異或門的邏輯功能

異或門(XOR gate)是數字邏輯電路中常用的一種邏輯門。它的作用是對兩個輸入信號進行邏輯運算,輸出一個結果。

異或門的真值表如下:

異或門的邏輯運算規則為:如果輸入的兩個信號不相同,則輸出為1;如果輸入的兩個信號相同,則輸出為0。

異或門可以使用不同的邏輯元件來實現,最常見的是使用電子元件,如晶體管或集成電路中的邏輯門芯片。在數字電路設計中,異或門被廣泛應用于數值計算、電信號處理、編碼解碼等領域。

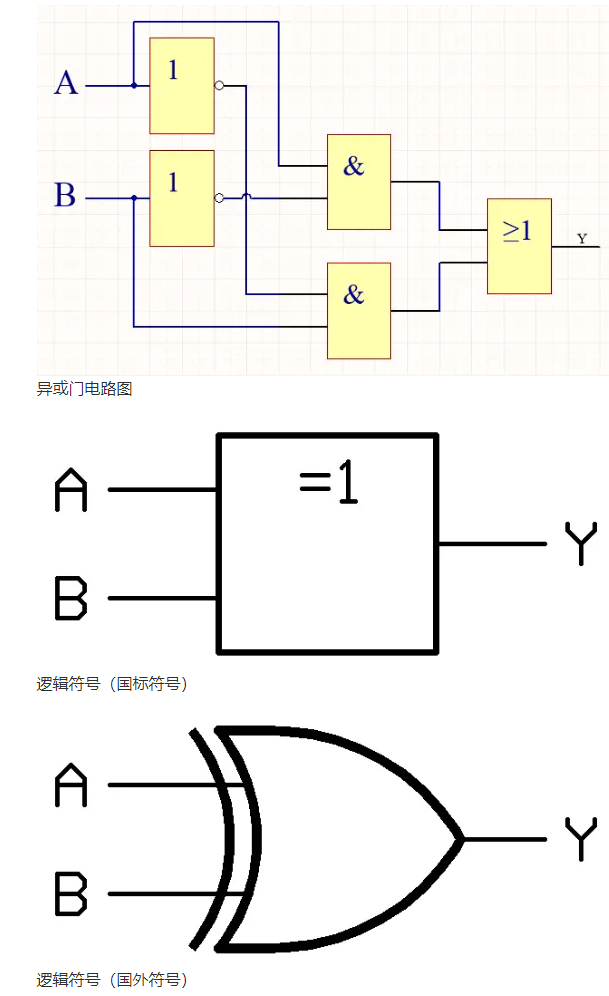

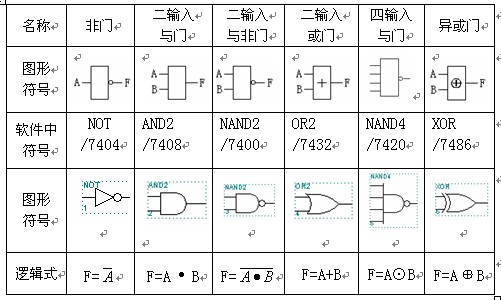

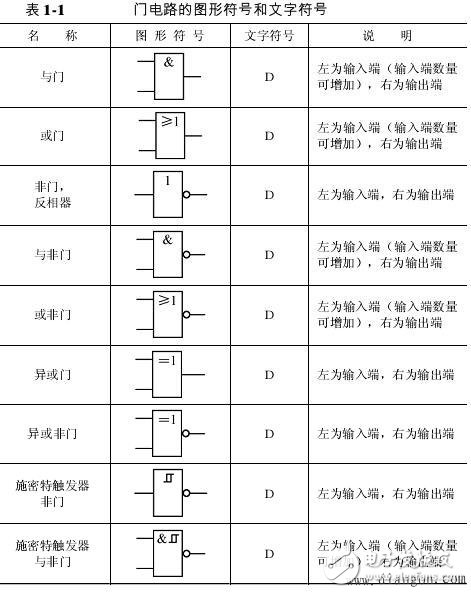

異或門的符號表示是一個帶有一個加號和一個圓圈的箭頭,如 ⊕。在電路圖中,我們常常用邏輯門符號表示異或門。

異或門的特點是在輸入的信號中只有一個為高電平(1)時,輸出才為高電平;當輸入的信號全為低電平(0)或全為高電平(1)時,輸出為低電平(0)。這種特性使得異或門在實際應用中能夠實現諸如二進制加法器、校驗和計算、數據傳輸等功能。

異或門是由哪些邏輯電路組成

異或門可以由幾種簡單的邏輯門組成,其中最常見的是使用與門(AND gate)、非門(NOT gate)和或門(OR gate)。

一種常見的實現異或門的方式是使用兩個與門、一個或門和一個非門。基于這種實現方式,可以按照以下步驟進行構建:

1. 將輸入信號 A 和 B 分別連接到兩個 AND 門的輸入端。

2. 將輸入信號 A 和 B 分別連接到一個 OR 門的輸入端。

3. 將兩個 AND 門的輸出信號分別連接到一個 OR 門的輸入端。

4. 將 OR 門的輸出信號連接到一個非門。

這樣構建的電路就是一個異或門,它可以根據輸入信號 A 和 B 的邏輯關系輸出相應的結果。

還有其他一些電路設計可以實現異或門,如使用 NAND 門和 NOR 門的組合,或者使用僅含有異或門的專用集成電路等。這些實現方式在邏輯功能上等效,只是使用不同的邏輯門組合。選擇哪種方式取決于具體的電路設計和應用需求。

審核編輯:黃飛

-

集成電路

+關注

關注

5387文章

11530瀏覽量

361633 -

晶體管

+關注

關注

77文章

9682瀏覽量

138080 -

異或門

+關注

關注

1文章

32瀏覽量

17796 -

數字邏輯電路

+關注

關注

0文章

106瀏覽量

15812

發布評論請先 登錄

相關推薦

組合邏輯電路和時序邏輯電路比較_組合邏輯電路和時序邏輯電路有什么區別

時序邏輯電路由什么組成_時序邏輯電路特點是什么

單片機邏輯電路運算符及邏輯電路符號資料下載

異或門的邏輯符號和邏輯電路組成

異或門的邏輯符號和邏輯電路組成

評論