什么是復位同步電路reset synchronizer?

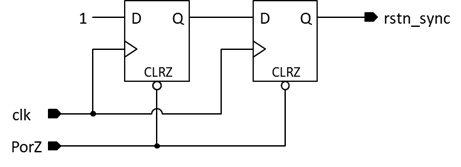

下圖是一個最簡單的復位同步電路。這個電路的輸出rstn_sync用作后續電路中D flip flop的復位信號。

這個電路的工作原理是:

-PorZ低電平,復位同步電路里的兩個D flip flop都被復位。電路的輸出rstn_sync為0,后續電路被復位。

-PorZ由低變高。clk上升沿到來時,第一個D flip flop先變1。過一個周期,第二個D flip flop變1,rstn_sync變1,后續電路離開復位狀態,開始正常工作。

-如果PorZ由低變高和clk上升沿離得很近,第一個D flip flop可能進入亞穩態(metastability)。不過沒關系,第二個D flip flop的輸出rstn_sync還是穩定的。復位同步電路的主要功能就是保障rstn_sync是穩定的0或1,在芯片的有生之年不發生亞穩態(或亞穩態的機率小到忽略不計)。同時,保障rstn_sync相對于clk有一個固定的時序關系。下面詳細討論。

為什么需要復位同步電路reset synchronizer?

這和D flip flop一個比較隱蔽的timing指標有關– removal/recovery time。D flip flop對時鐘沿active edge和復位的release edge是有時序要求的。通常,D flip flop復位端的release edge必須要滯后時鐘active edge一段時間(removal time),而且還要超前下一個時鐘active edge一段時間(recovery time)。如果有違例,那這個D flip flop就會進入亞穩態,在后仿中顯示為X。

復位同步電路reset synchronizer的輸出rstn_sync相對于時鐘clk有一個固定的時序關系。在PnR (place & route)中,工具構造buffer tree去buffer rstn_sync,并算出buffer后rstn_sync到后續每個D flip flop復位端的時間,通過插入或調整buffer,保障后續電路中每一個D flip flop的復位端都滿足removal/recovery要求。反之,如果rstn_sync相對于時鐘clk沒有有一個固定的關系,那工具就無從下手了,也就無法保障removal/recovery要求了。

順便說一下,綜合工具是不查removal/recovery time的。如果復位電路上有錯,通常會在設計流程很后面才發現,改起來代價也會高一些。所以一定要在一開始就重視復位電路。

為什么復位同步電路reset synchronizer自己不會進入亞穩態?

前面講了,第一級的D flip flop是有可能進入亞穩態。關鍵在于第二級。第二級的D輸入端在第一個clk到來的時刻仍是穩定的低電平(第一級的輸出此時尚未變成亞穩態X),第二級的的狀態不需要改變,仍舊保持原來復位后的0狀態。等到第二個clk到來的時候,如果第一級已經不在亞穩態了,第二級的D輸入就是一個穩定的1,那第二級的輸出rstn_sync自然就變成穩定的1了。即使第一級在第二個clk到來的時候沒有完全走出亞穩態,只要第一級的輸出不在中間值附近,第二級仍會把第一級的輸出當成0或1,第二級的輸出rstn_sync也就因此為穩定的0或1。這也就是為什么有時候復位同步電路reset synchronizer的latency是在1-3個時鐘之間。

有條件的同學,不妨跑一下Spectre sim,觀察一下D flip flop內部的信號,加深removal/recovery time的理解。眼見為實。

如果兩個D flip flop還不夠MTBF指標(發生亞穩態的概率仍不夠小),可以再加第三級。

有些標準元庫中有專門的同步電路,synchronizer cell。應該盡量使用這種synchronizer cell,比自己用兩個D flip flop搭更可靠。專門的synchronizer第二級是高增益的,大大降低第二級進入亞穩態的可能性。

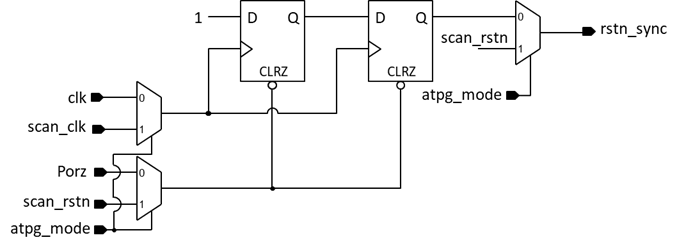

復位同步電路reset synchronizer能加到掃描鏈里嗎?

這里加了兩個MUX,這樣可以讓工具把同步復位電路的兩個D flip flop連到scan chain里,增加test coverage。

使用復位同步電路reset synchronizer需要注意的地方

一個復位同步電路reset synchronizer只能用到一個時鐘域。如果有幾個不同步的時鐘域,就要考慮使用多個復位同步電路。同步的時鐘域可以考慮復用一個復位同步電路reset synchronizer,但要做得仔細一些。

復位同步電路reset synchronizer有什么弊病嗎

復位同步電路reset synchronizer其實只在復位信號release的時候派上用場。復位結束后,這個電路其實就沒用了。但這個電路的時鐘還在switch,這個電路還在耗電。如果是高速時鐘,這個耗電就可觀了。低功耗設計,就要考慮是否可以關掉時鐘。這個根據不同場景,就非常復雜了,需要非常小心。

復位同步電路reset synchronizer是必須的嗎?

很多人通常不加思索一上來就加上同步復位電路reset synchronizer。這種條件反射本身是好習慣。

如果精益求精,那就要多思考一下了。有些場景是不需要復位同步電路reset synchronizer的。

復位的目的是讓電路有個明確的起始狀態。如果不需要明確的初始狀態,而且電路跑一段時間后能清除所有不確定狀態,進入正常狀態,那就可以考慮不用復位同步電路。例如FIR。如果使用場景中可以容忍初始輸出為垃圾,異步復位是可以的。

還有一個被99%的設計者忽略的場景。如果復位信號release的時候,時鐘還沒有啟動,那就根本不需要復位同步電路reset synchronizer。很多時候,芯片是內部oscillator, PLL提供時鐘的。而oscillator, PLL啟動都需要時間的。如果復位在這段時間內release,那就不需要同步復位電路reset synchronizer了。在低功耗設計中,尤其是多個內部時鐘域的場景,省下的功耗就可觀了。當然,設計要做得非常仔細。

還有一個場景就是內部產生的復位信號。做得精妙的設計,可以保證在內部復位release的時候沒有時鐘,也就不需要什么復位同步電路reset synchronizer了。內部產生復位信號是一個很有效的設計技巧。這個技巧復用現成的reset network同時將很多D flip flop清零,省去了在D flip flop的D輸入邏輯(D input logic cone)加上清零條件,可以節省很多門。

復位同步電路reset synchronizer在RTL里的實現

通常做成一個單獨的module,在主設計中例化這個module。

好了,希望復位同步講全面了。

審核編輯:黃飛

-

pll

+關注

關注

6文章

776瀏覽量

135130 -

復位電路

+關注

關注

13文章

322瀏覽量

44586 -

低電平

+關注

關注

1文章

115瀏覽量

13269 -

復位信號

+關注

關注

0文章

54瀏覽量

6314

發布評論請先 登錄

相關推薦

Xilinx FPGA異步復位同步釋放—同步后的復位該當作同步復位還是異步復位?

同步復位sync和異步復位async

同步復位和異步復位的比較(轉載)

HT66Fx0系列MCU的Reset復位電路應用介紹

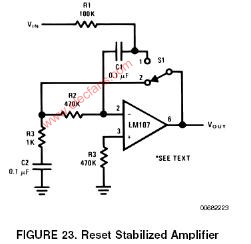

復位穩定放大器:The Reset Stabilized A

什么是復位同步電路 reset synchronizer?

什么是復位同步電路 reset synchronizer?

評論