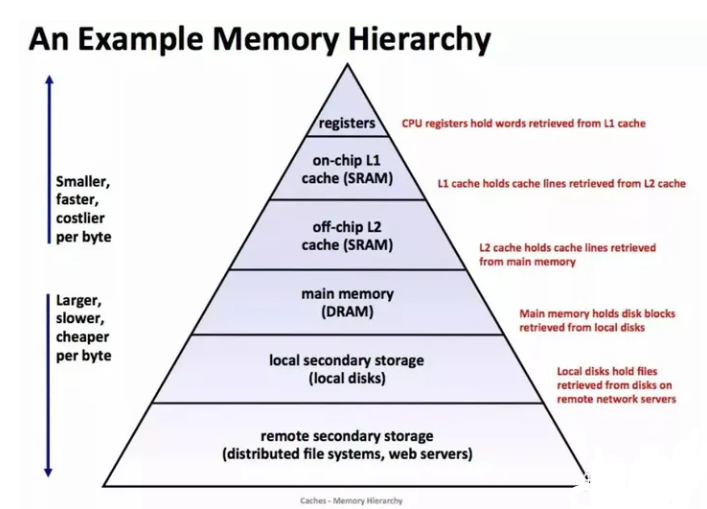

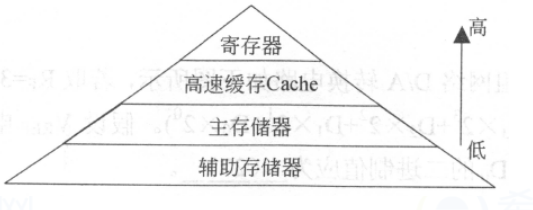

存儲器層次結構可以從圖片中清晰的看出來,圖片中共分為六級,越向上的層次,存儲器速度越快,容量更小,造價越高。

L0層為寄存器,寄存器從硬件的角度來說即觸發器( flip-flop ), 通常一個觸發器可以由兩個鎖存器( latcher )和邏輯塊組成,觸發器為邊沿有效,鎖存器為電平有效。寄存器集成在CPU內部,制作在CPU內的寄存器不可能容量太大,另一方面實際上CPU并不需要太多的寄存器,寄存器太多反而可能會減慢運行速度。目前的主流的片內寄存器數量為32個(或者64個?)。匯編語言中操作的寄存器也就是指的這些。寄存器由于在片內,避免了線延遲。

L1-L2為兩級高速緩存( cache ),這兩級存儲為SRAM,s即static,指靜態,最常見的SRAM為6T結構。高速緩存主要解決CPU計算速度和主存讀寫速度不匹配的問題,如果沒有這兩級,有關于內存的讀寫指令(如load和store)將會嚴重影響整體速度。高速緩存也一般集成在CPU上。目前主流CPU已經存在3級高速緩存。

L3為主存,即我們電腦中所謂的內存,為DRAM,d即dynamic,即動態,DRAM常見的有1T和3T結構,通過電容存儲信號,需要經常刷新不然電荷會漏光。DRAM速度要低于SRAM,但可以明顯看出1T只用了6T六分之一的晶體管,節省了六分之一的面積。

L4為磁盤內存,也就是我們所說的硬盤。以上的RAM都是掉電失去信息的,而硬盤中的內容掉電不會失去。目前機械硬盤主流的存儲技術為閃存flash,基于EEPROM。

L5層為遠端內存,比如網絡服務器,這些的讀寫速度主要取決于網絡延時。

為什么要采用這樣的分層結構呢?

采用存儲器層次結構的主要原因有以下幾點:

性能與成本的平衡:不同類型的存儲器在性能(如訪問速度)和成本(包括制造成本、功耗等)之間存在權衡。高速存儲器(如SRAM、Cache)訪問速度快,但制造成本高、容量小;而低速存儲器(如磁盤、DDR SDRAM)雖然訪問速度慢,但制造成本低、容量大。通過構建層次結構,可以充分利用各種存儲器的優勢,實現性能與成本的平衡。

局部性原理:程序在執行過程中通常會表現出時間局部性和空間局部性。時間局部性指的是程序在某一時刻訪問了某個數據后,在不久的將來還可能再次訪問該數據;空間局部性則指的是程序在某一時刻訪問了某個數據后,在不久的將來還可能訪問其附近的數據。利用這些局部性特性,可以在高速緩存中存放最近訪問過的數據和指令,從而提高訪問速度。

減少平均訪問時間:通過合理設計各級存儲器的容量和訪問速度,可以使得大部分數據訪問都在高速緩存或主存儲器中完成,從而顯著減少平均訪問時間。

管理復雜性:隨著技術的發展,存儲器的類型和容量都在不斷增加。采用層次結構可以簡化存儲器的管理復雜性,使得系統更容易擴展和升級。

采用存儲器層次結構是為了充分利用各種存儲器的優勢,實現性能與成本的平衡,同時利用程序的局部性特性來減少平均訪問時間,并簡化存儲器的管理復雜性。這也是現代計算機系統中廣泛采用存儲器層次結構的原因。

審核編輯:黃飛

-

DRAM

+關注

關注

40文章

2311瀏覽量

183446 -

存儲器

+關注

關注

38文章

7484瀏覽量

163764 -

cpu

+關注

關注

68文章

10854瀏覽量

211584 -

內存

+關注

關注

8文章

3019瀏覽量

74004 -

網絡服務器

+關注

關注

0文章

30瀏覽量

10890

發布評論請先 登錄

相關推薦

全面解析存儲器層次結構原理

存儲器的層次結構主要體現在什么地方?為什么要分這些層次?

MCP存儲器,MCP存儲器結構原理

高速緩沖存儲器基礎知識詳細介紹

存儲器層次結構如何解釋?

存儲器層次結構如何解釋?

評論