在Verilog中,Function和Task是用于模塊化設計和重用代碼的兩種重要元素。它們允許開發人員將復雜的操作分解為更小的功能單元,并在需要時調用它們。雖然Function和Task在某些方面非常相似,但它們在功能和使用方式上有一些重要的區別。

- 定義和聲明方式不同:

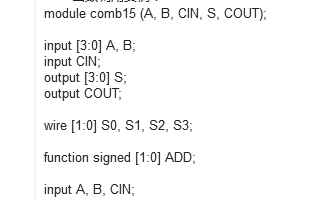

- Function:使用關鍵字"function"來定義和聲明。函數可以有一個或多個輸入參數,可以有一個返回值。函數必須在聲明之后直接定義,不能在其他函數或任務內部定義。

- Task:使用關鍵字"task"來定義和聲明。任務可以有一個或多個輸入參數,沒有返回值。與函數不同,任務可以在模塊的任何位置定義,也可以在其他函數或任務內部定義。

- 數據類型的使用:

- Function:函數可以接受和返回任何Verilog支持的數據類型。這些數據類型包括整數、浮點數、布爾值和自定義數據類型。函數可以將參數傳遞給其他函數或任務,并且可以在函數內部使用本地變量。

- Task:任務可以接受和返回任何Verilog支持的數據類型。任務也可以將參數傳遞給其他函數或任務。但是任務無法在內部定義本地變量。

- 返回值的處理方式不同:

- Function:函數必須通過"return"關鍵字返回一個值。函數的返回值可以直接賦值給其他變量,或者作為表達式的一部分使用。函數可以有多個返回語句,但只有在第一個返回語句時,函數的執行流程會跳到調用函數的位置。

- Task:任務沒有返回值,不需要"return"關鍵字。任務的執行流程會一直持續到最后一個語句執行完成,然后返回到調用任務的位置。

- 函數和任務的調用方式不同:

- Function:函數可以在任何地方被調用,包括組合邏輯和時序邏輯。函數可以在賦值語句、條件語句和循環語句中使用。函數的返回值可以直接賦值給變量,或者作為其他表達式的一部分使用。

- Task:任務只能在時序邏輯中被調用。任務的調用通常發生在"always"塊或"initial"塊內。在任務的調用語句后,任務中的所有語句會按照順序執行。任務不能在賦值語句等其他地方被使用。

- 并行和順序執行:

- Function:由于函數可以在任何位置被調用,它在代碼中可以并行執行。函數內的語句會根據調用順序依次執行,但在特定調用之間不會相互影響。

- Task:任務的語句按照順序執行。任務內的語句在調用任務時按照定義的順序被執行,并且不會并行執行。任務中的語句可以定義為組合邏輯或時序邏輯。

- 用途和場景不同:

- Function:函數主要用于進行計算、邏輯運算或數據處理。它們可以在Verilog模塊中廣泛使用,用于數值分析、數據轉換、狀態機控制等。

- Task:任務主要用于表示基本的行為或操作,例如時鐘信號的生成、觸發事件、輸出操作等。它們通常用于時序邏輯中,用于描述模塊的行為和操作。

總結起來,Function和Task在Verilog中具有不同的定義和聲明方式、數據類型的使用、返回值的處理方式、調用方式、并行與順序執行以及用途和場景。

聲明:本文內容及配圖由入駐作者撰寫或者入駐合作網站授權轉載。文章觀點僅代表作者本人,不代表電子發燒友網立場。文章及其配圖僅供工程師學習之用,如有內容侵權或者其他違規問題,請聯系本站處理。

舉報投訴

-

Verilog

+關注

關注

29文章

1367瀏覽量

112375 -

Function

+關注

關注

0文章

14瀏覽量

10127 -

函數

+關注

關注

3文章

4383瀏覽量

65039 -

模塊化

+關注

關注

0文章

341瀏覽量

22034

發布評論請先 登錄

相關推薦

熱點推薦

轉載---verilog中task和function的區別

;另外,function定義中聲明的所有局部變量寄存器都是靜態的,即function中的局部寄存器在function的多個調用之間保持他們的

發表于 03-13 21:53

煉獄傳奇-task_function之戰

1. task(任務)與function(函數)的不同任務與函數主要有以下四點不同:l函數只能與主模塊共用一個仿真時間單位,而任務定義自己的仿真時間單位。l函數不能啟動任務,任務可以啟動其他任務

發表于 05-13 11:19

Verilog函數中function里的過程語句該怎么寫

Verilog用函數方式描述一個4選1選擇器,function里的過程語句該怎么寫啊我這么寫報錯:functions can't contain non-blocking

發表于 04-17 06:35

Verilog的task和function說明語句

如果傳給任務的變量值和任務完成后接收結果的變量已定義, 就可以用一條語句啟動任務。任務完成以后控制就傳回啟動過程。如任務內部有定時控制, 則啟動的時回可以與控制返回的時

發表于 01-05 15:50

?13次下載

簡談FPGA verilog中的task用法

????????大家好,又到了每日學習的時間了,今天我們來聊一聊FPGA verilog中的task用法。 ? ? ? ?任務就是一段封裝在“task-endtask”之間的程序。任務

簡談FPGA verilog中的function用法與例子

大家好,又到了每日學習的時間了,今天我們來聊一聊FPGA verilog中的function用法與例子。 函數的功能和任務的功能類似,但二者還存在很大的不同。在 Verilog HDL

Verilog設計過程中的一些經驗與知識點

“ 本文主要分享了在Verilog設計過程中一些經驗與知識點,主要包括塊語句、阻塞賦值和非阻塞賦值 以及結構說明語句(initial, always, task, function)。”

verilog中的task用法

任務就是一段封裝在“task-endtask”之間的程序。任務是通過調用來執行的,而且只有在調用時才執行,如果定義了任務,但是在整個過程中都沒有調用它,那么這個任務是不會執行的。調用某個任務時可能

在Verilog中利用函數將重復性的行為級設計進行提取

在 Verilog 中,可以利用任務(關鍵字為 task)或函數(關鍵字為 function),將重復性的行為級設計進行提取,并在多個地方調用,來避免重復代碼的多次編寫,使代碼更加的簡

verilog同步和異步的區別 verilog阻塞賦值和非阻塞賦值的區別

Verilog中同步和異步的區別,以及阻塞賦值和非阻塞賦值的區別。 一、Verilog中同步和異

verilog function函數的用法

Verilog 是一種硬件描述語言 (HDL),主要用于描述數字電子電路的行為和結構。在 Verilog 中,函數 (Function) 是一種用于執行特定任務并返回一個值的可重用代碼

verilog task和function區別

verilog中的task和function都是用于實現模塊中的可重復的功能,并且可以接收參數和返回結果。但是它們在編寫和使用上有一些

verilog中initial和always的區別

Verilog是一種硬件描述語言(HDL),用于設計和模擬數字電路。在Verilog中,關鍵字initial和always都是用于描述電路行為的特殊語句。它們被用來生成仿真模型,并控制模擬器的啟動

評論