對于大多數模擬和混合信號數據采集系統設計工程師來說,設計無緩沖模數轉換器(ADC)的外部前端需要有耐心和大量建議,因為它常常被視為一種藝術形式,是經過多年摸索掌握其竅門的古怪大師的保留地。對于沒有經驗的人來說,這是一個令人沮喪的反復嘗試過程。大多數時候,由于相互關聯的規格要求很多,迫使設計人員不得不進行很多權衡(和評估)才能達到最佳效果。

1

挑戰

放大器級的設計由兩個彼此相關的不同級組成,因此問題變得難以在數學上建模,特別是因為有非線性因素與這兩級相關。第一步是選擇用來緩沖傳感器輸出并驅動ADC輸入的放大器。第二步是設計一個低通濾波器以降低輸入帶寬,從而最大限度地減少帶外噪聲。

理想的放大器是提供剛剛好的帶寬以正確緩沖傳感器或變送器產生的信號,而不會增加額外噪聲,并且功耗為零,但實際放大器與此相距甚遠。在大多數情況下,放大器規格將決定整體系統性能,尤其是在噪聲、失真和功耗方面。為了更好地弄清楚問題,第一步是了解離散時間ADC的工作原理。

離散時間ADC獲得連續時間模擬信號的樣本,然后將其轉換為數字碼。當信號被采樣時,根據模擬轉換器的類型,同一固有問題有兩種不同的情況。

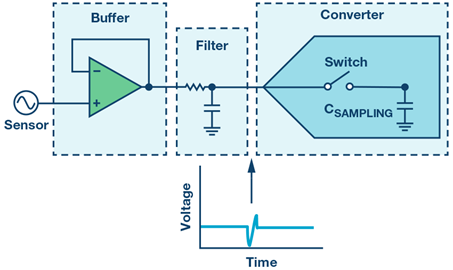

SARADC集成一個采樣保持器,其基本上由一個開關和一個電容組成,作用是保持模擬信號直到轉換完成,如圖1所示。

圖1. 采樣保持電路圖

離散時間∑-?ADC或過采樣轉換器實現了類似的輸入級,即具有一定內部電容的輸入開關。∑-?ADC的采樣機制略有不同,但采樣輸入架構類似,使用開關和電容來保持模擬輸入信號的副本。買元器件現貨上唯樣商城!

在這兩種情況下,開關都是用CMOS工藝實現,閉合時電阻為非零值,通常為幾歐姆。此串聯電阻與采樣電容(pF級)的組合,意味著ADC輸入帶寬常常非常大,在許多情況下要遠大于ADC采樣頻率。

2

帶寬問題

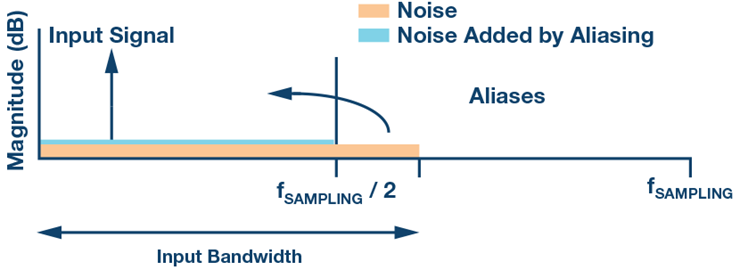

對轉換器來說,輸入信號帶寬是一個問題。在采樣理論中,我們知道高于奈奎斯特頻率(ADC采樣頻率的一半)的頻率信號應被移除,否則這些頻率信號將在目標頻帶中產生鏡像或混疊。通常,噪聲頻譜中有相當一部分功率存在于ADC奈奎斯特頻率以上的頻帶中。如果不處理這種噪聲,它將混疊到奈奎斯特頻率以下,增加本底噪聲(如圖2所示),使系統的動態范圍明顯降低。

圖2. 奈奎斯特折疊鏡像

ADC輸入信號帶寬,以及緩沖器輸出帶寬,是第一個要解決的問題。為確保噪聲不會向下混疊,必須限制ADC輸入信號的帶寬。這不是一個小問題。

通常,放大器的選擇是基于大信號帶寬(即壓擺率)和增益帶寬積的規格,以便應對輸入信號的極端情況,這決定了ADC可以跟蹤的最快變化的信號。

然而,放大器的有效噪聲帶寬等于小信號帶寬(通常針對小于10mVp-p的信號而考慮),這常常比大信號帶寬高出至少四到五倍。

換句話說,如果大信號規格是針對500kHz而選擇,那么小信號帶寬很容易就能達到2MHz或3MHz,這可能會導致ADC采集到大量噪聲。因此,在將模擬信號輸入ADC之前,應在外部限制小信號帶寬,否則測得的噪聲將是ADC數據手冊規格的三到四倍。

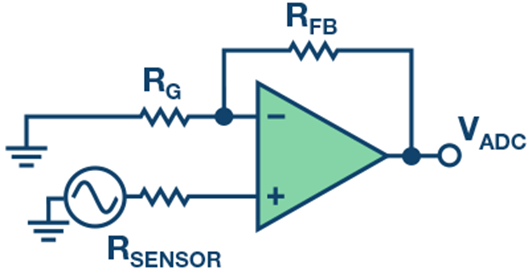

圖3. 同相放大器配置

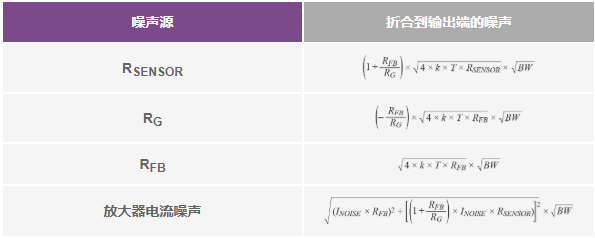

表1. 放大器折合到輸出端的噪聲,RTO

記住,放大器產生的熱噪聲取決于放大器增益和總系統帶寬。電路示例如圖3所示,噪聲源總結在表1中,其中:

T為溫度(單位為K),

k為玻爾茲曼常數(1.38×1023J/K),

電阻值單位為Ω,

BW指小信號帶寬。

以上公式表明,在ADC輸入引腳之前增加一個具有足夠衰減性能的低通濾波器以使采樣噪聲最小是很重要的,因為噪聲與帶寬的平方根成比例。通常,采用分立電阻和電容實現截止頻率足夠低的一階低通濾波器可消除大部分寬帶噪聲。一階低通濾波器還有一個額外的好處,即降低目標頻帶之外的任何其他較大信號的幅度,防止其被ADC采樣而可能產生混疊。

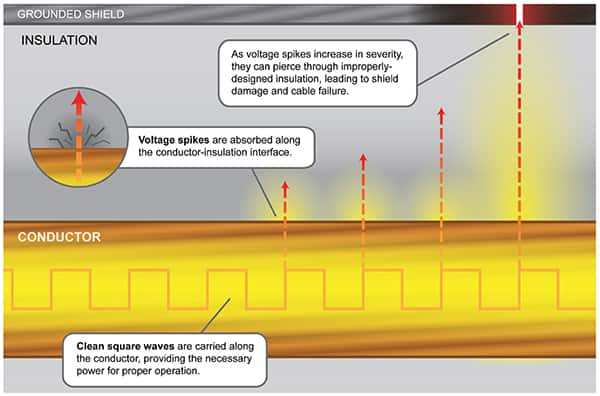

但是,這還沒完。ADC內部開關電阻和電容定義了模擬輸入帶寬,但由于輸入信號的變化,會產生時域充放電循環。每次開關(連接到采樣ADC電容的外部電路)閉合時,內部電容電壓可能與先前儲存在采樣電容上的電壓不同。

審核編輯 黃宇

-

ADI

+關注

關注

146文章

45819瀏覽量

249765 -

ADC驅動器

+關注

關注

0文章

35瀏覽量

13934

發布評論請先 登錄

相關推薦

驅動器的性能參數分析 驅動器的控制方式

Nexperia推出高性能柵極驅動器IC

如何提高伺服驅動器的效率

如何調試伺服驅動器

最大限度地提高GSPS ADC中的SFDR性能:雜散源和Mitigat方法

需要哪些輔助產品才能最大限度地發揮 VFD 和 VSD 的作用?- 第 1 部分

需要哪些支持產品才能最大限度地發揮 VFD 和 VSD 的作用?- 第 2 部分

利用TI GaN中的集成電流檢測功能更大限度提高系統效率

利用雙 MOSFET 最大限度地提高開關轉換器應用的功率密度和性能

伺服電機驅動器設置參數教程

用于并行采樣的EVADC同步轉換,如何在最大化采樣率的同時最大限度地減少抖動?

AD6645的底噪要做到什么程度才能最大限度的保證adc的有效位數?

Wi-SUN 可最大限度地提高太陽能跟蹤器的性能

ADI | 干貨!較大限度提高∑-? ADC驅動器的性能

ADI | 干貨!較大限度提高∑-? ADC驅動器的性能

評論