1、PCIe debug環(huán)境說明

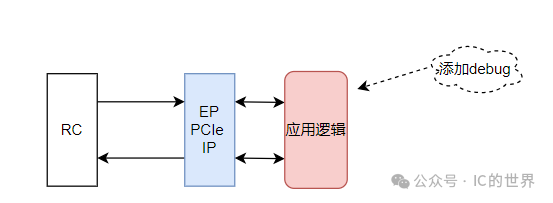

本文將以PCIe EP用戶邏輯舉例,描述PCIe可以添加哪些定位手段。

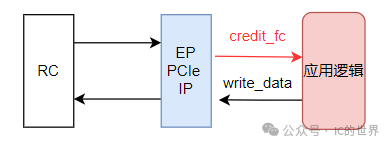

如圖所示,PCIe IP作為endpoint與RC對接,用戶實現(xiàn)了應用邏輯,與PCIe IP進行交互,交互信號中data格式為TLP報文格式,且交互信號包含相應的控制信號,例如PCIe配置空間和IP相干的配置信號。

常見的Debug設計可以通常有:中斷、鎖存狀態(tài)、統(tǒng)計計數(shù)和實時狀態(tài)。

添加Debug設計的目的通常是定位功能故障和性能故障。

功能故障通常有鏈路不通,出現(xiàn)錯包,PCIe部分 function無法訪問等等。

性能故障通常速率協(xié)商未到最高速率、傳輸速率不及預期等等。

添加debug手段可以在芯片調試時有效提高定位效率,快速發(fā)現(xiàn)并解決問題。

2.用戶需要添加的debug手段

2.1.最常見的統(tǒng)計計數(shù)

常見的統(tǒng)計技術有,發(fā)起的請求數(shù)量和收到的請求響應數(shù)量、正確的數(shù)量和錯誤的數(shù)量、單個function的統(tǒng)計以及所有function的統(tǒng)計。

已發(fā)起的dma read請求、已返回的dma read 響應。

已發(fā)起的dma write請求、已返回的dma write 響應。

已收到的memory space 訪問以及返回的memory space 響應。

2.2.ltssm 狀態(tài)機

記錄ltssm 協(xié)商過程,鎖存ltssm最近的若干次數(shù)值,便于分析ltssm協(xié)商過程。

ltssm 實時狀態(tài)可讀 統(tǒng)計ltssm進入L0狀態(tài)的次數(shù)和退出L0狀態(tài)的次數(shù)

2.3.PCIe 關鍵使能信號

PCIe IP關鍵信號包含vf/pf_bus_master_en、vf/pf_function_level_reset、hot reset、金手指復位perst,如下表格才采用英文簡寫描述。

如上的關鍵信號只有0和1兩種狀態(tài),都需要記錄實時狀態(tài)、統(tǒng)計0-->1跳變次數(shù)、統(tǒng)計1-->0跳變次數(shù)

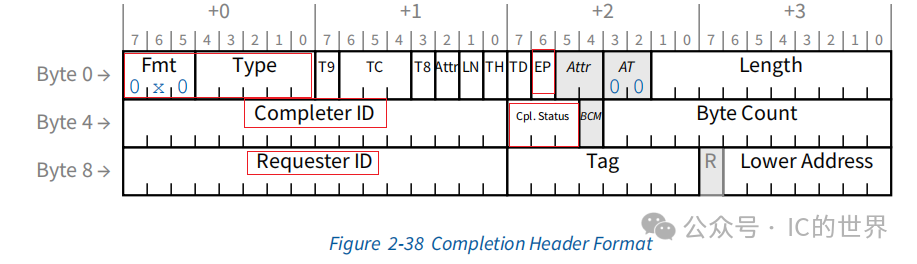

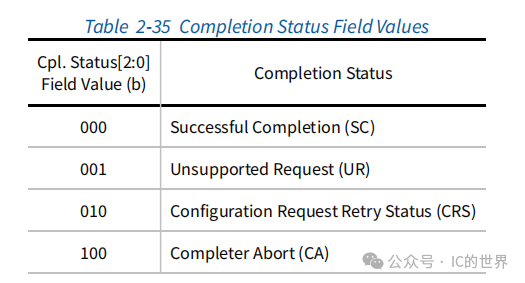

采用ram或者寄存器鎖存收到的cpl/cpld報文頭信息,可以根據(jù)需要選擇鎖存的字段,如下所示,強烈推薦鎖存Completion Status 、EP、Completer ID、Requester ID等信息方便問題定位。

2.5.異常請求debug

發(fā)現(xiàn)異常請求時記錄異常信息。 場景1:無效function的請求,例如當前PCIe只有128個VF,即VF0~VF127,結果收到了VF128的請求。此時需要鎖存請求類型、VF number以及產(chǎn)生錯誤中斷,方便問題定位。

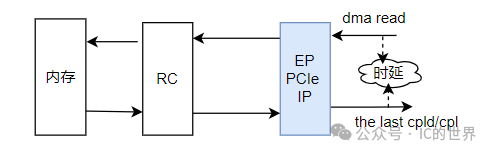

2.6.記錄cpld時延信息

為了便于計算性能,EP發(fā)起的memory 讀請求(俗稱dma read),需要統(tǒng)計時延,即從發(fā)起dma read請求開始到收到最后一個CPLD/CPL時消耗的時間,并且期望debug設計能夠記錄不同時延段位的dma read請求數(shù)量。debug設計可配置延時上限,一旦超時延時上限,則鎖存dma read請求信息,方便調試者定位。

2.7.統(tǒng)計流控信號

當應用邏輯寫數(shù)據(jù)速率過大或者RC端數(shù)據(jù)處理能力較弱時,RC反饋給EP的credit更新跟不上應用邏輯寫數(shù)據(jù)的速率,會導致EP對應用邏輯產(chǎn)生反壓,即credit_fc置1。此時將影響應用邏輯dma write的速率,通過觀察credit_fc的統(tǒng)計計數(shù)可以初步判斷影響性能的因素。

3.結束語

出現(xiàn)問題的原因可能是代碼bug,可能是配置的寄存器數(shù)值錯誤,也可能是配置順序流程不正確,添加debug設計就是為了能夠高效定位問題。本文僅僅簡單描述了部分需要添加的debug手段,歡迎大家留言補充。

審核編輯:劉清

-

寄存器

+關注

關注

31文章

5336瀏覽量

120230 -

鎖存器

+關注

關注

8文章

906瀏覽量

41496 -

PCIe

+關注

關注

15文章

1234瀏覽量

82582 -

TLP

+關注

關注

0文章

32瀏覽量

15625 -

CPLD芯片

+關注

關注

0文章

18瀏覽量

11628

原文標題:PCIE定位:PCIe需要的debug設計

文章出處:【微信號:IP與SoC設計,微信公眾號:IP與SoC設計】歡迎添加關注!文章轉載請注明出處。

發(fā)布評論請先 登錄

相關推薦

FPGA的PCIE接口應用需要注意哪些問題

PCIe可以添加哪些定位手段?PCIe需要的debug設計

PCIe可以添加哪些定位手段?PCIe需要的debug設計

評論