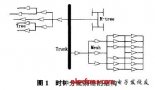

report_timing -path_type full_clock

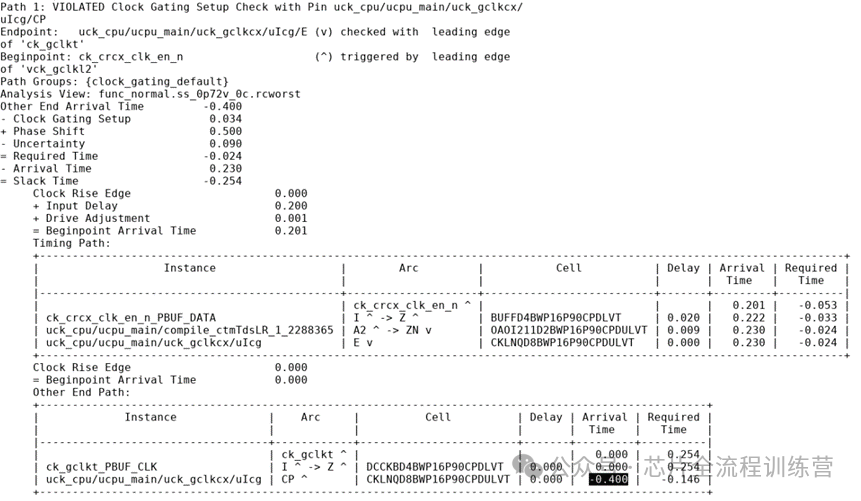

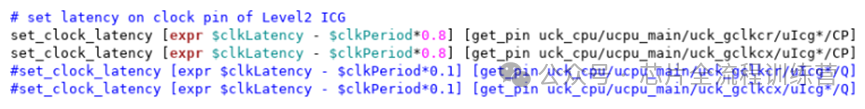

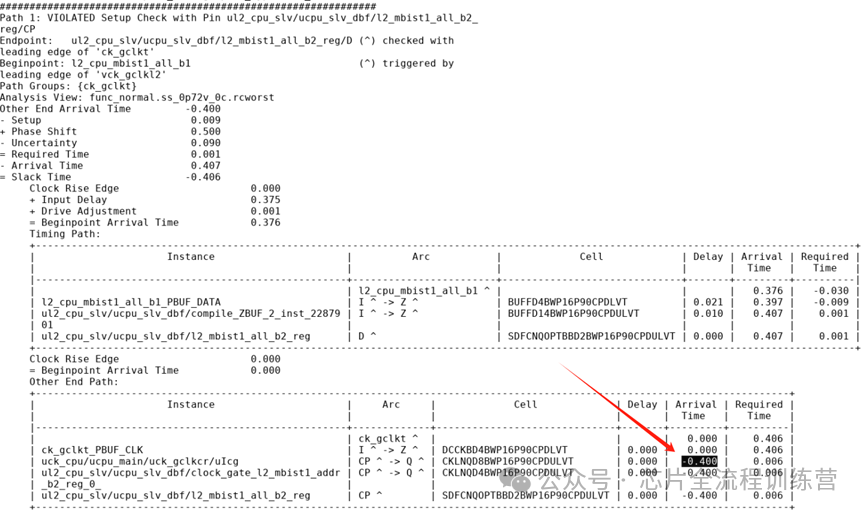

請問這里SDC為何約束到了ICG的CP端外,還約束了ICG的Q端?假設注釋掉Q端的約束,如下圖,會有什么問題?

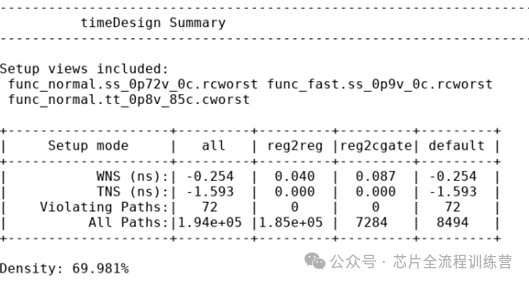

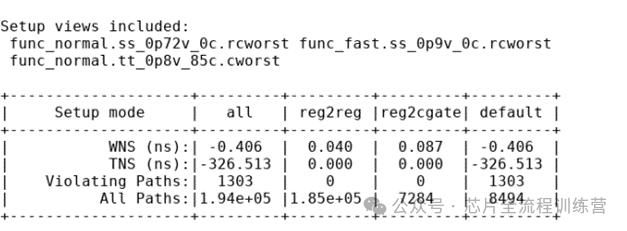

去掉后,timing報告如下,明顯setup timing變差了很多。

report_timing -path_type full_clock

因此,約束ICG的latency為-400ps,目的是把ICG從reg拉開400ps,如果不約束ICG的Q,那么工具為了minimize skew,會默認ICG后面所有的reg的CLK的latency和ICG是一樣的-400ps。此時,時鐘還是是理想的。因此需要給ICG的Q端也約束上latency,此處約束為-50ps。不經過這個ICG的CLK pin默認latency為0。

注意,ICG本身容易setupviolation,默認icg 和reg 越近越好。

“2.5GHz頻率,12nm工藝,DVFS低功耗A72后端培訓”

01

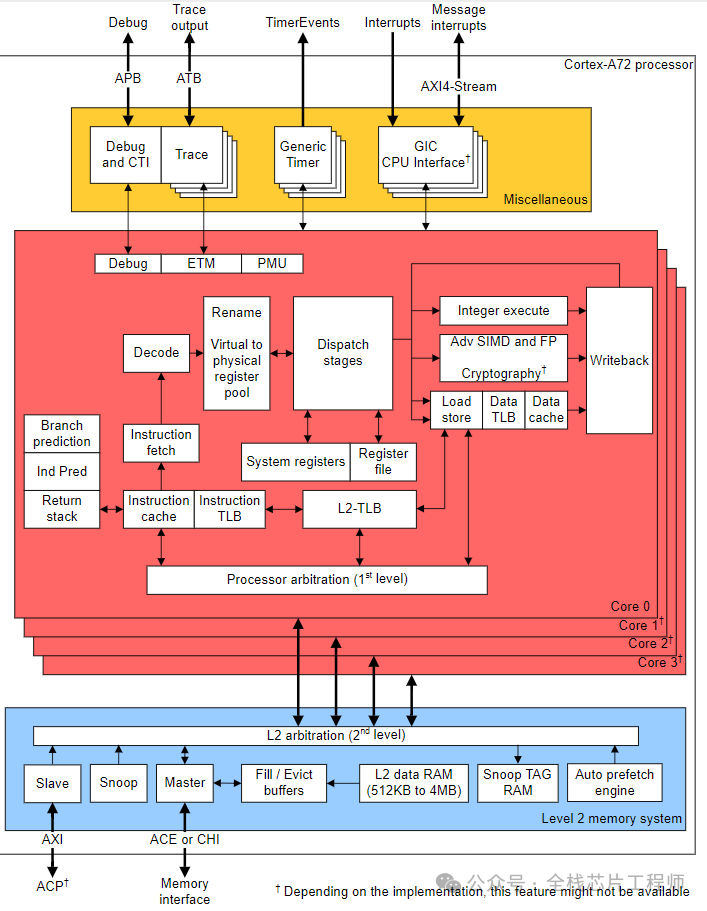

12nm Cortex-A72后端實戰

本項目是真實項目實戰培訓,低功耗UPF設計,后端參數如下:

工藝:12nm

頻率:2.5GHz

資源:2000_0000instances

低功耗:DVFS

為了滿足廣大學員的訴求,我們將12nm A72 TOP課程分為兩個版本:

1、基礎版(價格是知名機構的1/5,全國最低價)

2、進階版(低功耗、hierarchy UPF、Stampling)!業界最先進技術!

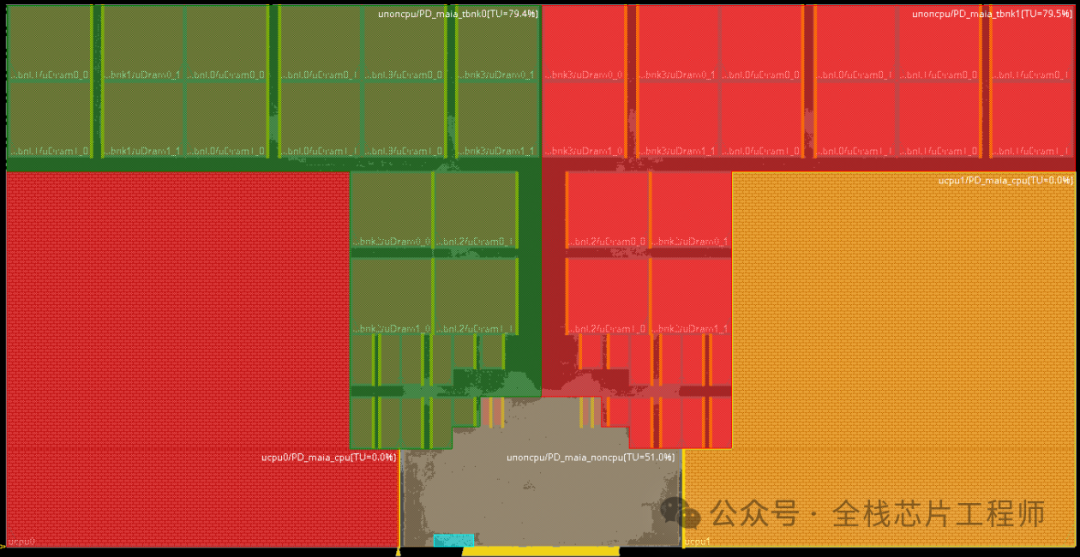

進階版本的低功耗設計如下:7個power domain

Stampling打起來真是高級手工藝術,全網唯一:

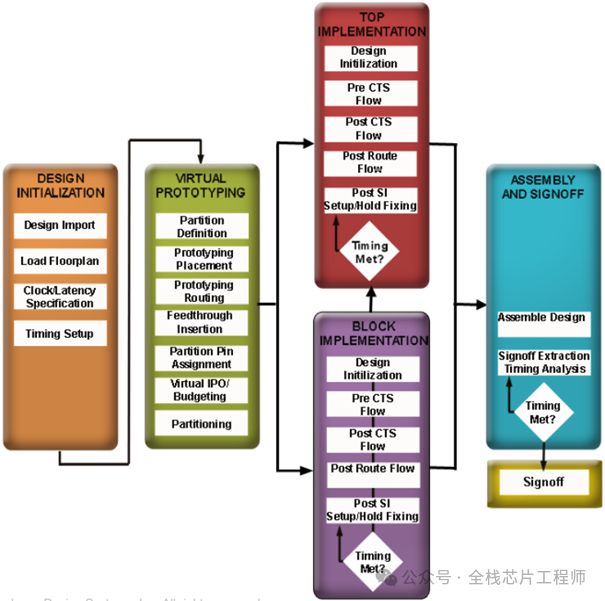

Flow:PartitionFlow

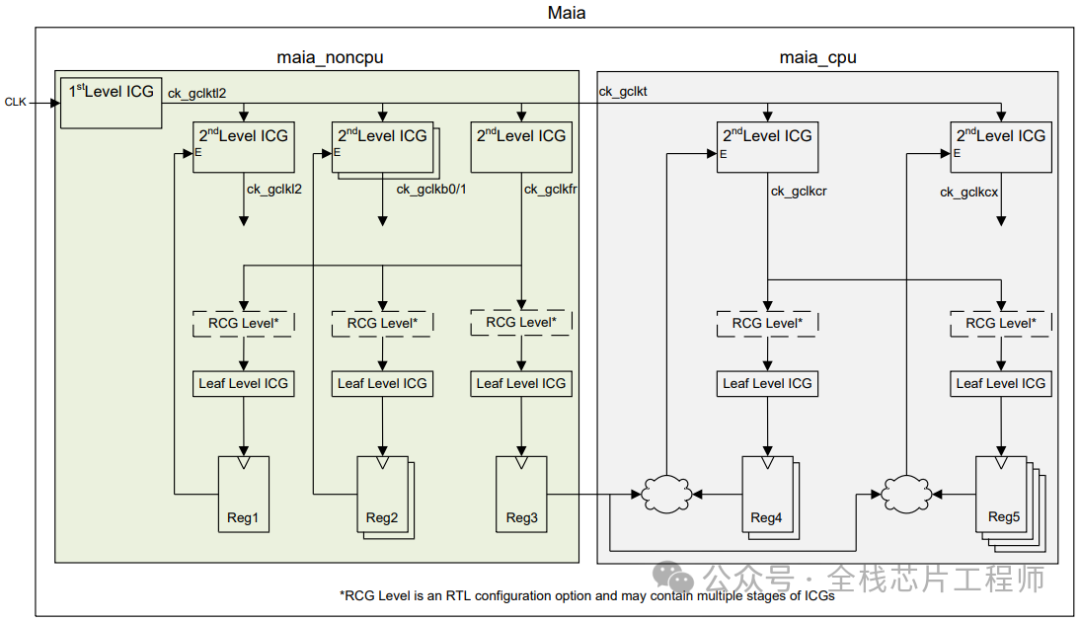

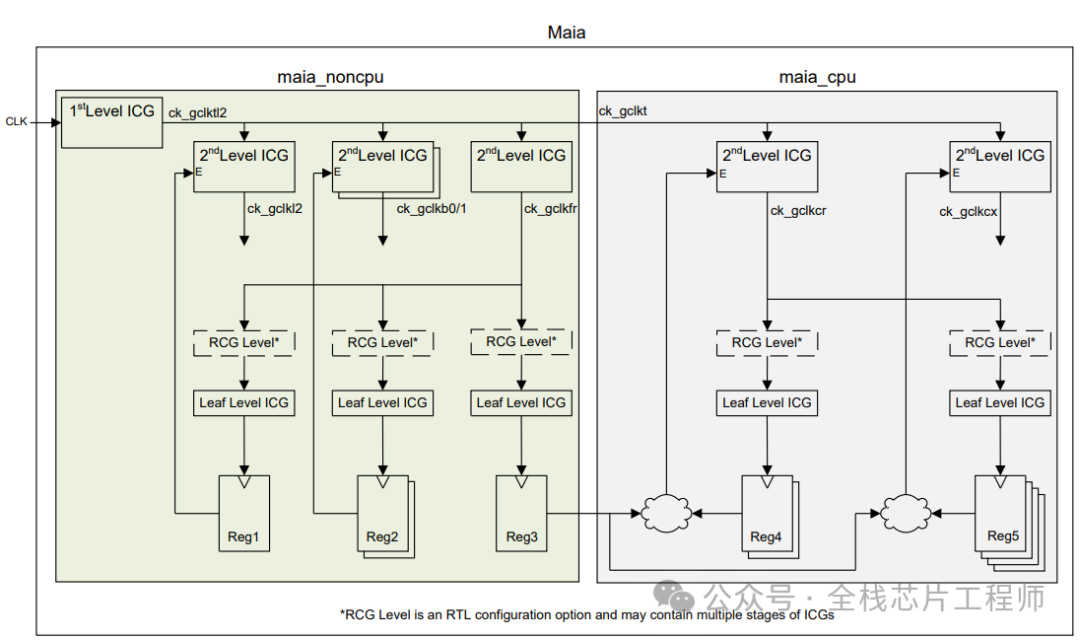

時鐘結構分析:

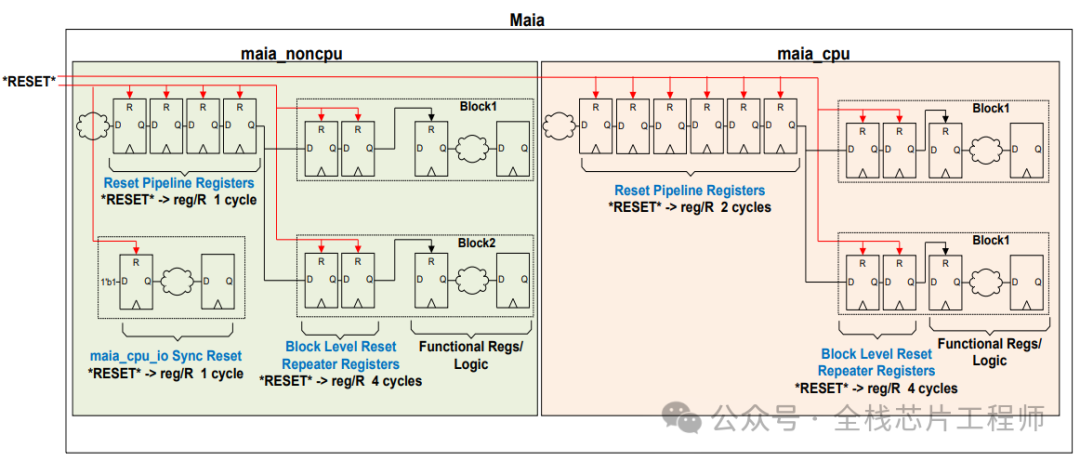

復位結構分析:

12nm 2.5GHz的A72實戰訓練營需要特別設置Latency,TOP結構如下,參加過景芯SoC全流程訓練營的同學都知道CRG部分我們會手動例化ICG來控制時鐘,具體實現參見40nm景芯SoC全流程訓練項目,本文介紹下12nm 2.5GHz的A72實戰訓練營的Latency背景,歡迎加入實戰。

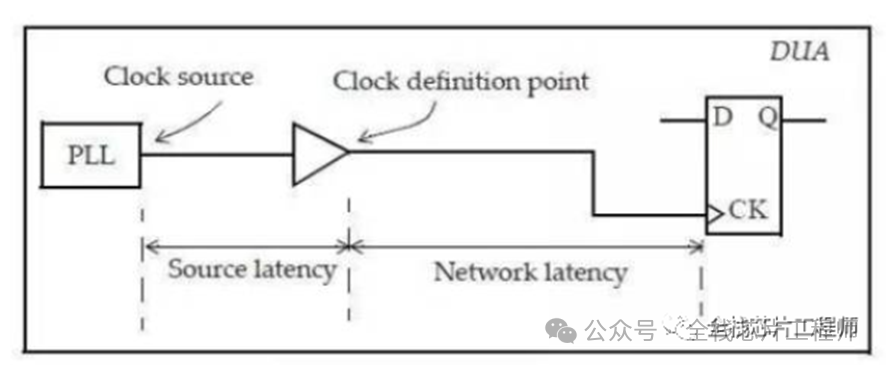

時鐘傳播延遲Latency,通常也被稱為插入延遲(insertion delay)。它可以分為兩個部分,時鐘源插入延遲(source latency)和時鐘網絡延遲(Network latency)。

大部分訓練營同學表示平時都直接將Latency設置為0了,那latency值有什么用呢?其實這相當于一個target值,CTS的engine會根據你設置的latency值來插入buffer來實現你的latency target值。

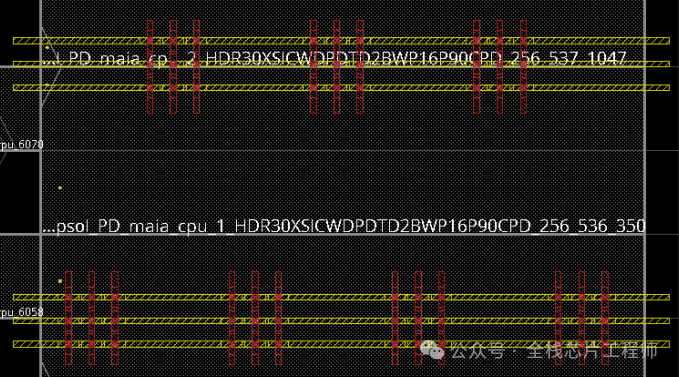

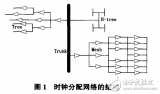

下圖分為1st Level ICG和2nd Level ICG,請問這些ICG為什么要分為兩層?

請問,為什么不全部把Latency設置為0?2nd Level ICG的latency應該設置為多少呢?

latency大小直接影響clock skew的計算。時鐘樹是以平衡為目的,假設對一個root和sink設置了400ps的latency值,那么對另外的sink而言,就算沒有給定latency值,CTS為了得到較小的skew,也會將另外的sink做成400ps的latency。請問,為何要做短時鐘樹?因為過大的latency值會受到OCV和PVT等因素的影響較大,并有time derate的存在。

審核編輯:黃飛

-

cpu

+關注

關注

68文章

10878瀏覽量

212168

原文標題:高性能CPU的ICG Latency設置

文章出處:【微信號:全棧芯片工程師,微信公眾號:全棧芯片工程師】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

CPU和GPU頻率的查看及設置

AutoKernel高性能算子自動優化工具

怎樣去設置電腦電源的高性能模式呢

怎么把電源計劃設置為高性能呢

《現代CPU性能分析與優化》---精簡的優化書

《現代CPU性能分析與優化》--讀書心得筆記

Linux CPU的性能應該如何優化

CPU與內存延遲的關系分析 影響CPU性能差距的因素

突破性能瓶頸,實現CPU與內存高性能互連

CPU程序幾個優化程序性能的手段詳解

優化高性能CPU的ICG延遲設置

優化高性能CPU的ICG延遲設置

評論