氮化鎵(GaN)場(chǎng)效應(yīng)晶體管已經(jīng)徹底改變了電力電子行業(yè),具有比傳統(tǒng)硅MOSFETs更小的尺寸、更快的開(kāi)關(guān)速度、更高的效率和更低的成本等優(yōu)勢(shì)。然而,GaN技術(shù)的快速發(fā)展有時(shí)超過(guò)了專(zhuān)用GaN專(zhuān)用柵極驅(qū)動(dòng)器和控制器的發(fā)展。因此,電路設(shè)計(jì)人員經(jīng)常求助于為硅MOSFETs設(shè)計(jì)的通用柵極驅(qū)動(dòng)器,從而需要仔細(xì)考慮各種因素以獲得最佳性能。

GaN晶體管與Si MOSFETs

與硅MOSFETs相比,eGaN FETs表現(xiàn)出不同的特性,影響其與專(zhuān)為后者設(shè)計(jì)的柵極驅(qū)動(dòng)器一起工作。一些主要差異包括:

較低的柵極電壓水平:eGaN FETs要求導(dǎo)通時(shí)的柵極電壓為5 V,關(guān)斷時(shí)的柵極電壓為0 V,最大柵極額定值為6 V,這使得驅(qū)動(dòng)?xùn)艠O驅(qū)動(dòng)器的電源必須進(jìn)行相應(yīng)設(shè)計(jì)。驅(qū)動(dòng)器或控制器的欠壓閉鎖(UVLO)也應(yīng)與5 V柵極驅(qū)動(dòng)對(duì)齊。

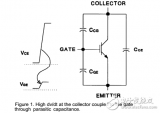

更快的開(kāi)關(guān)速度:Si MOSFETs的RDS(on)QG可能是GaN的3倍以上,RDS(on)QGD高達(dá)10倍。因此,開(kāi)關(guān)節(jié)點(diǎn)上可能存在75 V/ns或更高的dv/dt,因此柵極驅(qū)動(dòng)器需要不受這種壓擺率的影響。更快的開(kāi)關(guān)速度也會(huì)使寄生電感更加明顯,因此設(shè)計(jì)中需要采用低電感布局技術(shù)。

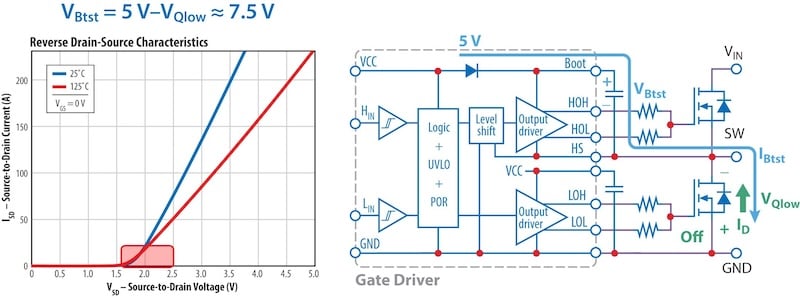

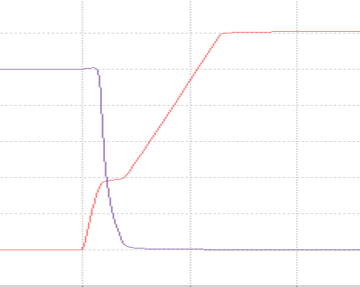

更高的反向?qū)▔航?與硅MOSFET不同,eGaN FETs沒(méi)有寄生體二極管,但它們以更大的壓降反向傳導(dǎo)電流,與MOSFET的1 V相比約為2.5 V,這意味著柵極驅(qū)動(dòng)器在整流開(kāi)關(guān)的死區(qū)時(shí)間內(nèi)可以看到更高的負(fù)開(kāi)關(guān)節(jié)點(diǎn)電壓。因此,柵極驅(qū)動(dòng)器應(yīng)包括自舉過(guò)壓管理,并且能夠在低至-5 V的負(fù)開(kāi)關(guān)節(jié)點(diǎn)電壓下工作。

物理結(jié)構(gòu):eGaN FETs具有橫向結(jié)構(gòu),而額定電壓》20 V的Si MOSFETs通常是垂直器件。因此,引腳位置可能不同,使用Si MOSFET專(zhuān)用柵極驅(qū)動(dòng)器時(shí)會(huì)帶來(lái)布局挑戰(zhàn)。GaN專(zhuān)用柵極驅(qū)動(dòng)器設(shè)計(jì)為與大多數(shù)GaN晶體管布局兼容。將MOSFET驅(qū)動(dòng)器用于GaN FET時(shí)的布局沖突要求理解設(shè)計(jì)中可能做出的權(quán)衡。

MOSFET柵極驅(qū)動(dòng)器兼容性審查

在設(shè)計(jì)驅(qū)動(dòng)GaN FETs的MOSFET柵極驅(qū)動(dòng)器之前,它必須滿(mǎn)足某些要求。

與5 V電源兼容:柵極驅(qū)動(dòng)器必須與驅(qū)動(dòng)級(jí)的5 V電源兼容,無(wú)論是外部穩(wěn)壓電源還是內(nèi)部低壓差穩(wěn)壓器(LDO)。

欠壓鎖定兼容性:UVLO必須與5 V驅(qū)動(dòng)器級(jí)兼容。低端驅(qū)動(dòng)器級(jí)的典型UVLO介于3.75–4V和高端的3.25 - 3.75 V之間。

壓擺率抗擾度:柵極驅(qū)動(dòng)器應(yīng)表現(xiàn)出超過(guò)開(kāi)關(guān)節(jié)點(diǎn)最大預(yù)期dv/dt的壓擺率抗擾度,最好大于50 kV/ s,如果無(wú)法滿(mǎn)足這一要求,可能需要以降低轉(zhuǎn)換器效率為代價(jià)降低開(kāi)關(guān)速度。

自舉電源:許多MOSFET驅(qū)動(dòng)器使用自舉電路為上層器件驅(qū)動(dòng)器供電,大多數(shù)驅(qū)動(dòng)器使用自舉二極管。只有使用外部自舉二極管的柵極驅(qū)動(dòng)器才適合與GaN FETs一起使用,這一點(diǎn)在建議中會(huì)很明顯。內(nèi)置LDO后置自舉二極管的驅(qū)動(dòng)器是首選。

死區(qū)能力:eGaN FETs出色的開(kāi)關(guān)特性支持MHz范圍內(nèi)的工作條件,同時(shí)保持較高的轉(zhuǎn)換器效率。因此,盡可能縮短死區(qū)時(shí)間(甚至低于10 ns)非常有益。一些為MOSFETs設(shè)計(jì)的控制器無(wú)法實(shí)現(xiàn)如此低的死區(qū)時(shí)間,從而抵消了GaN器件的優(yōu)勢(shì)。考慮使用GaN FETs的控制器時(shí),優(yōu)先考慮具有低死區(qū)功能的控制器。

轉(zhuǎn)換MOSFET驅(qū)動(dòng)器以使用GaN FETs

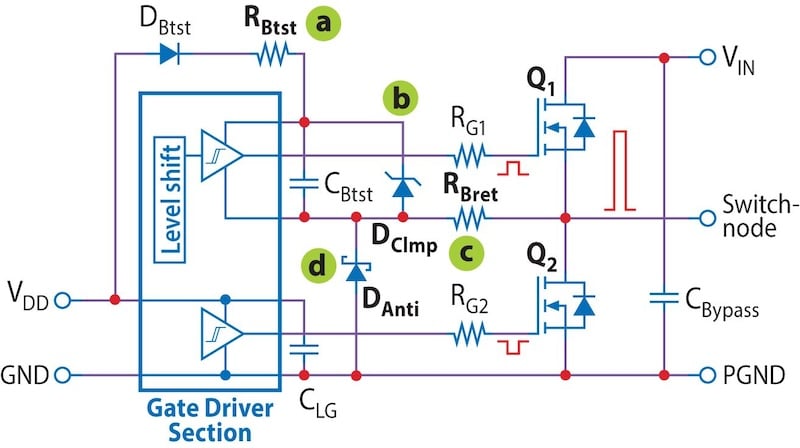

確定兼容的MOSFET驅(qū)動(dòng)器后,可以實(shí)施以下步驟來(lái)確保與GaN FETs的最高兼容性。請(qǐng)參考圖1了解詳細(xì)信息以及附帶的解釋。除這些建議外,還應(yīng)始終遵循通用GaN FET驅(qū)動(dòng)建議。

自舉二極管:用于外部自舉二極管,使用尺寸、電容和額定電流盡可能小的肖特基二極管,如BAT54KFILM,并將其與限流電阻串聯(lián),如圖1(a)所示。這肖特基二極管確保最低的電壓損失(V噓電視節(jié)目鹽水),使驅(qū)動(dòng)器電壓盡可能接近5 V。當(dāng)任何保護(hù)電路啟動(dòng)時(shí),小串聯(lián)電阻會(huì)限制自舉二極管中的電流。應(yīng)當(dāng)注意,該電阻可能會(huì)影響自舉電容再充電所需的最小脈沖寬度。自舉二極管后集成5 V LDO的驅(qū)動(dòng)器不需要串聯(lián)電阻或隨后介紹的額外電路保護(hù),因?yàn)檫@些建議已變?yōu)榭蛇x。

自舉箝位:自舉電容兩端的齊納二極管可以將電壓箝位在6 V以下,以防止低端器件反向?qū)〞r(shí)的死區(qū)期間過(guò)壓。齊納電壓為5.6 V的MM5Z5V6ST1G就是一個(gè)很好的例子,如圖1(b)所示。自舉電容和齊納二極管應(yīng)盡可能靠近彼此放置,并盡可能靠近柵極驅(qū)動(dòng)器。

柵極返回電阻:如圖1(c)所示,在低端GaN FET反向?qū)ㄆ陂g,為高端FET增加一個(gè)柵極返回電阻可以保護(hù)IC免受開(kāi)關(guān)節(jié)點(diǎn)上較大負(fù)電壓的影響,如圖2所示。該電阻值還取決于上部器件門(mén)電路所需的關(guān)斷阻尼和時(shí)序。使用該電阻要求柵極的導(dǎo)通電阻等效降低,以補(bǔ)償其電阻。

圖1(a-d)。

推薦用于GaN FET兼容性的Si柵極驅(qū)動(dòng)器增強(qiáng)。圖片由提供

博多的電力系統(tǒng)

[PDF]

4.反向?qū)槲?如圖1(d)所示,一個(gè)反并聯(lián)肖特基二極管跨接在半橋拓?fù)涞牡投耍梢韵拗乞?qū)動(dòng)器承受的負(fù)開(kāi)關(guān)節(jié)點(diǎn)電壓的幅度。當(dāng)開(kāi)關(guān)節(jié)點(diǎn)降至低于參考地的特定電壓以下時(shí),一些柵極驅(qū)動(dòng)器變得敏感或甚至可能失效。該二極管的額定電壓應(yīng)與低端GaN FET的額定電壓相匹配。額定電流可能顯著低于低端FET,因?yàn)樗鼉H在空載時(shí)間導(dǎo)通,因此應(yīng)根據(jù)其額定脈沖電流進(jìn)行選擇。

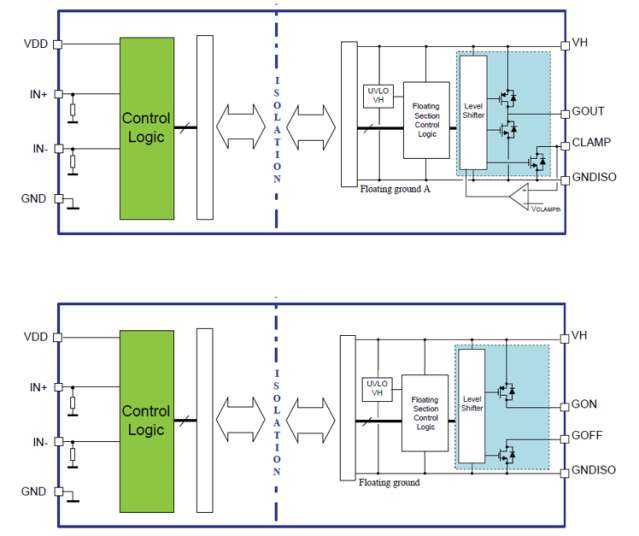

控制器IC和集成柵極驅(qū)動(dòng)器

控制器IC將許多功能集成到單個(gè)IC中,包括柵極驅(qū)動(dòng)器。其中一些IC可能不支持GaN器件的最佳布局,因此了解設(shè)計(jì)折衷以實(shí)現(xiàn)最佳性能非常重要。

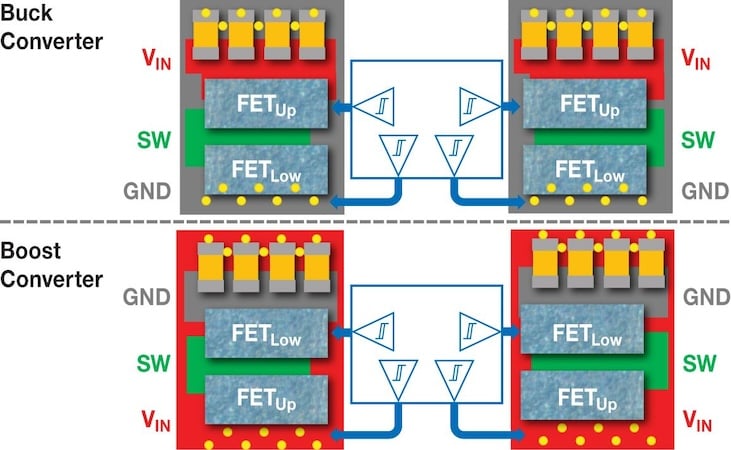

使用GaN FETs設(shè)計(jì)功率級(jí)時(shí),務(wù)必遵循一般布局建議。考慮的順序仍然是共源電感(CSI),然后是電源和柵極環(huán)路電感。這意味著功率級(jí)基本上設(shè)計(jì)成一個(gè)模塊,柵極信號(hào)連接到控制器IC,如圖3所示。功率級(jí)模塊建議布局的變化有助于選擇適合控制器IC的最佳模塊。在2相控制器的情況下,可能需要在兩種可選設(shè)計(jì)之間進(jìn)行選擇。設(shè)計(jì)標(biāo)準(zhǔn)是將通常為硬開(kāi)關(guān)的控制FET(開(kāi)關(guān))置于同步整流器之上。例如,在降壓轉(zhuǎn)換器中,應(yīng)優(yōu)化布局,使高端FET柵極環(huán)路中的寄生電感最小。對(duì)于中的低端FET也是如此升壓轉(zhuǎn)換器如圖3所示。

圖二。

死區(qū)時(shí)間內(nèi)的自舉充電路徑。圖片由提供者使用

博多的電力系統(tǒng)

[PDF]

圖3。

推薦布局。圖片由提供者使用

博多的電力系統(tǒng)

[PDF]

調(diào)整MOSFET柵極驅(qū)動(dòng)器以用于GaN FETs

為了使MOSFET柵極驅(qū)動(dòng)器適用于GaN FETs,設(shè)計(jì)人員必須確保兼容性,實(shí)施建議的修改,并優(yōu)化布局以充分發(fā)揮的潛力氮化鎵技術(shù)。仔細(xì)關(guān)注這些指南,設(shè)計(jì)人員可以使用通用柵極驅(qū)動(dòng)器和控制器,為成功大規(guī)模生產(chǎn)鋪平道路GaN基功率轉(zhuǎn)換器.

審核編輯 黃宇

-

MOSFET

+關(guān)注

關(guān)注

150文章

8514瀏覽量

219974 -

控制器

+關(guān)注

關(guān)注

114文章

17072瀏覽量

183910 -

晶體管

+關(guān)注

關(guān)注

77文章

10009瀏覽量

141405 -

柵極驅(qū)動(dòng)器

+關(guān)注

關(guān)注

8文章

1076瀏覽量

39644 -

GaN FET

+關(guān)注

關(guān)注

0文章

12瀏覽量

3833

發(fā)布評(píng)論請(qǐng)先 登錄

最實(shí)用的柵極驅(qū)動(dòng)芯片選型指南

為什么我們需要#mosfet柵極驅(qū)動(dòng)器?

高速柵極驅(qū)動(dòng)器助力實(shí)現(xiàn)更高系統(tǒng)效率

柵極驅(qū)動(dòng)器是什么

柵極驅(qū)動(dòng)器是什么,為何需要柵極驅(qū)動(dòng)器?

如何利用氮化鎵實(shí)現(xiàn)高性能柵極驅(qū)動(dòng)?

使用MOSFET柵極驅(qū)動(dòng)器的IGBT驅(qū)動(dòng)器

ADI隔離柵極驅(qū)動(dòng)器和WOLFSPEED SiC MOSFET

用于SiC MOSFET的柵極驅(qū)動(dòng)器

用于電機(jī)驅(qū)動(dòng)的MOSFET驅(qū)動(dòng)器

隔離式柵極驅(qū)動(dòng)器的演變(IGBT/SiC/GaN)

適配MOSFET柵極驅(qū)動(dòng)器以驅(qū)動(dòng)GaN FETs

評(píng)論