Versal 介紹

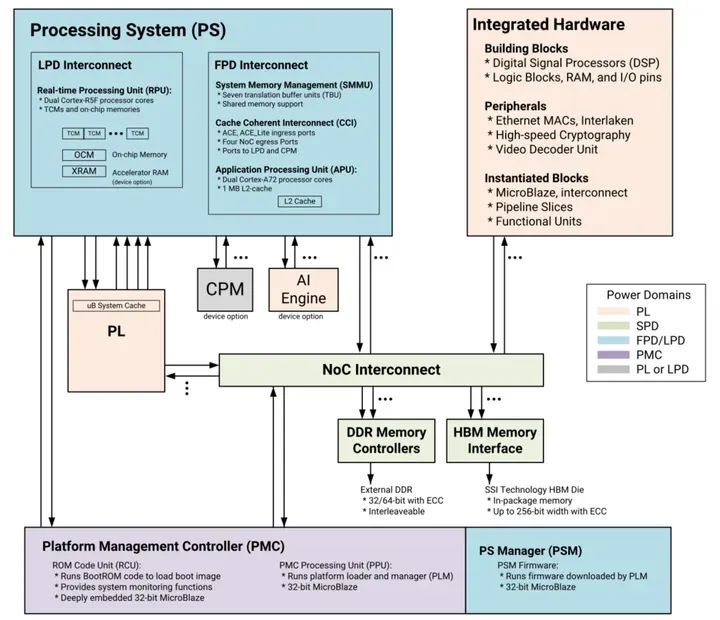

Versal 包含了 Cortex-A72 處理器和 Cortex-R5 處理器,PL 端可編程邏輯部分,PMC 平臺管理控制器,AI Engine 等模塊,與以往的 ZYNQ 7000 和 MPSoC 不同,Versal 內(nèi)部是通過 NoC 片上網(wǎng)絡(luò)進(jìn)行互聯(lián)。

Versal 芯片的總體框圖

Versal 芯片的總體框圖

PS: 處理系統(tǒng) (Processing System) , 就是與 FPGA 無關(guān)的 ARM 的 SoC 的部分。

PL: 可編程邏輯 (Progarmmable Logic), 就是 FPGA 部分。

NoC 架構(gòu)

Versal 可編程片上網(wǎng)絡(luò)(NoC) 是一種 AXI 互連網(wǎng)絡(luò),用于在可編程邏輯 PL,處理器系統(tǒng) PS 等之間共享數(shù)據(jù),而之前的 Versal 系列采用的 AXI 交叉互聯(lián)模塊,這是 Versal 的不同之處。

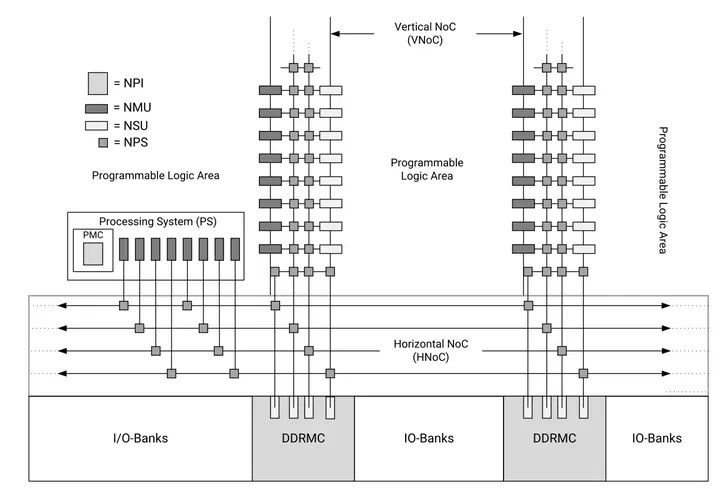

NoC 是為可擴(kuò)展性而設(shè)計(jì)的。它由一系列相互連接的水平(HNoC)和垂直(VNoC)路徑,由一組可定制的硬件實(shí)現(xiàn)組件支持,這些組件可以以不同的方式進(jìn)行配置,以滿足設(shè)計(jì)時(shí)序、速度和邏輯利用率要求。以下是 NoC 的結(jié)構(gòu)圖

NoC 的結(jié)構(gòu)圖

從 NoC 的結(jié)構(gòu)圖,可以看到,其主要由 NMU(NoC master units),NSU(NoC slave units),NPI(NoC programming interface),NPS(NoC packet switch)組成。PS 端可以連接到 NMU,再通過 NPS 連接訪問到 DDRMC,同樣 PL 端也可以通過 NMU,NPS 訪問到 DDRMC。通過 NPS 路由的方式,靈活地訪問各模塊。

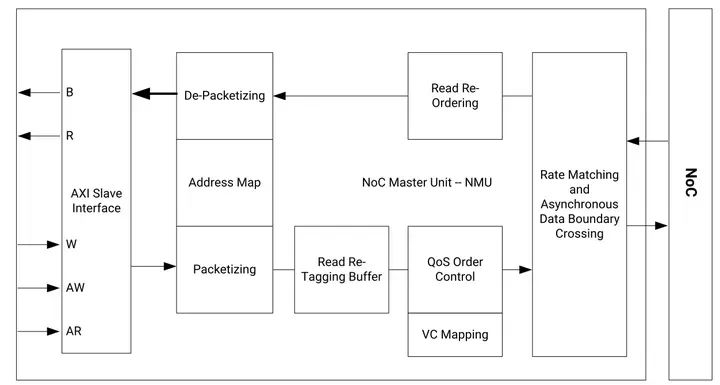

NMU 結(jié)構(gòu)

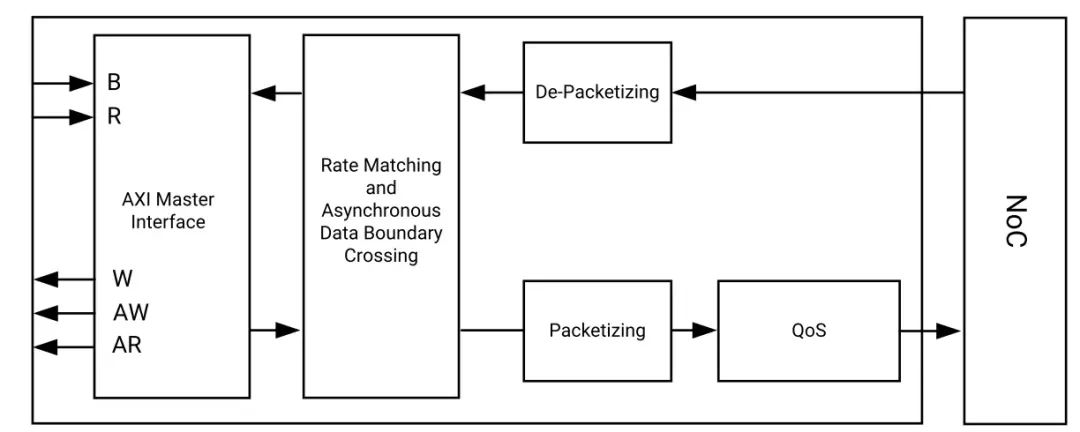

NSU 結(jié)構(gòu)

從以上的 NMU, NSU 結(jié)構(gòu)可以看到,對用戶的接口仍然是 AXI 總線,在其內(nèi)部,將 AXI 數(shù)據(jù)進(jìn)行組包或解包,連接到 NoC 網(wǎng)絡(luò)。

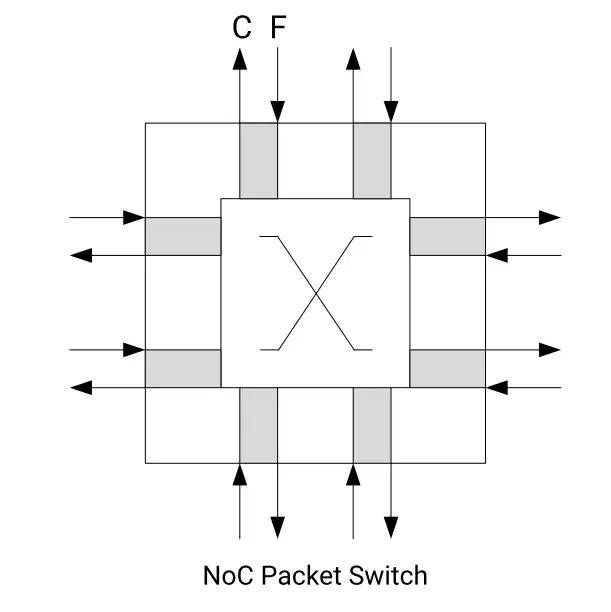

NPS 結(jié)構(gòu)

而 NMU 和 NSU 都是連接到 NPS 上的,它相當(dāng)于一個(gè)路由器,將數(shù)據(jù)轉(zhuǎn)發(fā)給目的設(shè)備。它是一個(gè)全雙工的 4x4 switch,每個(gè)端口在每個(gè)方向支持 8 個(gè)虛擬通道,采用基于信用的流控,類似于 TCP 的滑動窗口。

NoC 是 Versal 開發(fā)中非常重要的部件,PS 端訪問 DDR,PL 端訪問 DDR 都是通過 NoC,與 Versal 不同的是,versal 在 PS 端沒有 DDR 控制器,都是通過 NoC 訪問,因此了解 NoC 結(jié)構(gòu)是很有必要的,更多的內(nèi)容可以參考官方的 pg313 文檔。

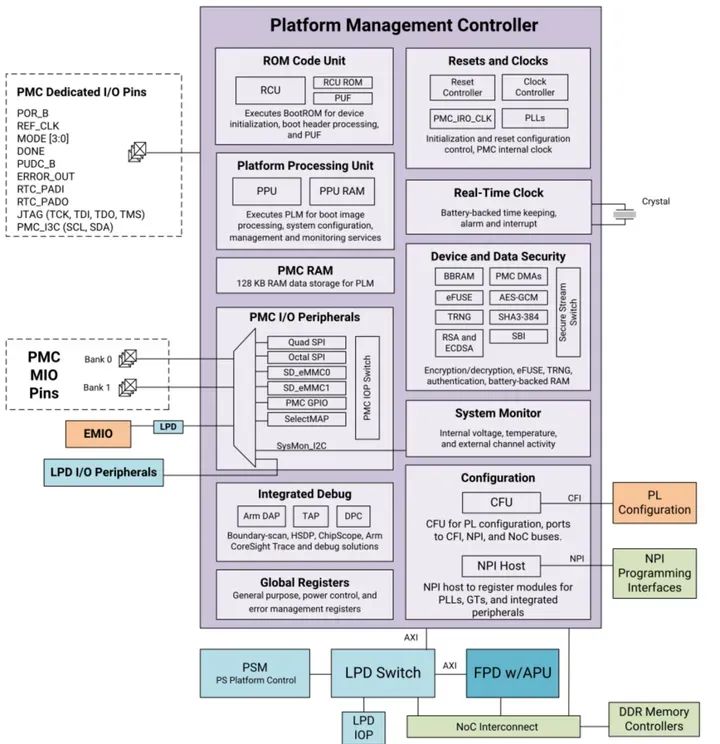

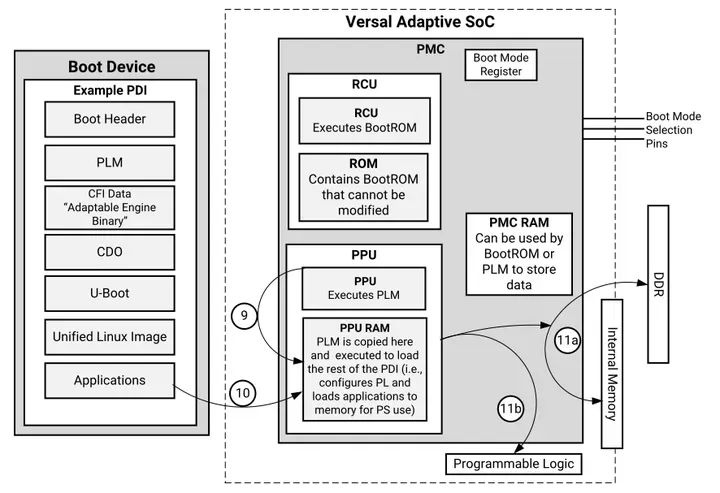

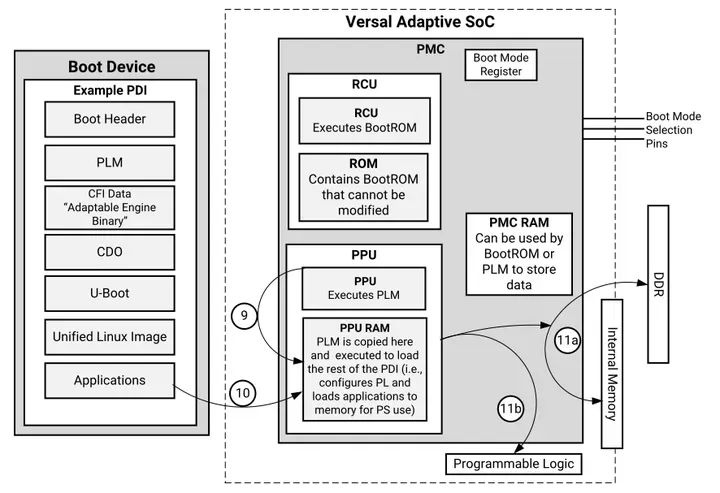

PMC 架構(gòu)

PMC(平臺管理控制器)在啟動,配置,運(yùn)行時(shí)做平臺的管理。從下圖的結(jié)構(gòu)圖中可以看出,PMC 由 ROM Code Unit,Platform Processing Unit,PMC I/O Peripherals 等單元組成,功能豐富。在這里主要介紹一下 PMC 是如何引導(dǎo)程序啟動的。

PMC 結(jié)構(gòu)圖

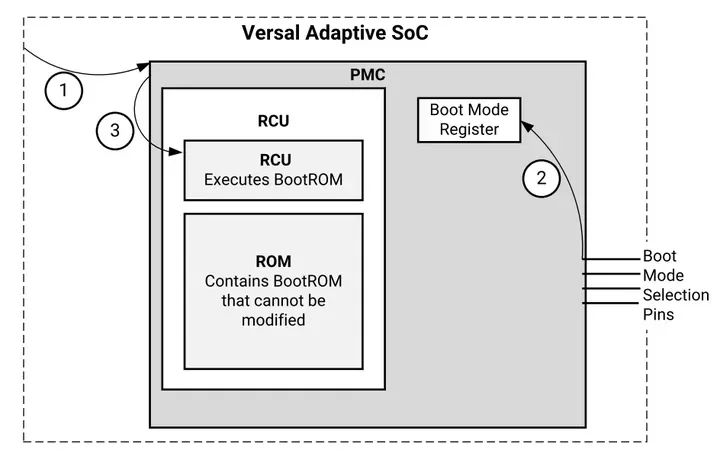

第一階段:Pre-Boot

PMC 檢測 PMC 電源和 POR_B 釋放

2. PMC 讀取啟動模式引腳并存入 boot mode 寄存器

3. PMC 發(fā)送復(fù)位給 RCU(ROM code unit)

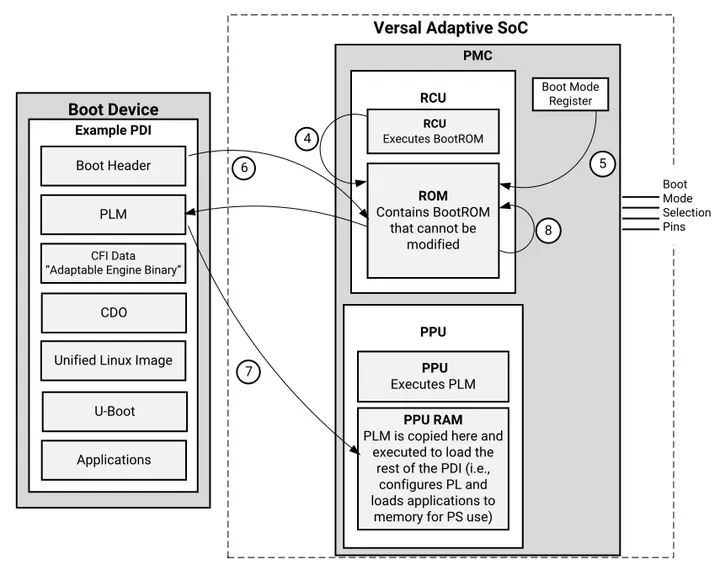

第二階段:Boot Setup

4. RCU 從 RCU ROM 中執(zhí)行 BootROM

5. BootROM 讀出 boot mode 寄存器,選擇啟動設(shè)備

6. BootROM 從啟動設(shè)備讀取 PDI(programmable device image) 并校驗(yàn)

7. BootROM 釋放 PPU 的復(fù)位,將 PLM 加載到 PPU RAM 并校驗(yàn)。校驗(yàn)后,PPU 喚醒,PLM 軟件開始執(zhí)行。

8. BootROM 進(jìn)入睡眠狀態(tài)

第三階段:Load Platform

9. PPU 開始從 PPU RAM 中執(zhí)行 PLM

10. PLM 開始讀取并運(yùn)行 PDI 模塊

11. PLM 利用 PDI 內(nèi)容配置 Versal 其他部分

11a: PLM 為以下模塊配置數(shù)據(jù):PMC, PS clocks

(MIO ,clocks, resets 等)(CDO 文件)

NoC 初始化和 NPI 模塊(DDR 控制器,NoC,

GT,XPIPE,I/Os,clocking 和其他 NPI 模塊

PLM 加載 APU 和 RPU 的應(yīng)用程序 ELF 到存儲空間,

如 DDR,OCM,TCM 等

11b: PL 端邏輯配置

PL 端數(shù)據(jù)(CFI 文件)

AI Engine 配置(AI Engine CDO)

第四階段:Post-Boot

12. PLM 繼續(xù)運(yùn)行,直到下一次 POR 或系統(tǒng)復(fù)位。并負(fù)責(zé) DFX 重配置,電源管理,子系統(tǒng)重啟,錯(cuò)誤管理,安全服務(wù)。

Versal 芯片開發(fā)流程的簡介

由于 Versal 將 CPU 與 FPGA 集成在了一起,開發(fā)人員既需要設(shè)計(jì) ARM 的操作系統(tǒng)應(yīng)用程序和設(shè)備的驅(qū)動程序,又需要設(shè)計(jì) FPGA 部分的硬件邏輯設(shè)計(jì)。開發(fā)中既要了解 Linux 操作系統(tǒng),系統(tǒng)的構(gòu)架,也需要搭建一個(gè) FPGA 和 ARM 系統(tǒng)之間的硬件設(shè)計(jì)平臺。所以 Versal 的開發(fā)是需要軟件人員和硬件硬件人員協(xié)同設(shè)計(jì)并開發(fā)的。這既是 Versal 開發(fā)中所謂的 " 軟硬件協(xié)同設(shè)計(jì)”。

Versal 系統(tǒng)的硬件系統(tǒng)和軟件系統(tǒng)的設(shè)計(jì)和開發(fā)需要用到一下的開發(fā)環(huán)境和調(diào)試工具:Xilinx Vivado。Vivado 設(shè)計(jì)套件實(shí)現(xiàn) FPGA 部分的設(shè)計(jì)和開發(fā),管腳和時(shí)序的約束,編譯和仿真,實(shí)現(xiàn) RTL 到比特流的設(shè)計(jì)流程。

Xilinx Vitis 是 Xilinx 軟件開發(fā)套件 (SDK), 在 Vivado 硬件系統(tǒng)的基礎(chǔ)上,系統(tǒng)會自動配置一些重要參數(shù),其中包括工具和庫路徑、編譯器選項(xiàng)、JTAG 和閃存設(shè)置,調(diào)試器連接已經(jīng)裸機(jī)板支持包 (BSP)。SDK 也為所有支持的 Xilinx IP 硬核提供了驅(qū)動程序。Vitis 支持 IP 硬核(FPGA 上)和處理器軟件協(xié)同調(diào)試,我們可以使用高級 C 或 C++ 語言來開發(fā)和調(diào)試 ARM 和 FPGA 系統(tǒng),測試硬件系統(tǒng)是否工作正常。Vitis 軟件也是 Vivado 軟件自帶的,無需單獨(dú)安裝。

Versal 的開發(fā)也是先硬件后軟件的方法。具體流程如下:

在 Vivado 上新建工程,增加一個(gè)嵌入式的源文件。

在 Vivado 里添加和配置 PS 和 PL 部分基本的外設(shè),或需要添加自定義的外設(shè)。

在 Vivado 里生成頂層 HDL 文件,并添加約束文件。再編譯生成比特流文件(*.pdi)。

導(dǎo)出硬件信息到 Vitis 軟件開發(fā)環(huán)境,在 Vitis 環(huán)境里可以編寫一些調(diào)試軟件驗(yàn)證硬件和軟件,結(jié)合比特流文件單獨(dú)調(diào)試 Versal 系統(tǒng)。

在 VMware 虛擬機(jī)里生成 u-boot.elf、 bootloader 鏡像。

在 Vitis 里將比特流文件和 u-boot.elf 文件生成一個(gè) BOOT.pdi 文件。

在 VMware 里生成 Ubuntu 的內(nèi)核鏡像文件 Zimage 和 Ubuntu 的根文件系統(tǒng)。另外還需要要對 FPGA 自定義的 IP 編寫驅(qū)動。

把 BOOT、內(nèi)核、設(shè)備樹、根文件系統(tǒng)文件放入到 SD 卡中,啟動開發(fā)板電源,Linux 操作系統(tǒng)會從 SD 卡里啟動。

審核編輯:劉清

-

處理器

+關(guān)注

關(guān)注

68文章

19607瀏覽量

232373 -

控制器

+關(guān)注

關(guān)注

113文章

16767瀏覽量

181773 -

電源管理

+關(guān)注

關(guān)注

116文章

6264瀏覽量

145514 -

PMC

+關(guān)注

關(guān)注

0文章

89瀏覽量

15084 -

片上網(wǎng)絡(luò)

+關(guān)注

關(guān)注

0文章

33瀏覽量

11910

原文標(biāo)題:【ALINX 技術(shù)分享】AMD Versal AI Edge 自適應(yīng)計(jì)算加速平臺之 Versal 介紹(2)

文章出處:【微信號:ALINX,微信公眾號:ALINX】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

相關(guān)推薦

【ALINX 技術(shù)分享】AMD Versal AI Edge 自適應(yīng)計(jì)算加速平臺之準(zhǔn)備工作(1)

【ALINX 技術(shù)分享】AMD Versal AI Edge 自適應(yīng)計(jì)算加速平臺之 Versal 介紹(2)

AMD Versal AI Edge自適應(yīng)計(jì)算加速平臺PL LED實(shí)驗(yàn)(3)

AMD Versal AI Edge自適應(yīng)計(jì)算加速平臺之PL LED實(shí)驗(yàn)(3)

AMD Versal AI Edge自適應(yīng)計(jì)算加速平臺之PL通過NoC讀寫DDR4實(shí)驗(yàn)(4)

在Vivado中構(gòu)建AMD Versal可擴(kuò)展嵌入式平臺示例設(shè)計(jì)流程

Xilinx推出Versal:業(yè)界首款自適應(yīng)計(jì)算加速平臺,支持快速創(chuàng)新

賽靈思發(fā)布自適應(yīng)計(jì)算加速平臺芯片系列Versal

賽靈思Versal自適應(yīng)計(jì)算加速平臺助于高效實(shí)現(xiàn)設(shè)計(jì)目標(biāo)

賽靈思Versal自適應(yīng)計(jì)算加速平臺指南

Versal:首款自適應(yīng)計(jì)算加速平臺(ACAP)

AMD發(fā)布第二代Versal自適應(yīng)SoC,AI嵌入式領(lǐng)域再提速

貿(mào)澤開售適用于AI和機(jī)器學(xué)習(xí)應(yīng)用的 AMD Versal AI Edge VEK280評估套件

AMD Versal自適應(yīng)SoC器件Advanced Flow概覽(下)

評論