什么是IRIG-B碼對(duì)時(shí)

IRIG-B(inter-range instrumentationgroup-B)碼是一種時(shí)間同步標(biāo)準(zhǔn),通常用于精確的時(shí)間測(cè)量和數(shù)據(jù)同步,廣泛應(yīng)用于電力、通信、航空等領(lǐng)域。

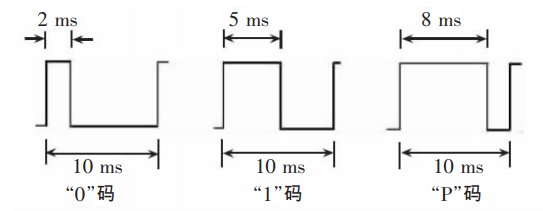

IRIG-B碼為每秒一幀的時(shí)間串碼,一幀串碼中包含100個(gè)碼元,頻率為1KHz,即每個(gè)碼元占用10ms時(shí)間。IRIG-B碼基本的碼元為"0"碼元、"1"碼元和"P"碼元,"0"碼元和"1"碼元對(duì)應(yīng)的脈沖寬度為2ms和5ms,"P"碼元為位置碼元,對(duì)應(yīng)的脈沖寬度為8ms,IRIG-B碼信息的基本碼元的示意圖如下所示。

圖1

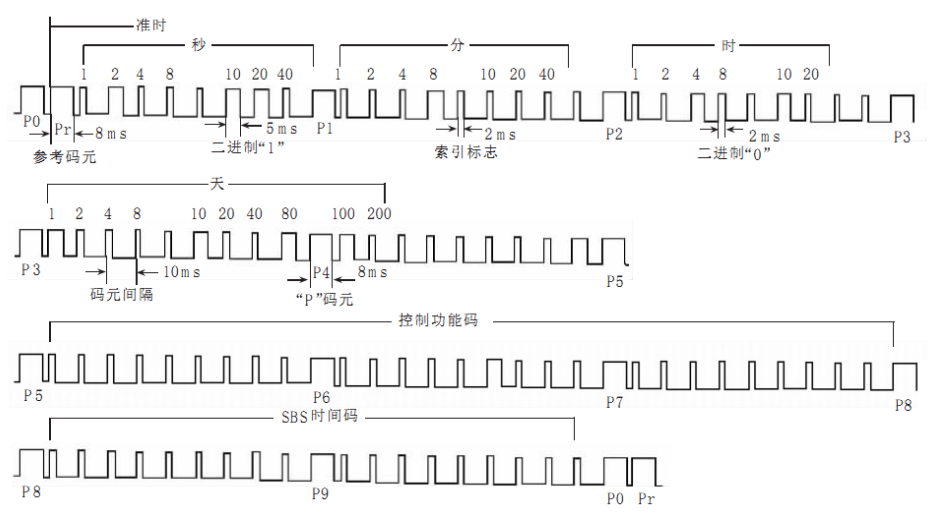

下圖為一幀的IRIG-B碼脈沖序列結(jié)構(gòu)示意圖。連續(xù)兩個(gè)"P"碼元表示整秒的開(kāi)始,第二個(gè)"P"碼元的脈沖前沿為“準(zhǔn)時(shí)”參考點(diǎn),定義其為"Pr"。每10個(gè)碼元有一個(gè)位置碼元,共有10個(gè),定義其為P1,P2,…,P9,P0。IRIG-B碼時(shí)間格式的時(shí)序?yàn)槊搿⒎帧r(shí)、天,所占信息位分別為:秒7位、分7位、時(shí)6位、天10位,其位置在P0 ~ P5之間。

通常,從"Pr"開(kāi)始對(duì)碼元進(jìn)行編號(hào),分別定義為第0,1,2,…,99碼元,則“秒”信息位于第1、2、3、4、6、7、8碼元,“分”信息位于第10、11、12、13、15、16,17碼元,“時(shí)”信息位于第20、21、22、23、25、26碼元,“天”信息位于第30、31、32、33、35、36、37、38、40、41碼元。

圖2

IRIG-B碼對(duì)時(shí)應(yīng)用場(chǎng)景

IRIG-B碼對(duì)時(shí)可應(yīng)用于繼電保護(hù)裝置、電力RTU、電力錄波器、通訊管理機(jī)、電能質(zhì)量在線監(jiān)測(cè)等領(lǐng)域。創(chuàng)龍科技已基于TI AM62x異構(gòu)多核處理器實(shí)現(xiàn)IRIG-B碼對(duì)時(shí)方案,降低了終端用戶的開(kāi)發(fā)難度,縮減了研發(fā)時(shí)間,可快速進(jìn)行產(chǎn)品方案評(píng)估與技術(shù)預(yù)研。

圖3

常見(jiàn)IRIG-B碼對(duì)時(shí)實(shí)現(xiàn)方案

IRIG-B碼對(duì)時(shí)的實(shí)現(xiàn)常見(jiàn)方案一般基于FPGA或MCU實(shí)現(xiàn),具體方案實(shí)現(xiàn)方式如下。

(1)基于FPGA實(shí)現(xiàn)

為達(dá)到IRIG-B碼與時(shí)間信號(hào)輸入、輸出的精確同步,采用現(xiàn)代化靶場(chǎng)的IRIG-B碼編碼和解碼的原理,從工程的角度出發(fā),提出了使用現(xiàn)場(chǎng)可編程門陣列(FPGA)來(lái)實(shí)現(xiàn)IRIG-B碼編碼和解碼的設(shè)計(jì)方案和體系結(jié)構(gòu),設(shè)計(jì)中會(huì)涉及到幾個(gè)不同的時(shí)鐘頻率,F(xiàn)PGA對(duì)時(shí)鐘的同步性具有靈活性、效率高、且功耗低,抗干擾性好的特點(diǎn)。結(jié)果表明,F(xiàn)PGA能夠確保為從設(shè)備提供同源的時(shí)鐘基準(zhǔn),使時(shí)鐘與信號(hào)的延遲控制在200ns以內(nèi),從而得到了IRIG-B碼與時(shí)間精確同步的效果。

但是,基于FPGA實(shí)現(xiàn)IRIG-B碼開(kāi)發(fā)難度較大,時(shí)間投入較多,開(kāi)發(fā)成本將會(huì)較高,不利于產(chǎn)品的快速上市。

(2)基于MCU實(shí)現(xiàn)

MCU(Micro Control Unit)即微控制單元,通過(guò)MCU核心可實(shí)現(xiàn)解析IRIG-B碼時(shí)序并提取時(shí)間信息,再將時(shí)間信息同步至其他核心。

基于MCU實(shí)現(xiàn)IRIG-B碼開(kāi)發(fā)方案結(jié)構(gòu)簡(jiǎn)單、開(kāi)發(fā)成本較低、同步精度較高,可滿足多種工業(yè)應(yīng)用場(chǎng)景要求。

AM62xIRIG-B碼對(duì)時(shí)方案

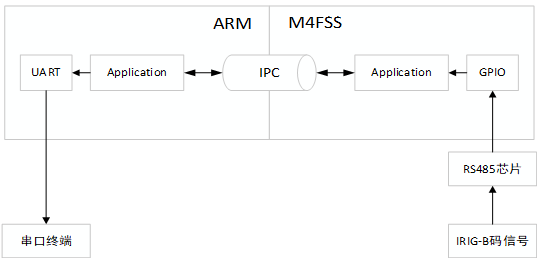

本章節(jié)主要描述創(chuàng)龍科技基于TI AM62x的MCU(Cortex-M4F)核心實(shí)現(xiàn)IRIG-B碼信號(hào)解析功能。

AM62x內(nèi)部集成Cortex-A53 + Cortex-M4F核心,可使用Cortex-M4F實(shí)現(xiàn)IRIG-B碼對(duì)時(shí)功能,無(wú)需增加額外的MCU成本。并且,通過(guò)內(nèi)部MCU實(shí)現(xiàn)IRIG-B碼對(duì)時(shí)功能方案,硬件設(shè)計(jì)簡(jiǎn)單,有利于快速開(kāi)發(fā)產(chǎn)品。

(1)案例說(shuō)明

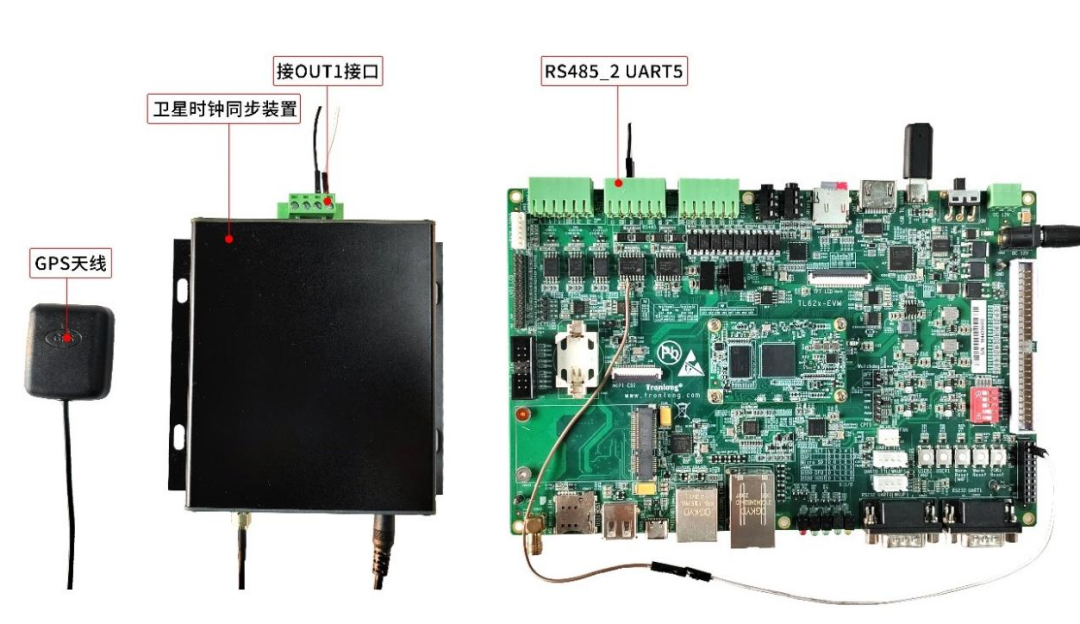

衛(wèi)星時(shí)鐘同步裝置(廠家:南京諾煌電氣科技有限公司,型號(hào):YS-DN-100)通過(guò)GPS天線模塊獲取標(biāo)準(zhǔn)時(shí)間信息并輸出IRIG-B碼信號(hào),經(jīng)評(píng)估板板載RS485芯片轉(zhuǎn)換成電平信號(hào)后傳輸至Cortex-M4F核心,Cortex-M4F核心通過(guò)讀取GPIO引腳電平,解析IRIG-B碼時(shí)序并提取時(shí)間信息,再通過(guò)TI-RPMsg機(jī)制將時(shí)間信息發(fā)送至Cortex-A53核心打印時(shí)間信息。系統(tǒng)框圖如下所示。

圖4

(2)

案例測(cè)試

本案例需在開(kāi)闊場(chǎng)地進(jìn)行測(cè)試,請(qǐng)確保衛(wèi)星時(shí)鐘同步裝置的RUN指示燈處于常亮狀態(tài)(表示設(shè)備工作正常),否則請(qǐng)檢查GPS天線連接是否正常。

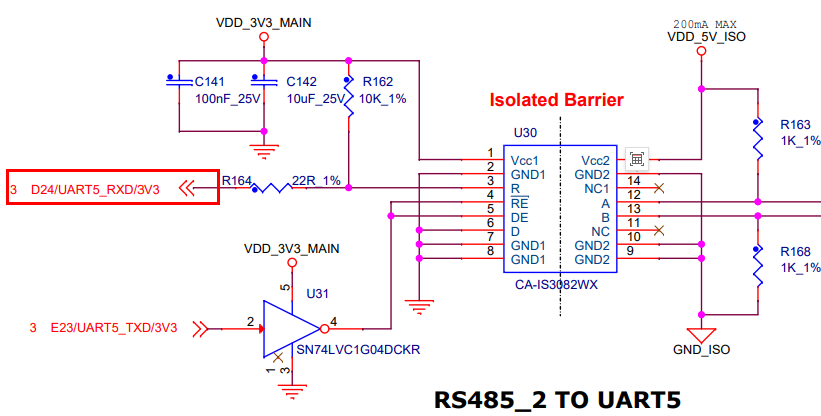

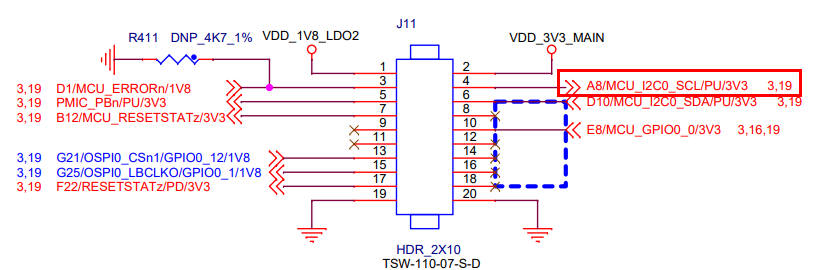

由于評(píng)估底板RS485_2 UART5為Cortex-A53核心的外設(shè),因此請(qǐng)通過(guò)飛線的方式將RS485芯片(U30)的pin3引腳連接至EXPROT接口(J11)的pin4引腳(即Cortex-M4F核心GPIO)。衛(wèi)星時(shí)鐘同步裝置輸出的IRIG-B碼信號(hào)經(jīng)評(píng)估底板RS485_2 UART5接口后,再經(jīng)過(guò)EXPROT接口(J11)的pin4引腳輸入至Cortex-M4F核心。

圖5

圖6

請(qǐng)將衛(wèi)星時(shí)鐘同步裝置的ANT接口連接至GPS天線模塊,將衛(wèi)星時(shí)鐘同步裝置OUT1接口的“+端子”連接至評(píng)估板的RS485_2 UART5接口“A2端子”、OUT1接口的“-端子”連接至評(píng)估板的RS485_2 UART5接口“B2端子”,硬件連接如下圖所示。

圖7

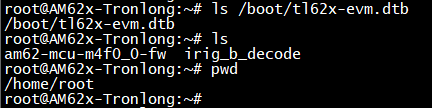

請(qǐng)將本案例"dtsbin"目錄下的tl62x-evm.dtb設(shè)備樹(shù)文件拷貝至Linux系統(tǒng)啟動(dòng)卡"/boot/"目錄下,替換原有的tl62x-evm.dtb設(shè)備樹(shù)文件。然后將案例bin目錄下的am62-mcu-m4f0_0-fw文件、irig_b_decode可執(zhí)行程序拷貝至Linux系統(tǒng)啟動(dòng)卡文件系統(tǒng)"/home/root/"目錄下。

圖8

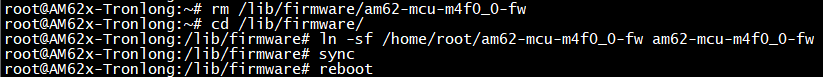

評(píng)估板上電,從Linux系統(tǒng)啟動(dòng)卡啟動(dòng),依次執(zhí)行如下命令,更新Cortex-M4F核心固件,并重啟評(píng)估板。

Target#rm /lib/firmware/am62-mcu-m4f0_0-fw

Target#cd /lib/firmware/

Target#ln -sf /home/root/am62-mcu-m4f0_0-fw am62-mcu-m4f0_0-fw

Target#sync

Target#reboot

圖9

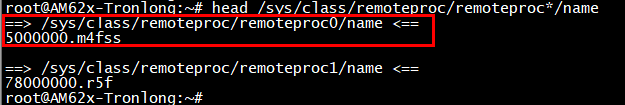

執(zhí)行如下命令,查詢Cortex-M4F核心與remoteproc對(duì)應(yīng)關(guān)系。

備注:Cortex-M4F核心對(duì)應(yīng)的RemoteProc Name為5000000.m4fss。

Target#head /sys/class/remoteproc/remoteproc*/name

圖10

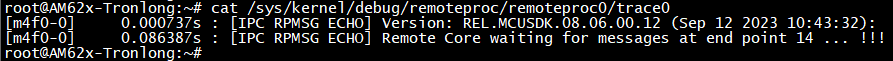

根據(jù)查詢結(jié)果,執(zhí)行如下命令查看Cortex-M4F核心程序運(yùn)行日志,確認(rèn)Cortex-M4F核心運(yùn)行狀態(tài)。

Target#cat /sys/kernel/debug/remoteproc/remoteproc0/trace0

圖11

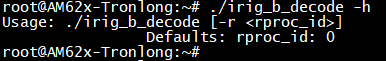

執(zhí)行如下命令,查看程序運(yùn)行參數(shù)。

Target#./irig_b_decode -h

備注:rproc_id:核心ID。Cortex-M4F核心ID為9,默認(rèn)ID為0。

圖12

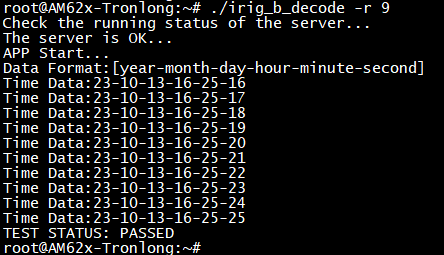

執(zhí)行如下命令,解析IRIG-B碼時(shí)序并提取時(shí)間信息,可看到串口終端打印當(dāng)前日期如下圖所示。

Target#./irig_b_decode -r9

圖13

審核編輯 黃宇

-

處理器

+關(guān)注

關(guān)注

68文章

19265瀏覽量

229687 -

FPGA

+關(guān)注

關(guān)注

1629文章

21729瀏覽量

603057 -

異構(gòu)多核

+關(guān)注

關(guān)注

0文章

6瀏覽量

6920 -

IRIG-B碼

+關(guān)注

關(guān)注

0文章

8瀏覽量

9343

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

基于TI AM62x的Debian系統(tǒng)正式發(fā)布,豐富的軟件生態(tài),讓您的應(yīng)用開(kāi)發(fā)更便利!

AM62x DDR板設(shè)計(jì)和布局指南

AM62x延長(zhǎng)開(kāi)機(jī)時(shí)間應(yīng)用說(shuō)明

AM62x Sitara?處理器數(shù)據(jù)表

B碼對(duì)時(shí)方案,基于TI AM62x異構(gòu)多核工業(yè)處理器實(shí)現(xiàn)!

B碼對(duì)時(shí)方案,基于TI AM62x異構(gòu)多核工業(yè)處理器實(shí)現(xiàn)!

GPMC并口多通道AD采集案例,基于TI AM62x四核處理器平臺(tái)!

GPMC并口多通道AD采集案例,基于TI AM62x四核處理器平臺(tái)!

沒(méi)搶到?米爾AM62x開(kāi)發(fā)板限量5折又來(lái)了

基于TI AM62x的SPI接口配置

“進(jìn)口”雙核A53@1.4GHz,超高性價(jià)比!“郵票孔”AM62x工業(yè)核心板,正式發(fā)布!

B碼對(duì)時(shí)方案,基于TI AM62x異構(gòu)多核工業(yè)處理器實(shí)現(xiàn)!

B碼對(duì)時(shí)方案,基于TI AM62x異構(gòu)多核工業(yè)處理器實(shí)現(xiàn)!

評(píng)論