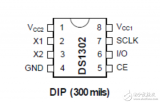

Clk引腳在芯片中是時鐘信號的輸入引腳。時鐘信號在數字電路中起著非常重要的作用,它用于同步芯片內各個模塊的操作,確保它們按照正確的時間序列執行任務。

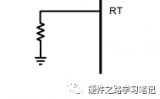

時鐘信號的輸入通常由外部晶振或振蕩器提供,被接入芯片的clk引腳。這個引腳會周期性地產生一個方波信號,頻率通常以赫茲(Hz)為單位表示。方波的周期等于時鐘周期,即一個方波周期內的時間。

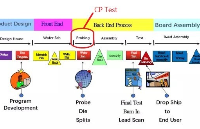

時鐘信號的周期是決定系統的工作速度的關鍵因素之一。更高的時鐘頻率可以使芯片工作得更快,但也需要更多的功耗和更復雜的電路設計。因此,在設計芯片時,必須權衡時鐘頻率和功耗之間的關系,并選擇一個適合的時鐘頻率。

時鐘信號的作用可以總結如下:

- 數據同步:時鐘信號用于同步系統中的各個模塊,確保它們在正確的時間上按照指定的順序執行任務。通過在時鐘上升沿或下降沿的瞬間對數據進行采樣,可以確保數據在傳輸過程中不會發生錯誤。

- 芯片節奏:時鐘信號作為整個芯片內部的節奏引導,控制各個模塊之間的通信和數據傳輸。它使各個模塊能夠在預定的時間內完成任務,并與其他模塊進行協調。

- 時序控制:時鐘信號用于控制芯片中的時序邏輯電路,如計數器和時序控制器。這些電路根據時鐘信號的頻率和相位來生成特定的時序波形,對系統的工作流程進行協調和控制。

- 電源噪聲濾波:時鐘信號也可以用作濾波器,減少電源噪聲對芯片內部電路的影響。通過將時鐘信號傳遞到電源回路中,可以將噪聲信號降低到一個可以接受的水平,以確保芯片的正常運行。

時鐘信號在芯片設計中的重要性不言而喻。一個正確的時鐘設計可以提高芯片的穩定性、可靠性和性能。在設計時,需要考慮時鐘頻率與功耗、干擾抗性等因素的平衡,以及時鐘信號的分配和布線,以確保時鐘信號在整個芯片中的準確傳遞和穩定性。

總結而言,Clk引腳在芯片中扮演著時鐘信號的接收和傳遞的角色,它是芯片運行和同步的關鍵。它的作用非常重要,在數字電路設計中占據著核心地位。通過合理的時鐘設計,可以提高芯片的性能和穩定性,促進數字系統的良好運行。

-

芯片

+關注

關注

459文章

52199瀏覽量

436328 -

振蕩器

+關注

關注

28文章

3968瀏覽量

140429 -

引腳

+關注

關注

16文章

1576瀏覽量

52366 -

時鐘信號

+關注

關注

4文章

465瀏覽量

29082 -

CLK

+關注

關注

0文章

127瀏覽量

17523

發布評論請先 登錄

hmc704 BIAS引腳影響相噪請問這個引腳在芯片中起什么作用?

AD7606模塊中的BUSY引腳是否必須接入到主控芯片中進行控制處理呢?

AD9515的CLK與CLKB這兩個引腳接差分時鐘時哪個接CLK+,哪個接CLK-?

AD9683的引腳如何與zynq 7015芯片中的JESD204 ip核端口對應相連?

如何吧項目實現在FPGA芯片中

語音芯片中的八腳指的是什么

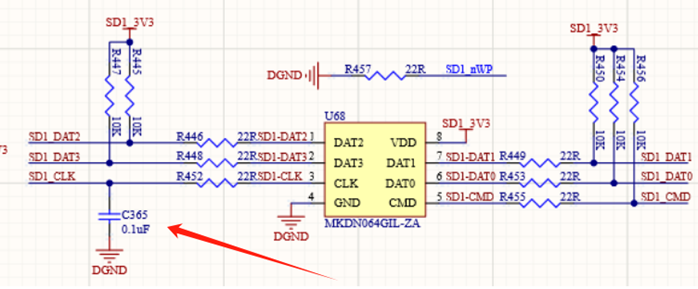

SD NAND的CLK引腳的注意事項和走線規范

評論