一、概述

SPI:Serial Peripheral Interface,串行外圍設(shè)備接口。

是由摩托羅拉在20世紀(jì)80年代中期開(kāi)發(fā)的同步串行總線接口規(guī)范(帶有時(shí)鐘信號(hào),通過(guò)時(shí)鐘極性和時(shí)鐘相位來(lái)控制采樣,

即同步傳輸)。

1、支持半雙工、全雙工通信模式。

2、沒(méi)有流控制和應(yīng)答機(jī)制來(lái)確認(rèn)是否接收到數(shù)據(jù)(UART有校驗(yàn)或流控制)。

3、沒(méi)有一個(gè)固定的傳輸速率規(guī)定,已有器件SPI輸出速率達(dá)到50Mbps以上(I2C有明確規(guī)定速率)。

4、只能板內(nèi)的短距離傳輸(RS232、RS485輸出距離遠(yuǎn))。

5、沒(méi)有限制傳輸bit數(shù)量,常用的是8bit或9bit。

6、不需要硬件地址(I2C要地址),采用片選。

7、主從模式,一托多。

二、3線和4線模式

3線SPI和4線SPI各個(gè)模式下信號(hào)定義:

3線9bit I型 接口信號(hào):SCL、CS、SDA

3線9bit II型接口信號(hào):SCL、CS、SDO、SDI

4線8bit I型接口信號(hào):SCL、CS、DCX、SDA

4線8bit II型接口信號(hào):SCL、CS、DCX、SDO、SDI

3線9bit 2 data Lane 接口信號(hào):SCL、CS、D0、D1

對(duì)于3線或4線來(lái)區(qū)分,并不是信號(hào)線的數(shù)量,也不是網(wǎng)上說(shuō)的半雙工和全雙工,或者數(shù)據(jù)線數(shù)量差異。

個(gè)人認(rèn)為:

3線說(shuō)的是時(shí)鐘、片選、數(shù)據(jù)信號(hào)(不管是一根數(shù)據(jù)線,還是兩根數(shù)據(jù)線),共三種信號(hào)。

4線說(shuō)的是時(shí)鐘、片選、數(shù)據(jù)信號(hào)、數(shù)據(jù)或命令控制線(確定發(fā)送的是數(shù)據(jù)還是命令),共4中信號(hào)。

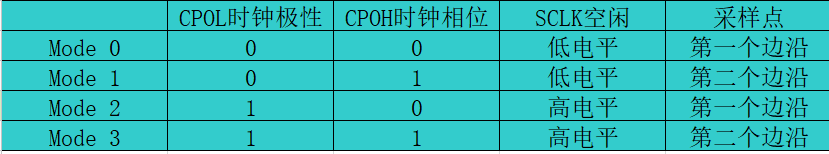

三、SPI 四種工作模式

通過(guò)CPOL時(shí)鐘極性和CPHA時(shí)鐘相位的搭配來(lái)得到四種工作模式:

CPOL時(shí)鐘極性定義的是 SCLK時(shí)鐘線空閑狀態(tài)時(shí)的電平

CPOL=0,即SCLK=0,表示SCLK時(shí)鐘信號(hào)線在空閑狀態(tài)時(shí)的電平為低電平,因此有效狀態(tài)為高電平。

CPOL=1,即SCLK=1,表示SCLK時(shí)鐘信號(hào)線在空閑狀態(tài)時(shí)的電平為高電平,因此有效狀態(tài)為低電平。

CPHA時(shí)鐘相位定義的是數(shù)據(jù)位相對(duì)于時(shí)鐘線的時(shí)序(即相位)

CPHA=0,即表示輸出(out)端在上一個(gè)時(shí)鐘周期的后沿改變數(shù)據(jù),而輸入(in)端在時(shí)鐘周期的前沿(或不久之后)捕

獲數(shù)據(jù)。輸出端保持?jǐn)?shù)據(jù)有效直到當(dāng)前時(shí)鐘周期的尾部邊緣。對(duì)于第一個(gè)時(shí)鐘周期來(lái)說(shuō),第一位的數(shù)據(jù)必須在時(shí)鐘前沿之

前出現(xiàn)在MOSI線上。也就是一個(gè)CPHA=0的周期包括半個(gè)時(shí)鐘空閑和半個(gè)時(shí)鐘置位的周期。

CPHA=1,即表示輸出(out)端在當(dāng)前時(shí)鐘周期的前沿改變數(shù)據(jù),而輸入(in)端在時(shí)鐘周期的后沿(或不久之后)捕獲

數(shù)據(jù)。輸出端保持?jǐn)?shù)據(jù)有效直到下一個(gè)時(shí)鐘周期的前沿。對(duì)于最后一個(gè)時(shí)鐘周期來(lái)說(shuō),從機(jī)設(shè)備在片選信號(hào)消失之前保持

MISO信號(hào)線有效。也就是一個(gè)CHPA=1的周期包括半個(gè)時(shí)鐘置位和半個(gè)時(shí)鐘空閑的周期。

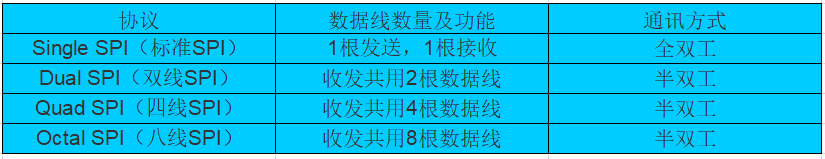

四、SPI升級(jí)版

SPI flash接口有standard SPI、Dual SPI、Quad SPI、Octal SPI,也就是所謂的1248線模式。

五、SDR和DDR模式

SPI通信支持SDR和DDR模式。

SDR:Single Data Rate通過(guò) SCLK 的觸發(fā)對(duì)信號(hào)進(jìn)行采樣時(shí),一個(gè)時(shí)鐘周期只執(zhí)行一次,稱為單倍數(shù)據(jù)速率模式。

DDR:Double Data Rate通過(guò) SCLK 的觸發(fā)對(duì)信號(hào)進(jìn)行采樣時(shí),每個(gè)上升沿和下降沿將采樣一次。

也就是說(shuō)一個(gè)時(shí)鐘周期內(nèi)發(fā)送2位或者接收2位數(shù)據(jù),稱為雙倍數(shù)據(jù)速率模式

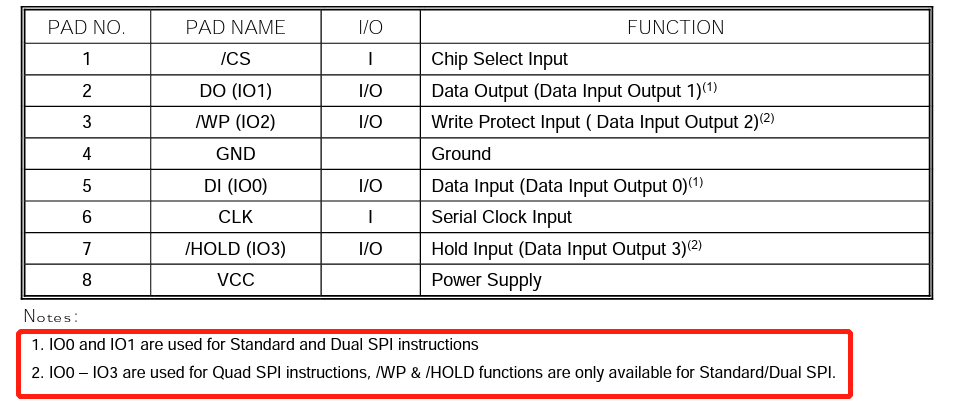

六、SPI Flash接口

Dual SPI有兩根數(shù)據(jù)IO;Quad SPI有4根數(shù)據(jù)IO。

SPI flash spec:

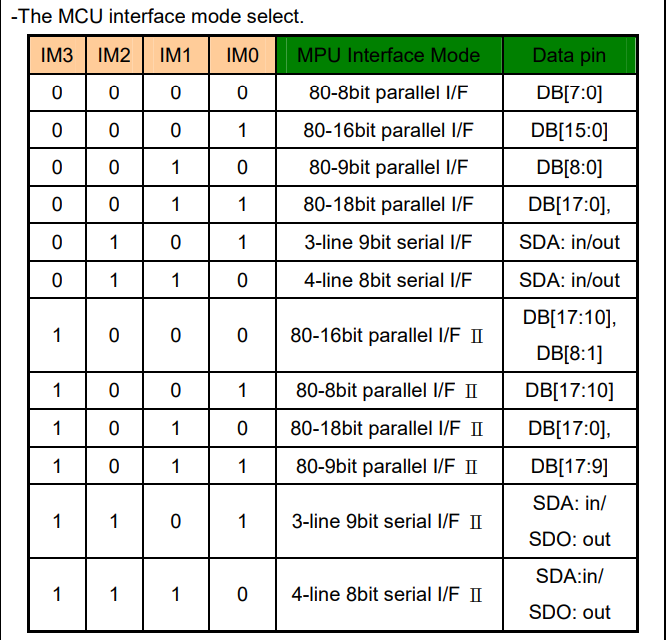

七、SPI TFT液晶屏接口

TFT液晶屏ST7789 spec定義,支持串行和并行,支持SPI多種通信模式。

八、信號(hào)定義及連線

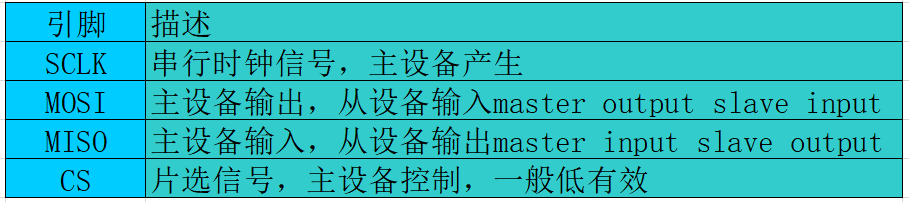

標(biāo)準(zhǔn)SPI接口信號(hào)定義:

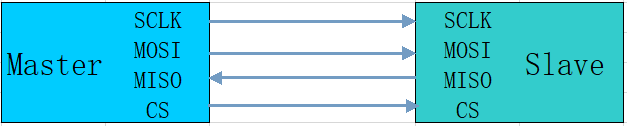

標(biāo)準(zhǔn)的SPI規(guī)范連線:

SDOSDI網(wǎng)絡(luò)命名的連線(SDO和SDI交叉):

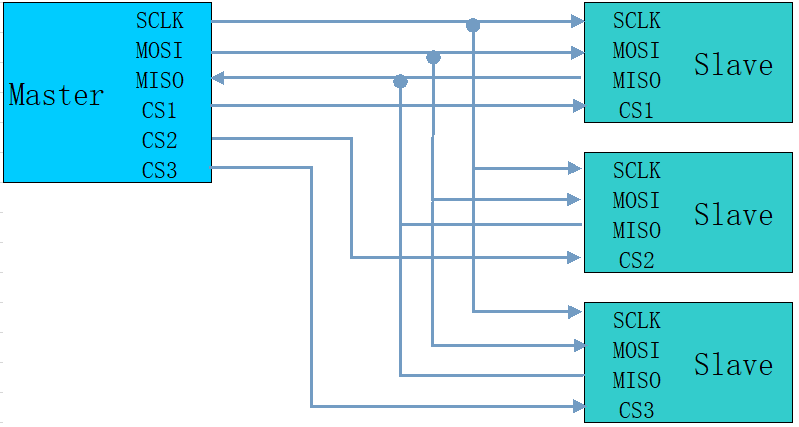

SPI總線,一對(duì)多連線:

九、小結(jié)

1、有的參考設(shè)計(jì)原理圖中,用SDI表示MOSI,用SDO表示MISO,連線要注意輸出和輸入的定義。

2、芯片引腳的信號(hào)輸入或輸出,是針對(duì)自身來(lái)標(biāo)明的,因此在主從設(shè)備芯片的輸出或輸入要連接正確。

3、電路設(shè)計(jì)上引腳信號(hào)不需要上拉。如果是IO模擬的話,需注意是不是開(kāi)漏,如是要加上拉。另,要確認(rèn)器件spec的SPI

信息,可能有特殊的要加上下拉。

4、一對(duì)多的連線,片選信號(hào)CS單獨(dú)控制,多個(gè)從設(shè)備需要多個(gè)CS信號(hào)。

5、從設(shè)備未被選中時(shí),信號(hào)線變成高阻態(tài)(斷開(kāi))。

6、Layout上沒(méi)有特殊要求,當(dāng)然可以SCLK信號(hào)包下地。

審核編輯 黃宇

-

通信協(xié)議

+關(guān)注

關(guān)注

28文章

879瀏覽量

40297 -

SPI

+關(guān)注

關(guān)注

17文章

1706瀏覽量

91502 -

總線

+關(guān)注

關(guān)注

10文章

2878瀏覽量

88051

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

通信協(xié)議之SPI總線硬件篇

通信協(xié)議之SPI總線硬件篇

評(píng)論