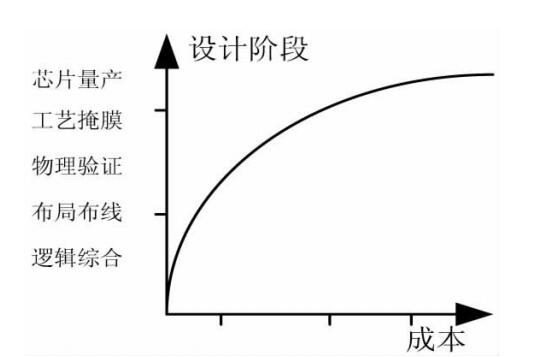

大型SOC項目的綜合非常耗時間,常常花費好幾天。當需要做功能ECO時,代碼的改動限定在某些子模塊里,設計人員并不想重跑一次完整的綜合,這種方法縮短了一輪ECO的時間,保證了項目進度。

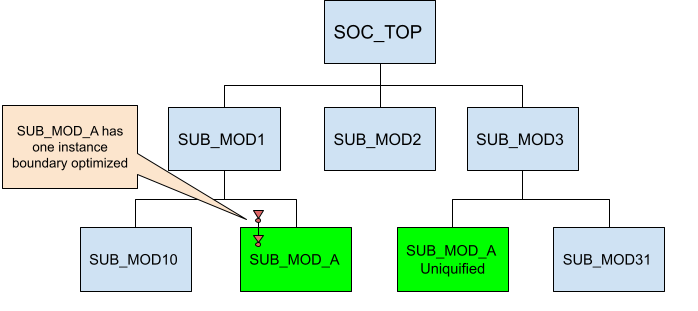

然而,設計時這些子模塊經過了物理綜合、DFT、后端工具等各種優化。模塊例化好幾次時,在這些優化后,每一個實例都會出現很多不同的邊界優化。下圖中,SUB_MOD_A有后端優化,如端口反相。

因此,自動ECO工具必須能夠識別和處理這些各種各種的后端優化,處理好每一個模塊的特有的復雜情況,并精確修理。

面對這種挑戰,GOF中讀入了prelayout網表(綜合+DFT)來更好地處理邊界優化。這其實是可以實現的,我們知道prelayout網表,在做ECO之前,應該與綜合網表等價。

在ECO時,為了提取出子模塊的邊界優化,我們用prelayout網表與老APR網表來做對比。因為ECO作用于各個子模塊,相應的邊界優化信息又被反標到網表上,這保證了ECO的精度和準確性,又能保證頂層設計的邏輯等價PASS。

read_design命令的-ori_syn參數用來加載prelayout網表。下面一段腳本,先用SUB_MOD_A作參考fix SUB_MOD_A_0,再接著修理SUB_MOD_A_1。最后把頂層設置到SOC_TOP,寫出ECO網表。

read_design('-ref', "new_sub_mode_a.gv"); # New synthesized sub-module-A

read_design('-imp', "post_layout.gv"); # Full post layout netlist

read_design('-ori_syn', "pre_layout.gv"); # Full prelayout, equal to post_layout.gv

# Apply ECO to the first instance

set_top_ref("SUB_MOD_A"); # Must set REF scope

set_top("SUB_MOD_A_0"); # Uniquified name for the first instance

fix_design;

# Apply ECO to the second instance

set_top_ref("SUB_MOD_A"); # Must set REF scope

set_top("SUB_MOD_A_1"); # Uniquified name for the second instance

fix_design;

set_top("SOC_TOP");

report_eco();

write_verilog("post_layout.eco.gv"); # Full post layout netlist after ECO

可以處理完整網表的ECO,但不需要對整個設計重新綜合,這就會格外地節省時間。由于GOF提取出了邊界信息,ECO的結果就會有更高的準確程度。

審核編輯:劉清

-

SoC設計

+關注

關注

1文章

148瀏覽量

18774 -

DFT

+關注

關注

2文章

231瀏覽量

22712

原文標題:大型SOC設計中的功能ECO加速的解決方案

文章出處:【微信號:ExASIC,微信公眾號:ExASIC】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

一種面向LTE基站的SOC平臺軟件解決方案

一種基于FPGA的圖神經網絡加速器解決方案

一種高效的UPS電源解決方案

Magma推出面向大型SoC的增強版層次化設計規劃解決方案

ECO技術在SoC芯片設計中的應用

分享一種大型SOC設計中功能ECO加速的解決方案

分享一種大型SOC設計中功能ECO加速的解決方案

評論