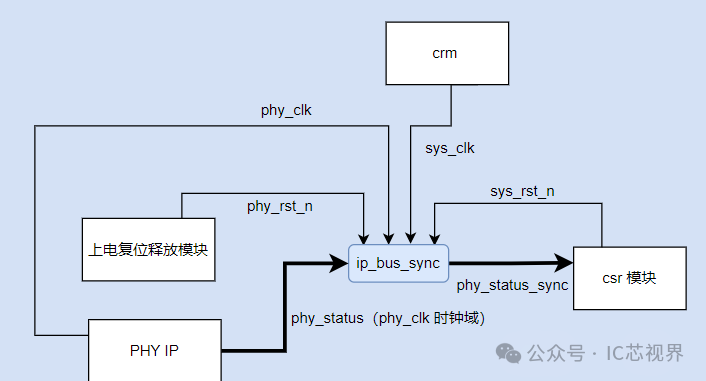

本文將介紹一個跨時鐘錯誤的案例如圖所示,phy_status作為一個多bit的phy_clk時鐘域的信號,需要輸入csr模塊作為一個可讀狀態寄存器,目的是方便debug,而csr模塊是sys_clk時鐘域,此時phy_status需要進行跨時鐘,得到sys_clk時鐘域的phy_status_sync送到csr模塊。

phy_rst_n是由上電復位釋放模塊產生的phy_clk時鐘域的復位信號,在上電處理流程的初期phy_rst_n一直是0,處于復位狀態,上電解復位流程進行到一定階段后才會將phy_rst_n置為1。 ? ? ? ? ?

? ? ? ? ?

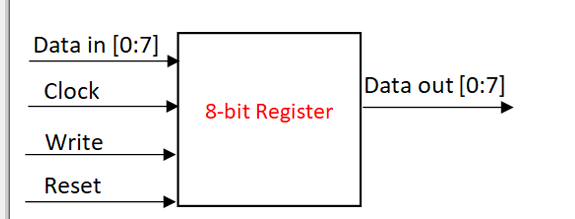

ip_bus_sync跨時鐘模塊接口信號如下: 本模塊的特點就是只有輸入數據,沒有vld信號。

phy_clk作為源時鐘(i_src_clk),而phy_rst_n作為源時鐘域復位信號(i_src_rst_n)。

sys_clk作為目的時鐘(i_dst_clk),而sys_rst_n作為源時鐘域復位信號(i_dst_rst_n)。

NOTE: 需要注意的是在在源時鐘復位phy_rst_n為0時,輸出的o_dst_dout(phy_status_sync)是跨時鐘模塊Ip_bus_sync的復位值(每bit都是0)

| 信號名稱 | 信號IO | 位寬 | 說明 |

| i_src_clk | in | 1 | 源端時鐘 |

| i_src_rst_n | in | 1 | 源時鐘域的復位信號,0表示復位。根據代碼實現不同,可以是同步復位,也可以是異步復位 |

| i_src_din | in | 1 | 源時鐘域bus信號 |

| i_dst_clk | in | 1 | 目的端時鐘 |

| i_dst_rst_n | in | 1 | 目的時鐘域的復位信號,0表示復位。根據代碼實現不同,可以是同步復位,也可以是異步復位 |

| o_dst_dout | out | DATA_WDTH | 已完成跨時鐘的bus信號 |

錯誤設計:設計中將phy_status作為一個可讀狀態寄存器,本意是想在上電解復位流程出現異常的時候,能夠讀出phy_status的數值,從而進行分析上電流程異常的原因。而在部分場景中,一旦phy_rst_n沒有從0跳變成1時,此時phy_status_sync為0,無法獲取phy_status的真實數值 。

正確設計:本文場景中應該采用無復位的跨時鐘模塊進行實現,如果存在可用的無復位多bit跨時鐘模塊,可以直接采用,否則可以考慮采用多個無復位的bit跨時鐘模塊實現。雖然采用多個無復位的bit跨時鐘模塊實現多bit跨時鐘可能存在重匯聚問題,但是此場景中,一旦出現上電解復位異常,phy_status信號通常是處于穩定狀態,多bit跨時鐘重匯聚問題將不會存在。

審核編輯:劉清

-

寄存器

+關注

關注

31文章

5437瀏覽量

124728 -

IC設計

+關注

關注

38文章

1361瀏覽量

105878 -

PHY

+關注

關注

2文章

325瀏覽量

52897 -

CLK

+關注

關注

0文章

128瀏覽量

17630

原文標題:IC設計錯誤案例:可讀debug寄存器錯誤跨時鐘

文章出處:【微信號:IP與SoC設計,微信公眾號:IP與SoC設計】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

跨時鐘域為什么要雙寄存器同步

ARM Cortex-M 系列 MCU 錯誤追蹤庫 --- CmBacktrace

為調試寄存器 DBGDRAR 設置的值錯誤

虹科干貨 | 帶你全面認識“CAN總線錯誤”(一)——CAN總線錯誤與錯誤幀

CAN總線錯誤分析與解決 CAN節點發送錯誤不成功是什么原因

【答疑】網關返回錯誤?Modbus地址與寄存器地址別混淆!

評論