AnaPico公司的APPH系列相噪分析儀以-190dBc/Hz的本底噪聲和小于5fs本底抖動(dòng)而具有極高的靈敏度,能夠以高于時(shí)域抖動(dòng)的靈敏度測(cè)量頻域中的相位噪聲并及其便利的轉(zhuǎn)換為對(duì)應(yīng)的抖動(dòng)數(shù)值。

APPH相位噪聲分析儀

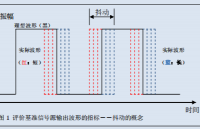

APPH相位噪聲分析儀抖動(dòng)(Jitter):反映的是數(shù)字信號(hào)偏離其理想位置的時(shí)間偏差。高頻數(shù)字信號(hào)的bit周期都非常短,一般在幾百ps甚至幾十ps,很小的抖動(dòng)都會(huì)造成信號(hào)采樣位置電平的變化,所以高頻數(shù)字信號(hào)對(duì)于抖動(dòng)都有嚴(yán)格的要求。

實(shí)際信號(hào)可能具有較高復(fù)雜性,比如既有隨機(jī)抖動(dòng)成分(RJ),也有不同頻率的確定性抖動(dòng)成分(DJ)。確定性抖動(dòng)可能由于碼間干擾或一些周期性干擾引起,而隨機(jī)抖動(dòng)很大一部分來源于信號(hào)上的噪聲。一般我們把數(shù)字信號(hào)超過閾值的狀態(tài)判決為“1”,把低于閾值的狀態(tài)判決為“0”,由于信號(hào)的上升沿不是無限陡的,所以垂直的幅度噪聲就會(huì)造成信號(hào)過閾值點(diǎn)時(shí)刻的左右變化,這就是由于噪聲造成信號(hào)抖動(dòng)的原因。

要進(jìn)行信號(hào)抖動(dòng)的分析,最常用的工具是寬帶示波器配合上響應(yīng)的抖動(dòng)分析軟件。示波器里的抖動(dòng)分析軟件可以方便地對(duì)抖動(dòng)的大小和各種成分進(jìn)行分解,但是,現(xiàn)在很多高速芯片對(duì)時(shí)鐘的抖動(dòng)要求都在1ps以下甚至fs級(jí)。這就需要借助于其它的測(cè)量方法,比如相位噪聲(phase noise)的測(cè)量方法。

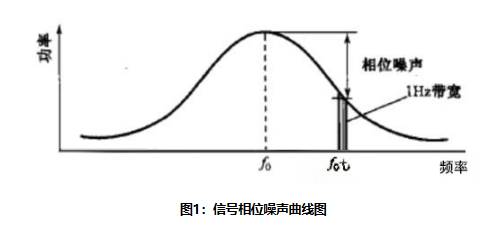

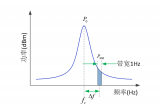

相位噪聲:在頻域上,數(shù)據(jù)偏移量用相位噪聲來定義。對(duì)于頻率為f0的時(shí)鐘信號(hào)而言,如果信號(hào)上不含抖動(dòng),則信號(hào)的所有功率應(yīng)集中在頻率點(diǎn)f0處,由于任何信號(hào)都存在抖動(dòng),這些抖動(dòng)有些是隨機(jī)的,有些是確定的,分布于相當(dāng)廣的頻帶上,因此抖動(dòng)的出現(xiàn)將使信號(hào)功率被擴(kuò)展到這些頻帶上。信號(hào)的相位噪聲,就是信號(hào)在某一特定頻率處的功率分量,將這些分量連接成的曲線就是相位噪聲曲線。相位噪聲通常定義為在某一給定偏移處的dBc/Hz值,其中dBc是以dB為單位的該功率處功率與總功率的比值。如一個(gè)振蕩器在某一偏移頻率處的相位噪聲定義為在該頻率處1Hz帶寬內(nèi)的信號(hào)功率與信號(hào)總功率的比值,即在fm頻率處1Hz范圍內(nèi)的面積與整個(gè)噪聲頻率下的所有面積之比。

從相位噪聲曲線圖1可知,絕大多數(shù)抖動(dòng)都集中在頻率f0附近,距離f0越遠(yuǎn)的頻段,抖動(dòng)能量越小。

以下面的例子為例,說明對(duì)時(shí)鐘輸入的要求:

RMS JPER(12kHz~20MHz):0.5ps

相位噪聲(10~100kHz):-120dBc/Hz

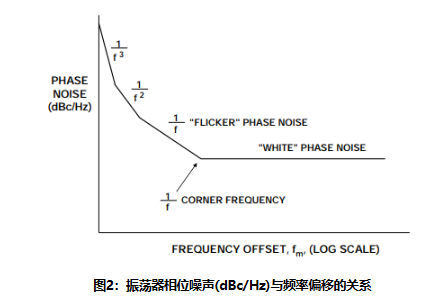

通常用單邊帶相位噪聲來描述振蕩器的特性,如圖2的相位噪聲(dBc/Hz)與頻率偏移fm的關(guān)系曲線所示,其中頻率軸采用對(duì)數(shù)刻度。注意,實(shí)際的曲線由多個(gè)區(qū)域擬合而成,各區(qū)域的斜率為1/fx,x=0對(duì)應(yīng)于“白色”相位噪聲區(qū)域(斜率=0dB/10倍),x=1對(duì)應(yīng)于“閃爍”相位噪聲區(qū)域(斜率=–20dB/10倍)還存在x=2、3、4的區(qū)域,這些區(qū)域依次出現(xiàn),愈來愈接近載波頻率。

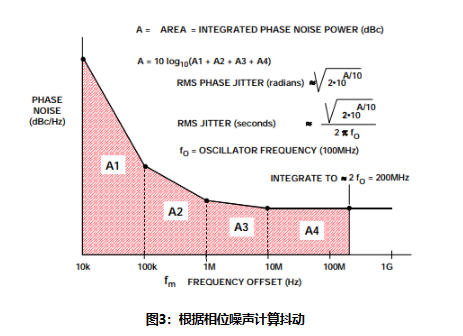

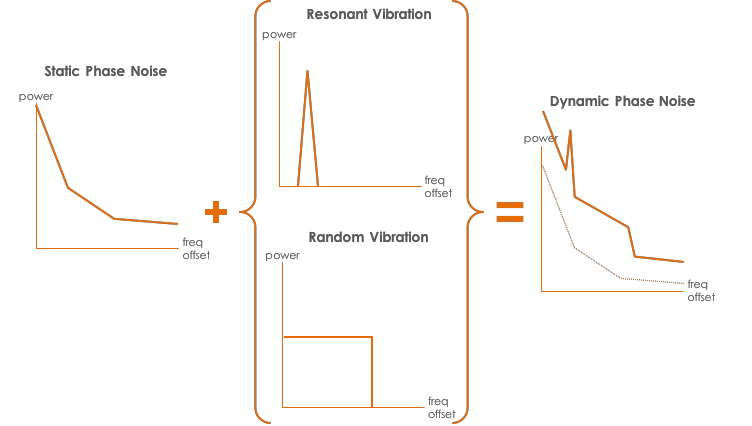

我們已經(jīng)看到,振蕩器通常用相位噪聲來描述性能,但為了將相位噪聲與ADC的性能關(guān)聯(lián)起來,必須將相位噪聲轉(zhuǎn)換為抖動(dòng)。為將該曲線與現(xiàn)代ADC應(yīng)用關(guān)聯(lián)起來,選擇100MHz 的振蕩器頻率(采樣頻率)以便于討論,典型曲線如圖3所示。請(qǐng)注意,相位噪聲曲線由多條線段擬合而成,各線段的端點(diǎn)由數(shù)據(jù)點(diǎn)定義。

計(jì)算等效rms抖動(dòng)的第一步是獲得目標(biāo)頻率范圍(即曲線區(qū)域A)內(nèi)的積分相位噪聲功率。該曲線被分為多個(gè)獨(dú)立區(qū)域(A1、A2、A3、A4),各區(qū)域由兩個(gè)數(shù)據(jù)點(diǎn)定義。一般而言,假設(shè)振蕩器與ADC輸入端之間無濾波,則積分頻率范圍的上限應(yīng)為采樣頻率的2倍,這近似于ADC采樣時(shí)鐘輸入的帶寬。

積分頻率范圍下限的選擇也需要一定的斟酌。理論上,它應(yīng)盡可能低,以便獲得真實(shí)的rms抖動(dòng)。但實(shí)際上,制造商一般不會(huì)給出偏移頻率小于10Hz時(shí)的振蕩器特性,不過這在計(jì)算中已經(jīng)能夠得出足夠精度的結(jié)果。多數(shù)情況下,如果提供了100Hz時(shí)的特性,則選擇100Hz作為積分頻率下限是合理的。否則,可以使用1kHz或10kHz數(shù)據(jù)點(diǎn)。

還應(yīng)考慮,“近載波”相位噪聲會(huì)影響系統(tǒng)的頻譜分辨率,而寬帶噪聲則會(huì)影響整體系統(tǒng)信噪比。最明智的方法或許是對(duì)各區(qū)域分別積分,并檢查各區(qū)域的抖動(dòng)貢獻(xiàn)幅度。如果使用晶體振蕩器,則低頻貢獻(xiàn)與寬帶貢獻(xiàn)相比,可能可以忽略不計(jì)。其它類型的振蕩器在低頻區(qū)域可能具有相當(dāng)大的抖動(dòng)貢獻(xiàn),必須確定其對(duì)整體系統(tǒng)頻率分辨率的重要性。

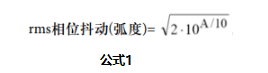

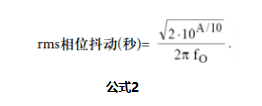

各區(qū)域的積分產(chǎn)生個(gè)別功率比,然后將各功率比相加,并轉(zhuǎn)換回dBc。一旦知道積分相位噪聲功率,便可通過下式計(jì)算rms相位抖動(dòng)(單位為弧度)

以上結(jié)果除以2πfO,便可將用弧度表示的抖動(dòng)轉(zhuǎn)換為用秒表示的抖動(dòng)。

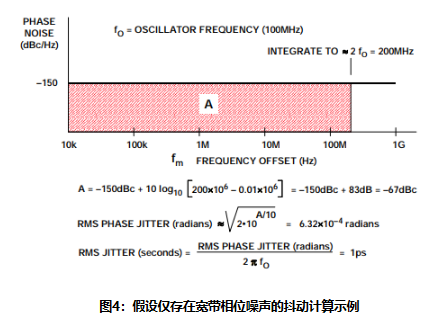

圖4給出了一個(gè)計(jì)算示例,它假設(shè)僅存在寬帶相位噪聲。所選的–150dBc/Hz寬帶相位噪聲代表了良好信號(hào)發(fā)生器的特性,由此獲得的抖動(dòng)值可以代表實(shí)際情況。–150dBc/Hz的相位噪聲(用比值表示)乘以積分帶寬(200MHz),得到–67dBc的積分相位噪聲。請(qǐng)注意,該乘法相當(dāng)于把10log10[200MHz–0.01MHz]的量與相位噪聲(dBc/Hz)相加。實(shí)際上,計(jì)算中可以丟棄0.01MHz的頻率下限,因?yàn)樗粫?huì)對(duì)最終結(jié)果產(chǎn)生重大影響。利用公式2可知, 總rms抖動(dòng)約為1ps。

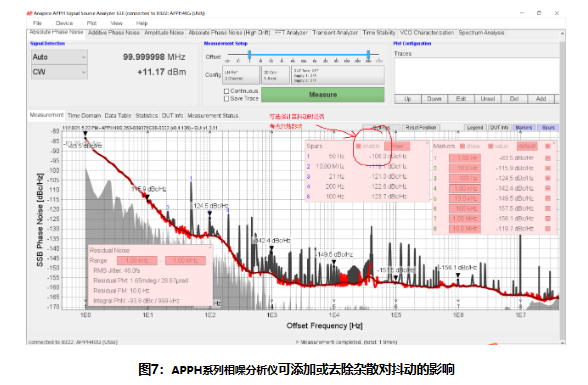

在實(shí)際測(cè)試中,抖動(dòng)值的來源除了相位噪聲還要包含信號(hào)雜散,因此實(shí)際換算時(shí)必須把所有因素考慮進(jìn)去。AnaPico的APPH系列相位噪聲分析儀可以進(jìn)行絕對(duì)相位噪聲測(cè)試時(shí)將這些因素綜合考慮或單獨(dú)考慮。

結(jié)論:相位噪聲和抖動(dòng)是對(duì)同一種現(xiàn)象的兩種不同的定量方式(描述)。抖動(dòng)是一個(gè)時(shí)域概念,單位是ps或fs。相位噪聲是頻率域的概念,相位噪聲是用偏移頻率fm處1Hz帶寬內(nèi)的矩形的面積, 與整個(gè)功率譜曲線下包含的面積之比表示的,單位為-dBc/Hz。隨著現(xiàn)代數(shù)字系統(tǒng)的時(shí)鐘頻率越來越高,對(duì)高速芯片對(duì)時(shí)鐘的抖動(dòng)要求都在1ps以下甚至fs級(jí)。示波器已經(jīng)無法滿足相關(guān)的測(cè)試要求,因此必須采用靈敏度更高的相位噪聲分析儀。AnaPico公司的APPH系列相噪分析儀以-190dBc/Hz的本底噪聲和小于5fs本底抖動(dòng)而具有極高的靈敏度,能夠以高于時(shí)域抖動(dòng)的靈敏度測(cè)量頻域中的相位噪聲并及其便利的轉(zhuǎn)換為對(duì)應(yīng)的抖動(dòng)數(shù)值。

-

芯片

+關(guān)注

關(guān)注

459文章

52006瀏覽量

434459 -

相位噪聲測(cè)量

+關(guān)注

關(guān)注

0文章

3瀏覽量

6075

發(fā)布評(píng)論請(qǐng)先 登錄

EMC 時(shí)鐘信號(hào)的噪聲源頭是什么?

請(qǐng)問如何根據(jù)相位噪聲求取相位噪聲的功率譜密度?

電源軌噪聲對(duì)系統(tǒng)時(shí)鐘抖動(dòng)的影響

數(shù)字鎖相環(huán)固有的相位抖動(dòng)是怎樣產(chǎn)生的,如何解決

數(shù)字振蕩器的相位噪聲是多少

時(shí)鐘抖動(dòng)與相位噪聲的關(guān)系

抖動(dòng)與相位噪音的基礎(chǔ)知識(shí)

鎖相環(huán)相位噪聲的影響因素

相位噪聲對(duì)收發(fā)信機(jī)的影響

高速信號(hào)傳輸中的抖動(dòng)和眼圖挑戰(zhàn)

振蕩器動(dòng)態(tài)相位噪聲優(yōu)化的四步實(shí)操指南

評(píng)論