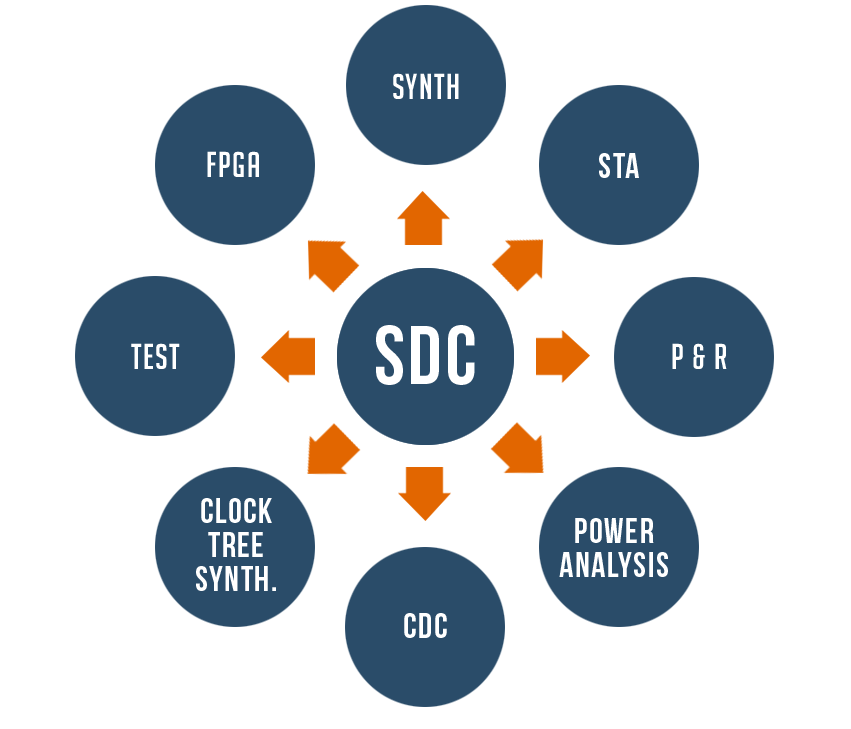

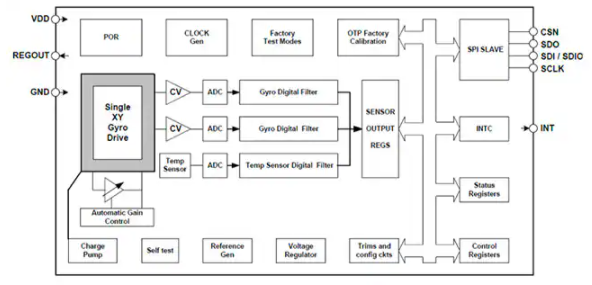

SOC設計變得越來越復雜,成本越來越高,設計和驗證也越來越困難。設計尺寸、眾多的IP、先進技術節點、時鐘和時鐘域數量的增加,以及multi-mode/multi-coner組合中為時序收斂造成設計約束變得越來越復雜。為高效的應對復雜的設計約束,需要一個完整的產品來生成、管理,整合和驗證與靜態時序分析引擎相關的設計約束,以確保設計的正確性。

在約束、時鐘或時序方面的錯誤所造成的巨大代價通常迫使設計團隊采取最小化策略——設計一個完全最小的、安全的、最不容易出錯的時序約束集合。設計領域經驗豐富的領導者認識到這是一個復雜的、多方面的問題,需要各種能力和技術來解決。簡單的結構或語義工具和方法只能捕獲簡單的問題,而且會產生大量的誤報信息,需要設計人員進行檢查。一個完善的解決方案應該是輔助和幫助設計團隊創建設計約束條件,覆蓋設計需求,使其滿足功耗、性能和面積目標,同時最小化由于時鐘或時序問題而導致的其他風險。

為解決上述問題,Excellicon公司提供了Conman和Concert的組合解決方案,來幫助設計公司應對各種在設計中出現的SDC問題。

Conman:設計約束文件的編譯和管理

ConMan是第一個商用的形式化設計約束編譯器工具,它可以自動為任何層次結構和SoC的任何模式生成SDC,從而大大縮短了時序收斂的周期。ConMan提供了一種直觀的方法,可以自動編譯和管理針對于不同設計的sign off質量級別的、構造及正確的時間約束文件,且工具已經通過ISO2626認證。

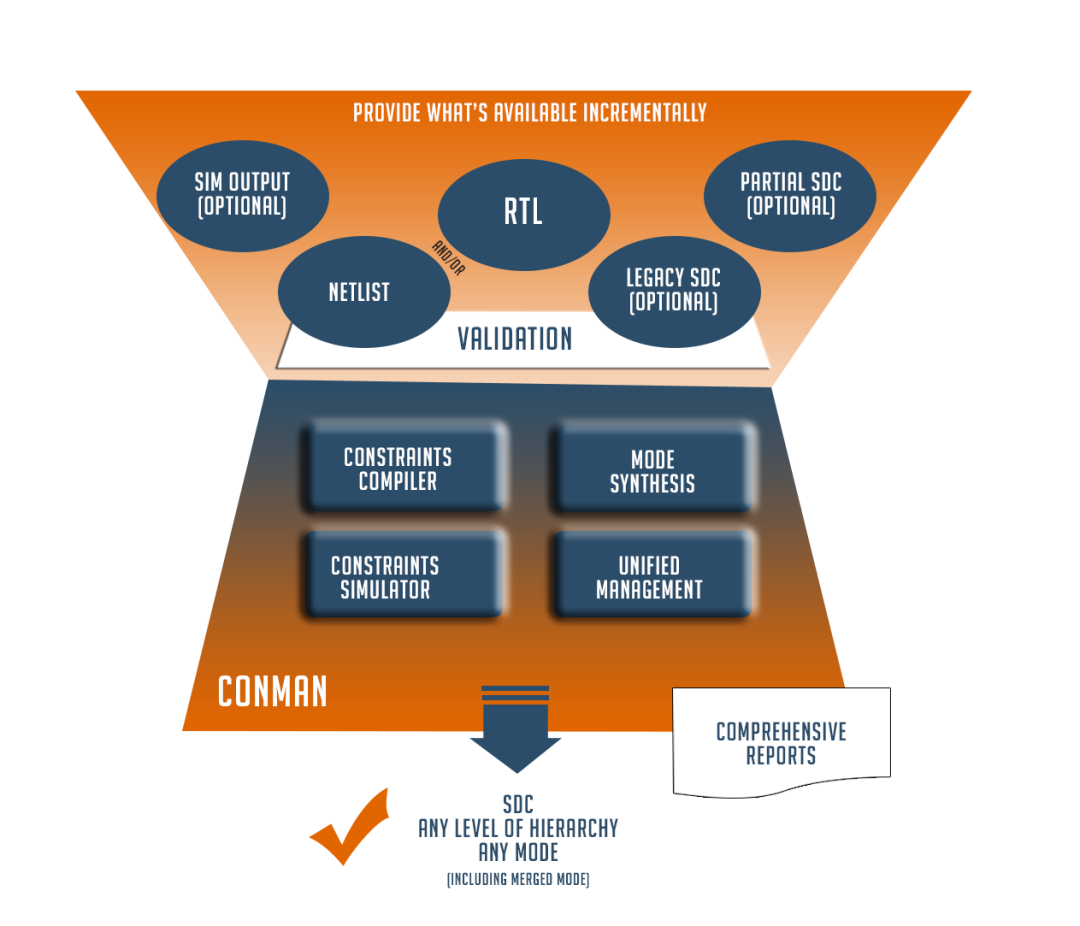

ConMan還通過在設計周期的早期將前端與后端對齊來重新定義時序約束,從而消除了仿真測試中假設的時序與SDC文件中用于實現時序之間的斷層。 ConMan生成并維護單一數據源,供前端和后端設計人員使用,以捕獲、生成和管理所有操作模式的設計時序約束,同時在設計的所有階段向設計人員提供反饋。使用ConMan,設計人員可以從前端工程師開始RTL開發,一直到后端團隊的實現階段,開始生成時序約束。所有信息通過ConMan跟蹤,并可以通過報告或可視化的模擬計時數據進行查看。

設計人員可以手動提供時序信息,也可以選擇從舊的SDC或通過設計層次結構的任何塊的仿真結果提取時序信息。ConMan使用其強大的形式化符號仿真引擎自動驗證所有的輸入數據,然后在設計層次結構中組裝和傳播所有的時序數據,解決時序沖突,并在需要時向設計師提供數據以進一步細化。

ConMan平臺包含以下組件:

僅以RTL或gate作為輸入的多模式約束生成Multi-Mode Constraints

約束管理

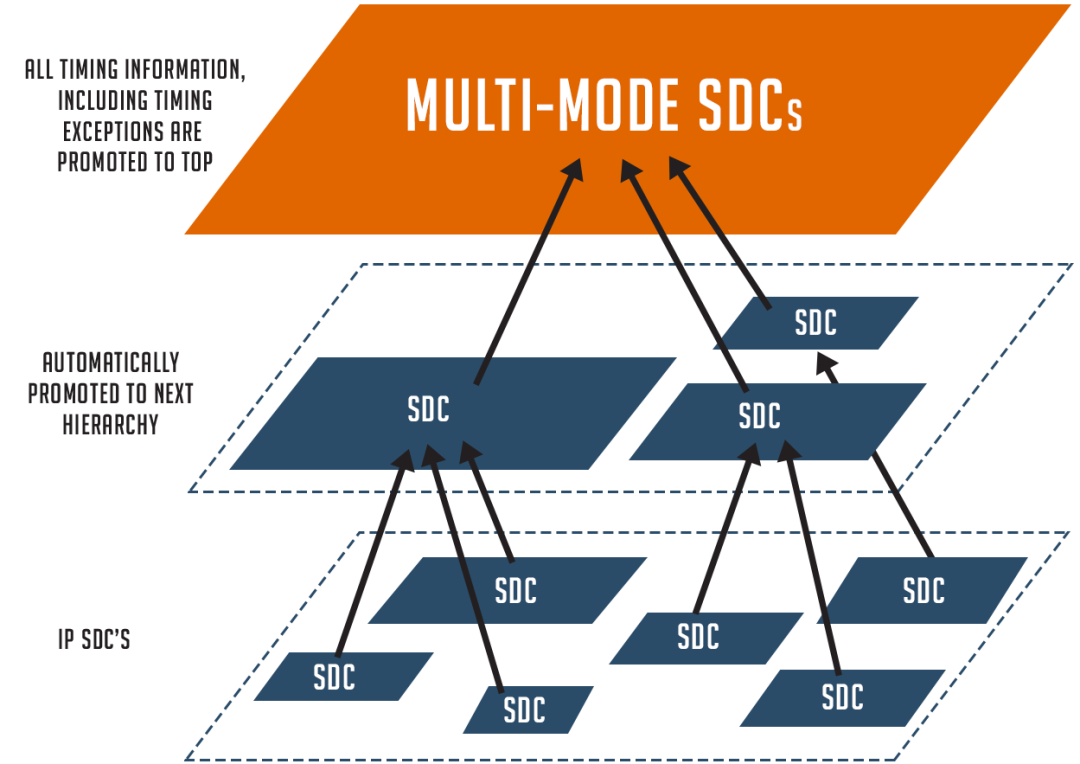

約束設定的提升(promotion)

時鐘可視化與分析

Multi-Mode Constraints Generation

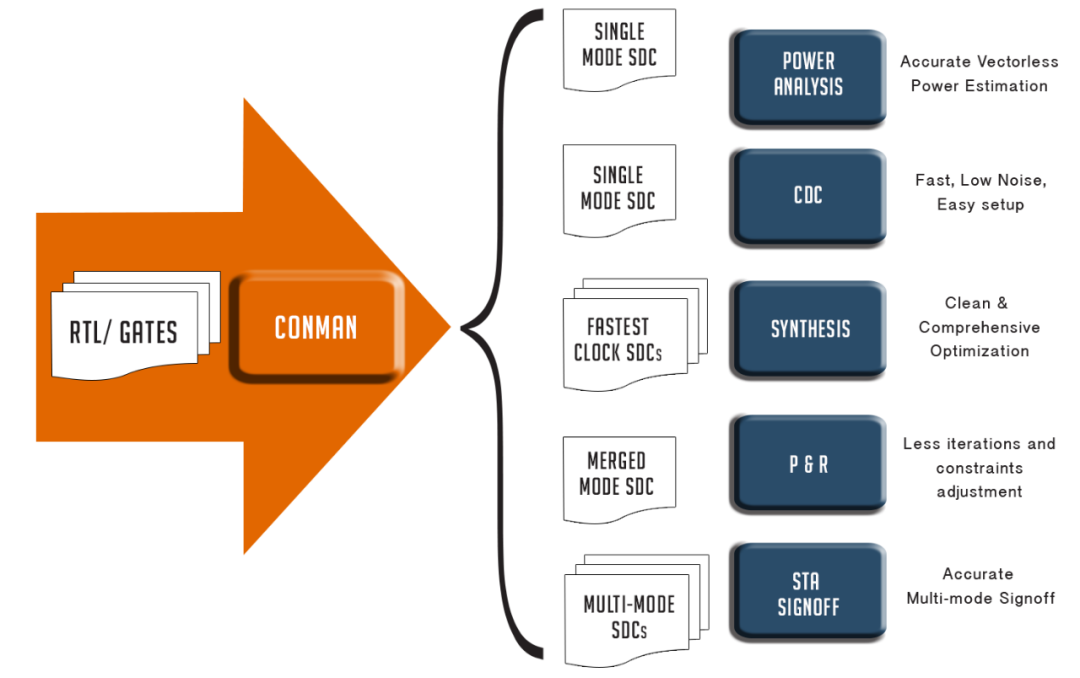

ConMan生成SDC格式的全面時序約束,適用于任何設計層次和任何模式。不需要SDC語法知識。

sdc用于任何層次結構,任何模式和任何類型- RTL或Gates

不同類型:單模式,合并模式-層次化或者扁平化100%發現所有時鐘和模式引腳

完整的SDC時序約束,包含時鐘,時序異常,Case Analysis,IO延遲,時鐘組,drc等。

單數據庫多模式,RTL和Gate的時序約束

約束管理

約束管理

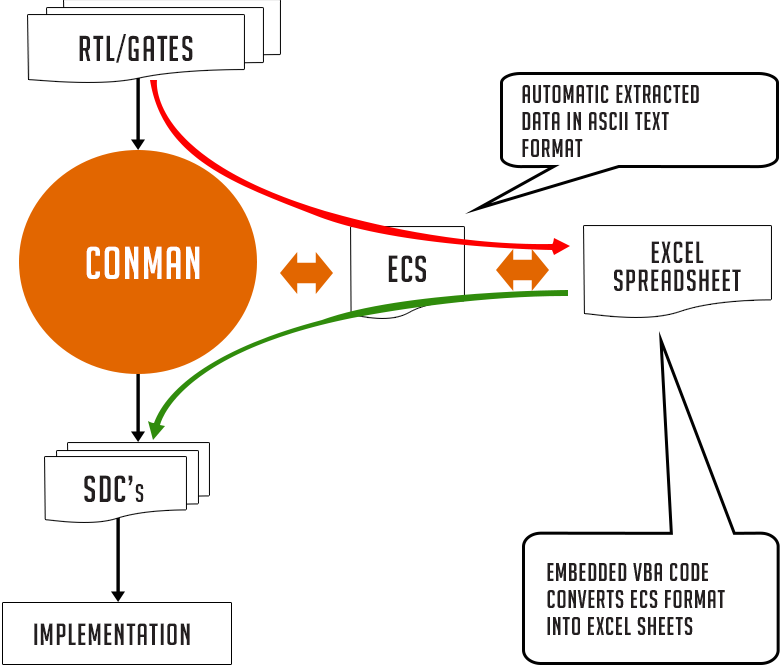

ConMan提供了Excel的無縫接口,通過該接口,所有的時序約束都可以在工具外部進行管理或修改。這種雙向接口允許設計師使用熟悉的Excel電子表格格式來檢查時序數據,并在需要時修改它。

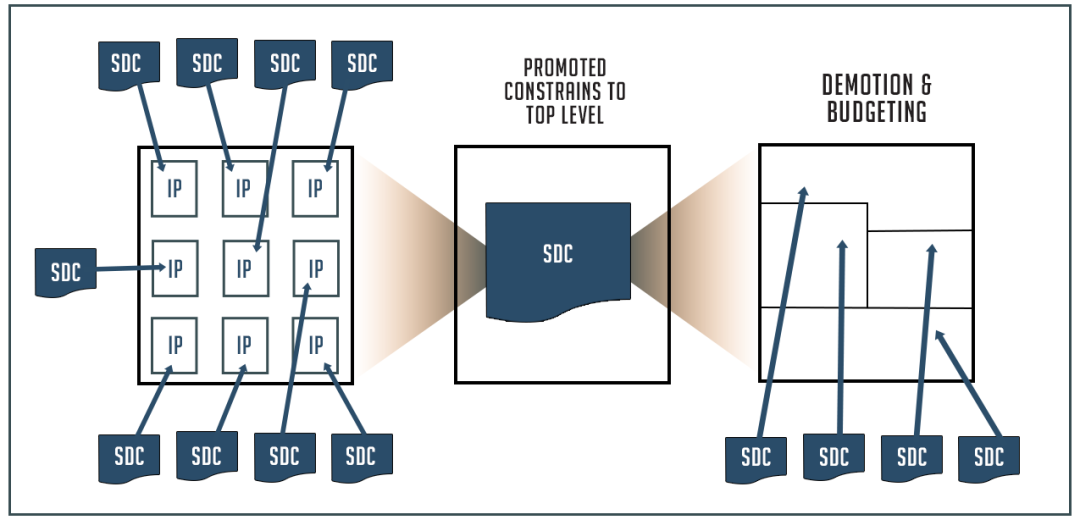

約束條件的提升(Promotion)

目前,約束的大多數傳播都是使用操作層次分隔符的手工方法完成的。這種技術增加了在編輯過程中引入錯誤和丟失約束的風險。Excellicon的多傳播功能不僅自動化方式節省設計師手工編輯數據需要花費數周的過程,而且還為設計師提供了很大的靈活性來處理他們可能遇到的任何情況,既然他們試圖生成適當的高質量的約束。

ConMan提供了三種技術,用于將較低級別的時序約束提升到層次結構的任何層。支持混合使用這三種方法。

集成方法- IP時序約束允許改變作為頂層設計結構的結果

隔離方法—IP時序約束保持原樣。

上下文方法——頂層和低級別的約束都可用,但它們不在彼此的上下文中。隨著設計者定義和指導的時序約束的增量傳播而進行推廣。

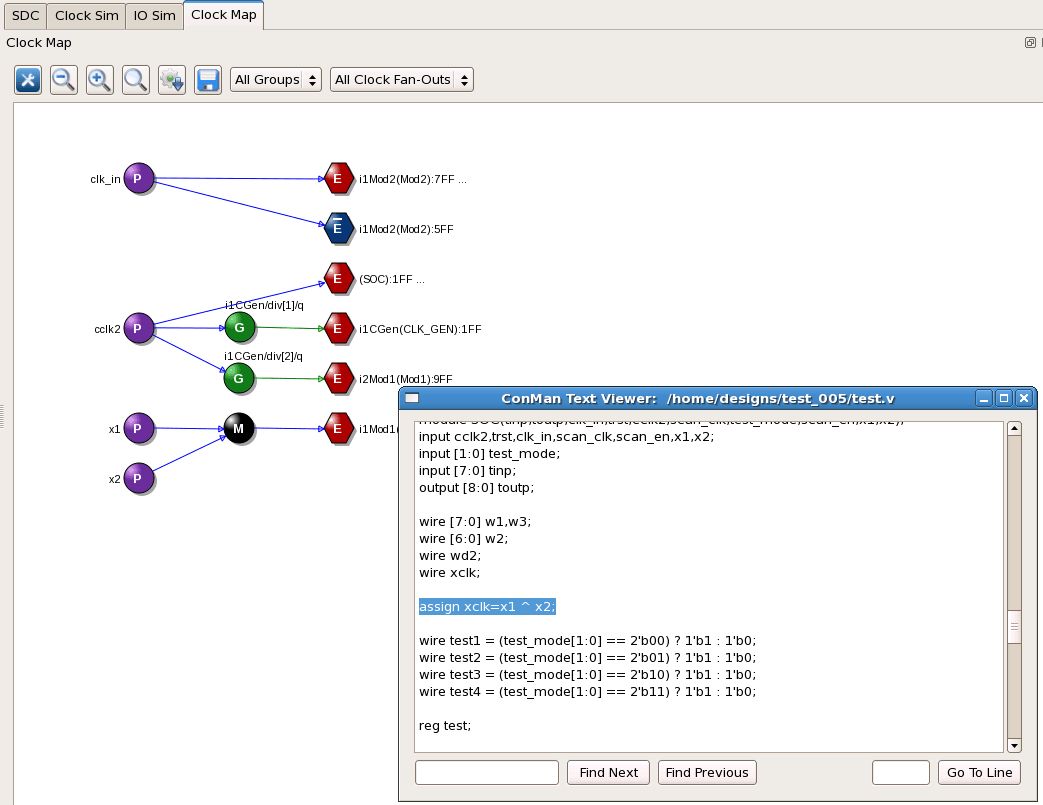

時鐘可視化與分析

理解任何設計的時鐘總是最困難的任務之一,并且非常容易出錯。現有的解決方案繪制了一個完整的邏輯示意圖,從其中識別時鐘邏輯不僅是困難的,有時是不可能的。

ConMan利用一種直觀的抽象方法來顯示時鐘圖(自動從HDL中提取),從中設計者可以快速理解任何層次結構、全平面或分層視圖的時鐘邏輯。此外,ConMan使用其正式引擎使設計人員能夠執行時鐘傳播的“假設”分析,以創建不同的操作模式。

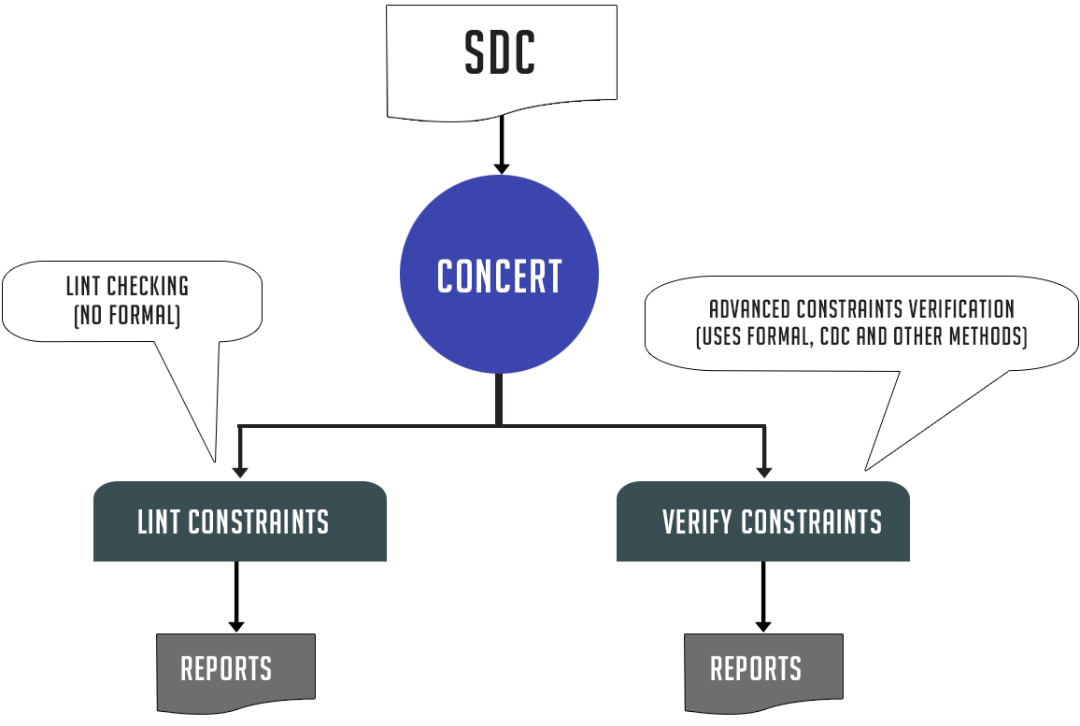

ConCert :約束證明平臺

ConCert 是一個sign off平臺,為 ASIC/SOC 或 FPGA 流程的任何階段的提供時序約束驗證、降級(Demotion)和預算(Budgeting)獨一無二的系統。

ConCert 平臺包含以下組件:

約束驗證

Exception工具箱

Demotion和Budgeting工具箱

等價檢查

設計分析

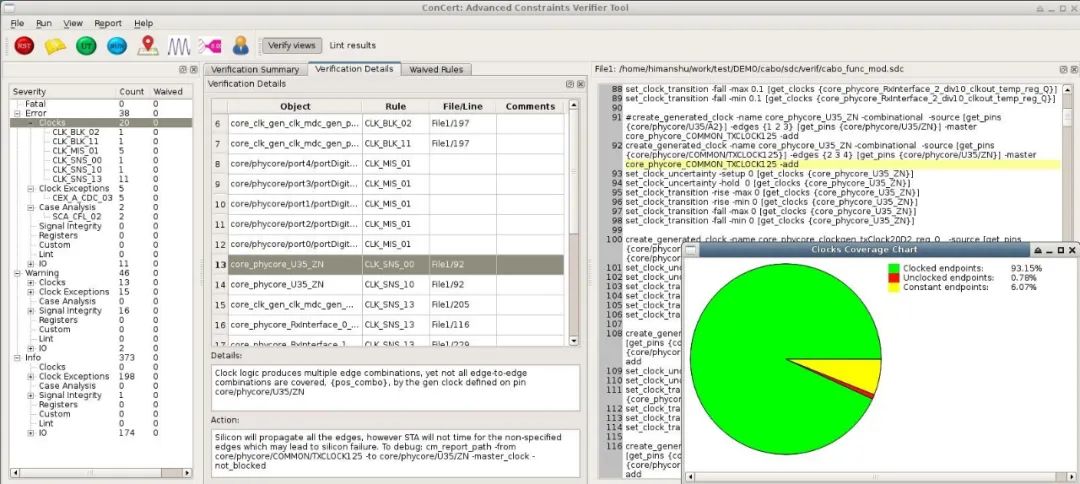

約束驗證

ConCert 使用形式化算法來驗證時序約束,從而提供對設計及其相關時序約束的準確深入分析。ConCert 的約束驗證方法不同于當今市場上可用的傳統工具。傳統工具主要是通過使用數千條規則來關注語法和基本正確性的 SDC linter。這總是會在輸出報告中產生大量噪音。此外,時序意圖丟失并且無法通過此類傳統工具進行分析。

ConCert 除了 linting 之外,還利用其形式化引擎來分析設計和 SDC 文件的行為。提取設計的時序意圖和相關的 SDC 文件并進行比較,以生成精確的分析報告。這種方法可以消除噪聲輸出,并將約束驗證領域擴展到下一代,遠遠超出語法和基本檢查。

此外,通過 ConCert,設計人員還可以在原始 SDC 缺少約束的情況下生成增量 SDC,或者使 SDC 信號完整性相兼容。

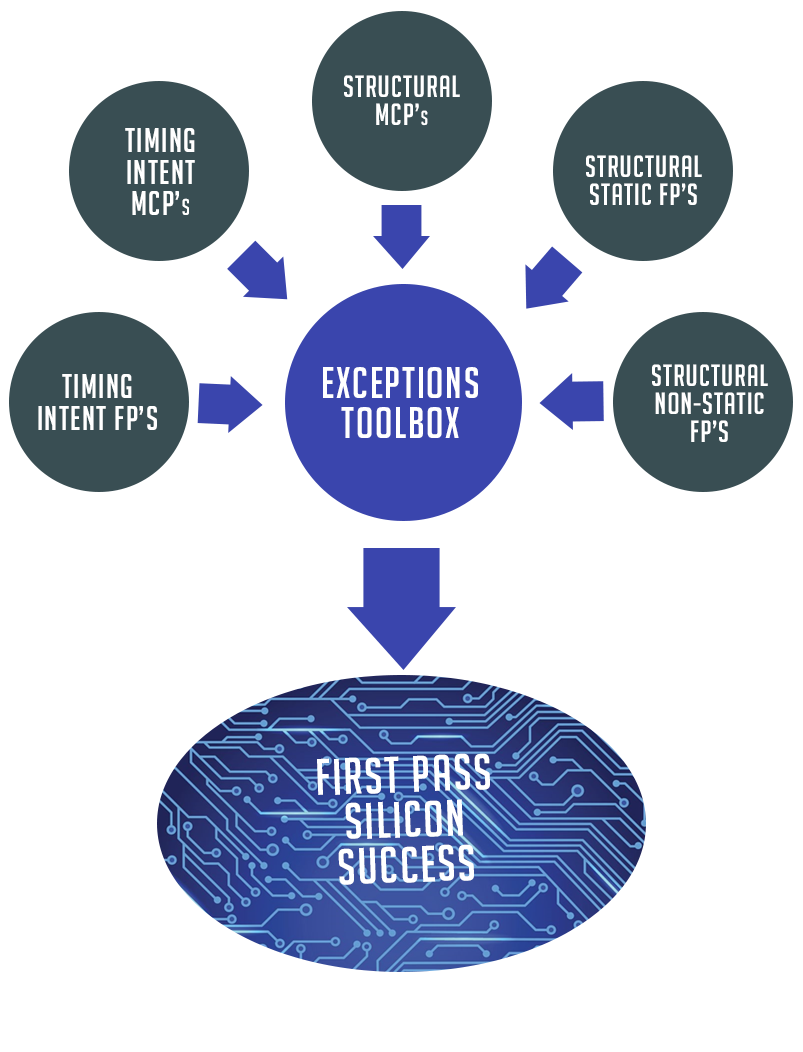

例外工具箱

時序約束文件通常包含大量異常,例如錯誤路徑 (FP) 和多周期路徑 (MCP)。此類例外通常分為“結構”和“時間意圖”例外。結構異常取決于設計結構,可以通過形式化技術進行驗證。然而,時序意圖類型的異常與設計結構無關,即它們基于設計人員的意圖(例如對所有復位引腳設置錯誤路徑約束),因此不能使用形式化技術來驗證它們。

典型時序約束文件中大約 20% 的 FP 和 MCP 異常屬于結構類型。然而,挑戰在于其余 80% 的例外情況,這些例外情況屬于 RTL 設計人員在功能設計時定義的時序意圖性質。由于形式化技術不能用于此類異常,設計人員傳統上通過手動審查約束文件來驗證它們。

ConCert-ET 是 ConCert 的一個插件,是當今市場上唯一的工具,不僅可以通過形式化方式驗證結構異常,還可以使用專有方法驗證時序意圖類型的異常。

約束模擬

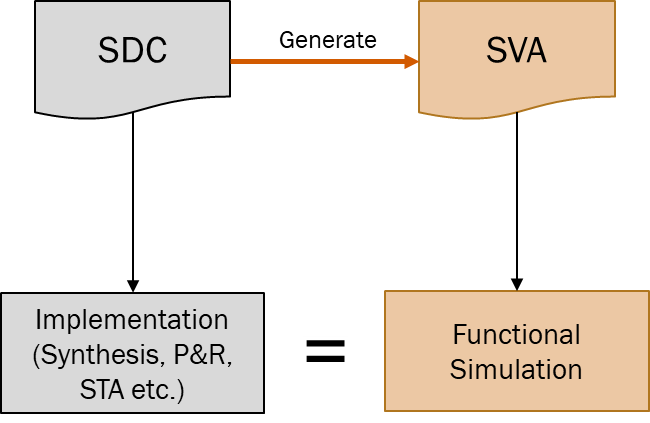

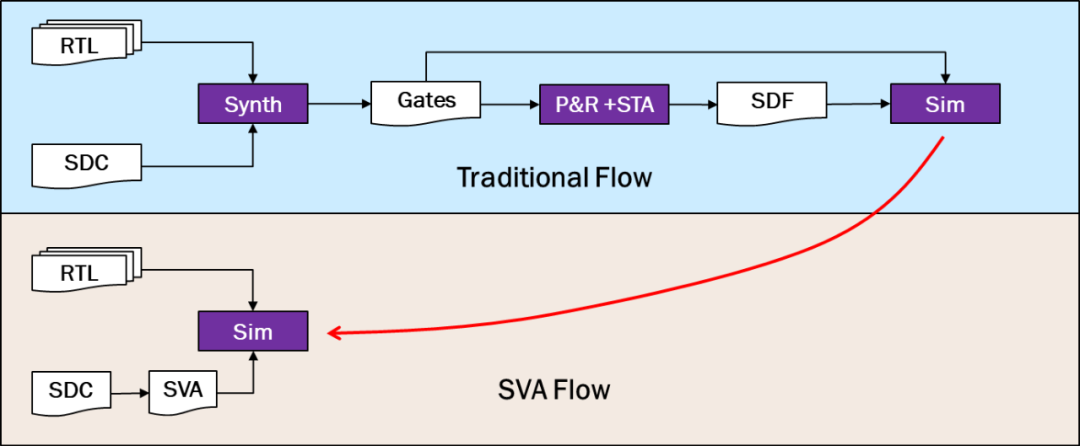

通常,對 RTL 進行仿真以確保功能正確性。與設計相關的時序以 SDC 格式捕獲,與 RTL 功能無關。設計的兩個方面,即功能和時序,僅在設計周期后期執行 SDF 反標的GLS仿真時才對齊。

即使有了約束驗證工具、LEC、STA、CDC 分析和故障分析工具等靜態工具的可用性,人們仍會假設不需要 GLS。然而,今天不存在可以驗證時序約束的時序意圖性質的 EDA 解決方案。時序意圖是指獨立于設計結構但基于設計者意圖的約束。例如,SDC文件中定義的復雜時鐘波形;或在 SDC 文件中指定的錯誤/多周期路徑不是基于邏輯結構,而是基于設計人員的經驗和只是來指定。

這就需要 GLS 來捕捉這些類型的問題。但是,GLS 的一個主要問題是設置 GLS 環境是一項極其繁瑣的任務。為了規避這些問題并幫助在 ASIC 周期的早期階段仿真設計(無需通過 SDF 進行延遲反標),Excellicon 開發了一種 ABSV(基于斷言的 SDC 驗證)功能,其中相關的時序約束被轉換為可在仿真期間使用的 SVA。

這種方法消除了運行 SDF反標的 GLS 的需要,從而顯著減少了循環迭代時間。SVA 也可以在 RTL 階段進行仿真,從而完全簡化整個流程。

降級和預算

ConCert-BT 是 ConCert 的一個附加組件,使設計人員能夠以從 RTL 到物理實現的不同精度級別執行約束降級(demotion)和分層預算(budgeting)。

該產品具有完整的功能:

約束降級

預算生成

基于百分比

基于邏輯的層次

基于固有單元延遲和布局寄生的延遲

驗證所有設計macros的預算

手動細化預算

根據 STA 時序slack值自動重新分配時序預算

具有每個macros過去的預算歷史進行分層預算管理

使用 ConMan,設計人員可以將 IP 約束提升到頂層,隨后通過 ConCert-BT 可以將約束降級到 P&R 活動的宏觀層面。ConCert-BT 在配置工具以選擇性地降級某些約束或自動降級所有約束方面提供了充分的靈活性。

隨著設計在物理實現過程的趨于穩定,時序預算也會不斷變化。這包括對 ECO 的 RTL 更改,這可能會導致設計中各個模塊之間的時序不平衡,這需要調整 IO 延遲值以解決macros之間的時序違反問題。設計人員必須找到一種重新分配預算的方法,以解決False路徑的時序問題;手動完成的方式會導致長時間的迭代,并且通常是芯片的次優時序。

由于物理實現工程師團隊在他們自己的模塊上并行工作,接口時序必須考慮準確的預算,以使頂層時序順利通過而沒有任何違反。前端設計人員可以使用 ConCert-BT 在實施周期的早期階段使用基于百分比或基于邏輯的預算生成適當的預算,而后端工程師可以利用最強大的物理預算生成使用平面圖信息進行預算,并在整個時序收斂周期中管理預算,包括創建時序模型,從而在流片前進行最終迭代。

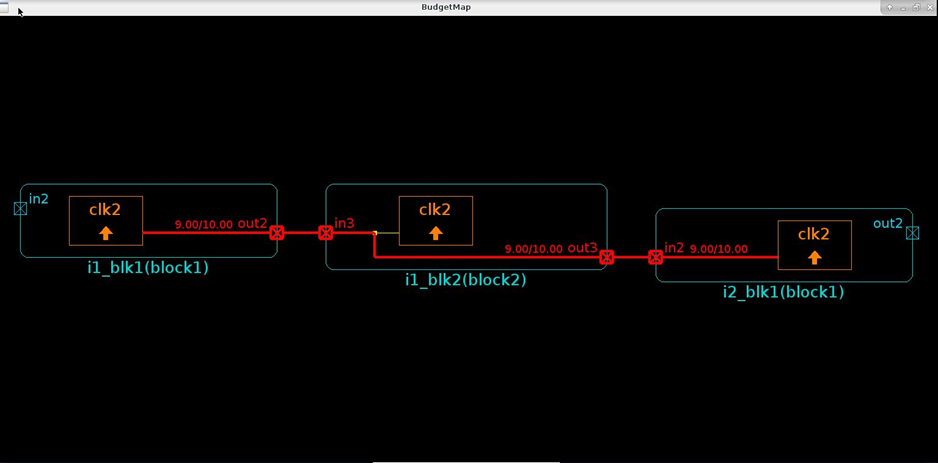

ConCert-BT 提供了一個全面的解決方案,不僅可以跨macros驗證現有預算的正確性,還可以通過其直觀的 Budget Map GUI 顯示預算。通過 BudgetMap,設計人員可以輕松調試失敗的路徑并采取糾正措施。

等價檢查

隨著設計從一個設計階段進展到另一個設計階段,約束總是會發生變化。可能會添加新的約束或修改現有的約束,這可能會導致時序約束不等效并失去最初的意圖。

由于 SoC 是層次化設計的,因此可能存在模塊級時序可能與頂層時序不相關的情況。當執行頂層完全扁平(flatten) STA 時,這可能會出現問題。

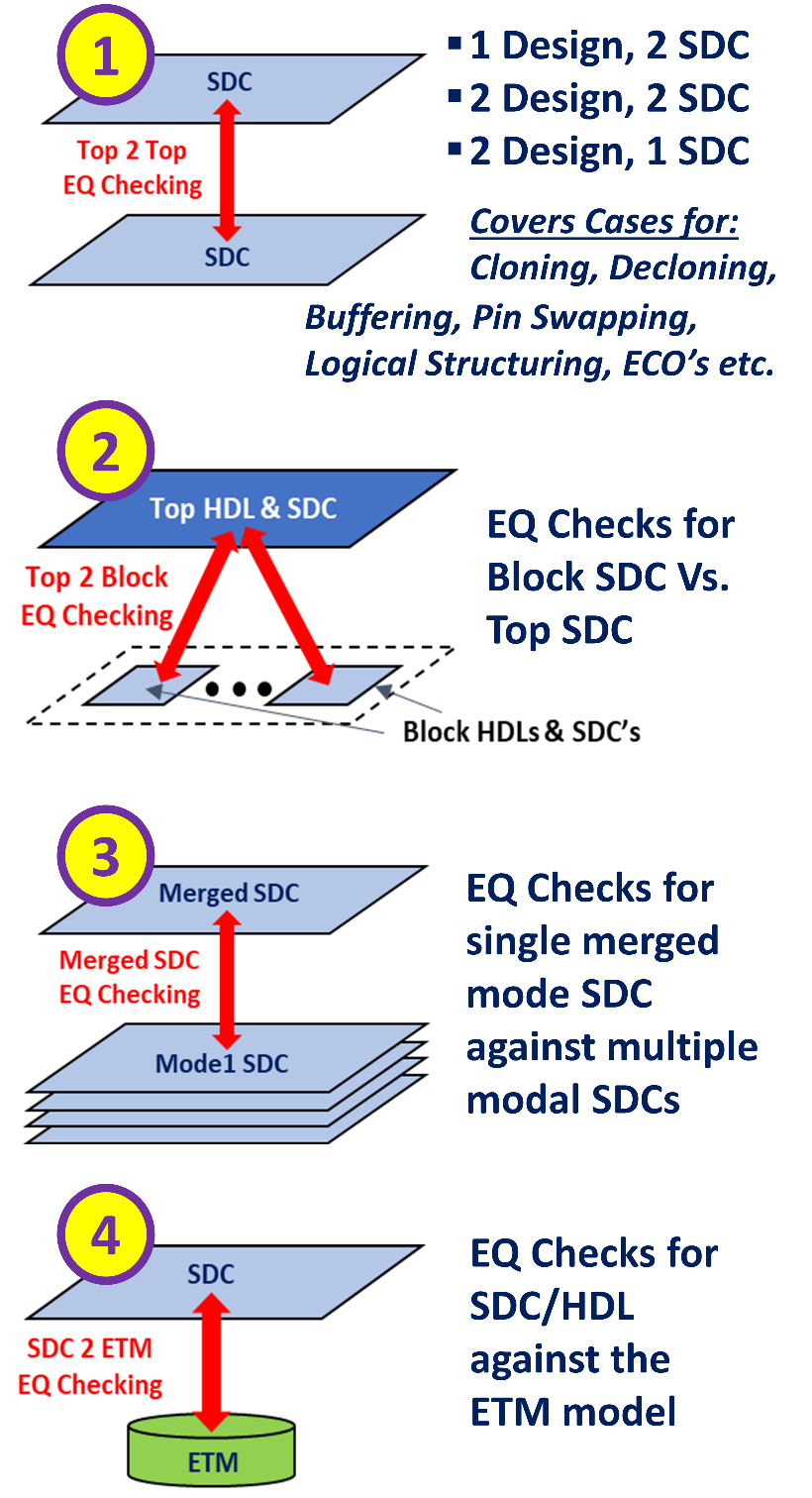

因此,需要證明約束之間的時序等效性。ConCert 提供兩種等效方法:

Top to Top——檢查設計周期不同階段之間的約束等效性

Top to Block – 檢查頂層約束和模塊間的約束等效性

審核編輯:劉清

-

EDA工具

+關注

關注

4文章

267瀏覽量

31785 -

SoC設計

+關注

關注

1文章

148瀏覽量

18774 -

信號完整性

+關注

關注

68文章

1404瀏覽量

95458 -

RTL

+關注

關注

1文章

385瀏覽量

59759 -

SDC

+關注

關注

0文章

48瀏覽量

15534

原文標題:SOC中的SDC約束正變得越來越龐大和復雜,我們該如何應對

文章出處:【微信號:ExASIC,微信公眾號:ExASIC】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

IC datasheet為什么越來越薄了?

藍牙技術越來越雞肋

為什么RF濾波器越來越重要?

如何將Altera的SDC約束轉換為Xilinx XDC約束

黑科技大盤點 機器人已經在我們的生活中越來越普及

不得不承認人類越來越像人工智能了!

自動駕駛供應鏈的關系越來越復雜 成本問題成發展的核心

看門狗功能在 MCU 應用中越來越重要

為什么FPGA在原型驗證中越來越重要

可穿戴設備中的傳感器:尺寸越來越“小”,左右越來越“大”

我們的城市為什么越來越熱?

我們該如何應對SOC中越來越龐大和復雜的SDC約束?

我們該如何應對SOC中越來越龐大和復雜的SDC約束?

評論