FPGA(現場可編程門陣列)的編程主要使用硬件描述語言(HDL),其中最常用的是Verilog HDL和VHDL。

Verilog HDL是一種硬件描述型語言,通過文本的形式來描述數字系統硬件的結構和行為。Verilog HDL應用廣泛,尤其是在美國和日本,其語法與C語言相似,比較靈活,適合用于各種層次的邏輯設計、數字系統的邏輯綜合、仿真驗證和時序分析等。

VHDL(超高速集成電路硬件描述語言)則是一種用于電路設計的高級語言,主要應用在數字電路的領域當中。雖然VHDL的學習可能相對困難一些,但其硬件描述風格與高級計算機語言較為相似。在歐洲,VHDL的使用更為普遍。

除了這兩種主要的HDL,還有一些其他的語言如System Verilog、Xilinx HLS和Chisel等,也可以用于FPGA的編程,但它們并未被廣泛使用。

需要注意的是,雖然有些公司試圖用C語言替代VHDL進行FPGA編程,但由于FPGA的硬件特性,C語言并不適合直接用于FPGA編程。FPGA編程語言屬于硬件編程語言,其設計思路和編程方法與C/C++、Java、Python等計算機編程語言存在顯著差異。因此,在使用FPGA編程語言時,不能照搬軟件設計思路。

總的來說,FPGA的編程主要依賴于特定的硬件描述語言,這些語言能夠精確描述硬件的行為和結構,從而實現FPGA的靈活配置和功能實現。

-

FPGA

+關注

關注

1629文章

21729瀏覽量

602993 -

集成電路

+關注

關注

5387文章

11530瀏覽量

361632 -

Verilog

+關注

關注

28文章

1351瀏覽量

110074

發布評論請先 登錄

相關推薦

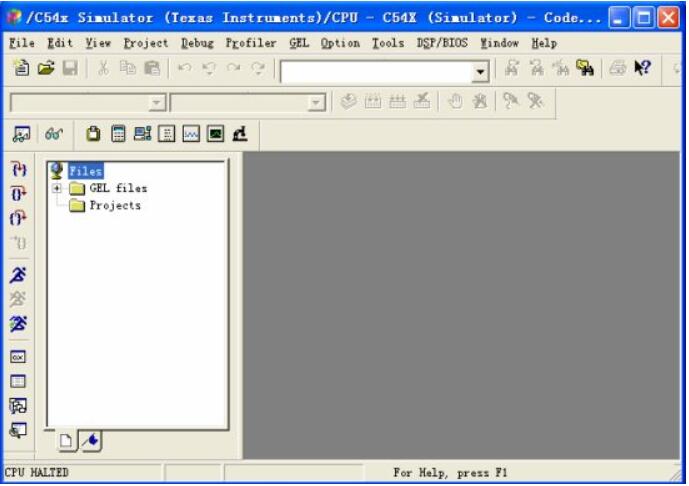

dsp編程用什么語言_dsp編程如何實現的

fpga用什么語言編程

fpga用什么語言編程

評論