FPGA仿真是一種驗證FPGA設計正確性的過程,主要用來分析設計電路邏輯關系的正確性。在FPGA設計中,仿真測試是把FPGA當作一個功能芯片,給一些輸入信號,再觀測輸出信號,看輸出信號是不是設計者想要的信號。這個過程由專門的軟件完成。

FPGA仿真主要分為功能仿真和時序仿真兩類。功能仿真(也稱為RTL級行為仿真或前仿真)是在設計實現前對所創建的邏輯進行驗證,分析其功能是否正確。布局布線以前的仿真都稱作功能仿真,它包括綜合前仿真和綜合后仿真。綜合前仿真主要針對基于原理框圖的設計,而綜合后仿真既適合原理圖設計,也適合基于HDL語言的設計。功能仿真不帶有任何的門延時、線延時等,只是理想情況下的仿真,但它的仿真速度快,可以根據需要觀察電路輸入輸出端口和電路內部任一信號和寄存器的波形。

時序仿真則是使用布局布線后器件給出的模塊和連線的延時信息,在最壞的情況下對電路的行為作出實際地估價。

總的來說,FPGA仿真在FPGA設計和驗證過程中扮演著重要的角色,有助于確保設計的正確性和可靠性。

-

FPGA

+關注

關注

1629文章

21729瀏覽量

603009 -

芯片

+關注

關注

455文章

50714瀏覽量

423155 -

仿真

+關注

關注

50文章

4070瀏覽量

133552

發布評論請先 登錄

相關推薦

FPGA核心知識詳解(3):那些讓FPGA初學者糾結的仿真

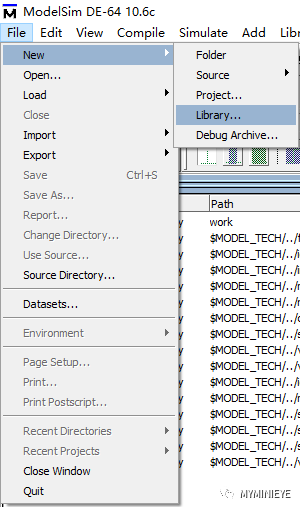

FPGA開發:modelsim仿真流程及波形

fpga仿真是什么

fpga仿真是什么

評論