在這個(gè)信息化飛速發(fā)展的時(shí)代,如果說哪樣?xùn)|西是現(xiàn)代電子設(shè)備的心臟,那非半導(dǎo)體芯片莫屬了。手機(jī)、電腦、汽車,乃至那些我們?nèi)庋劭床灰姷?a href="http://www.1cnz.cn/v/tag/117/" target="_blank">傳感器,里面都有它的身影。但你知道嗎,制造這些小巧而復(fù)雜的半導(dǎo)體芯片,是一項(xiàng)極其挑戰(zhàn)性的技術(shù)工作,它涉及到的科技可真是既深又寬,咱們一起來探個(gè)究竟吧。

01

半導(dǎo)體芯片的設(shè)計(jì)階段,電子設(shè)計(jì)自動(dòng)化(EDA)工具扮演著至關(guān)重要的角色。EDA工具是一系列軟件工具的總稱,它們使得芯片設(shè)計(jì)師能夠利用計(jì)算機(jī)輔助設(shè)計(jì)(CAD)技術(shù)來設(shè)計(jì)和分析整個(gè)半導(dǎo)體制造過程中的電子系統(tǒng),包括集成電路(IC)和印刷電路板(PCB)。

使用EDA工具,設(shè)計(jì)師可以進(jìn)行從邏輯設(shè)計(jì)、電路設(shè)計(jì)、布局設(shè)計(jì)到最終的驗(yàn)證和仿真的全過程設(shè)計(jì)。這些工具不僅提高了設(shè)計(jì)的效率,還大大減少了由于人為錯(cuò)誤導(dǎo)致的缺陷,確保了設(shè)計(jì)的準(zhǔn)確性和可靠性。EDA工具的使用,從根本上改變了芯片設(shè)計(jì)的方式,使得設(shè)計(jì)復(fù)雜度的大幅提升成為可能。

在芯片設(shè)計(jì)流程中,設(shè)計(jì)師首先需要完成電路的邏輯設(shè)計(jì),這通常涉及到硬件描述語言(HDL),如Verilog或VHDL。這些語言允許設(shè)計(jì)師以代碼形式描述電路的邏輯功能,而不是傳統(tǒng)的圖形方式。隨后,這些邏輯描述會(huì)被轉(zhuǎn)換成電路圖,然后是物理布局,即決定各個(gè)電路元件在硅片上的具體位置。

系統(tǒng)級(jí)仿真是芯片設(shè)計(jì)流程中的另一個(gè)關(guān)鍵步驟。在這個(gè)階段,設(shè)計(jì)師會(huì)使用EDA工具來模擬和驗(yàn)證電路設(shè)計(jì)在系統(tǒng)層面的行為。這包括對(duì)電路的時(shí)序、功耗、熱特性和信號(hào)完整性等進(jìn)行分析,確保設(shè)計(jì)在理論上是可行的。系統(tǒng)級(jí)仿真可以在實(shí)際制造芯片之前發(fā)現(xiàn)潛在的問題,從而節(jié)省時(shí)間和成本。

02

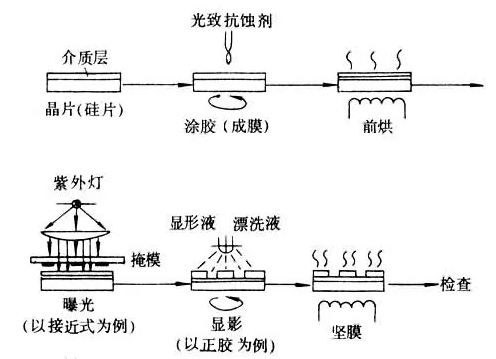

接下來就輪到光刻技術(shù)登場(chǎng)了。光刻過程是半導(dǎo)體制造中的關(guān)鍵步驟之一,它用于在硅片上創(chuàng)建集成電路圖案的微小結(jié)構(gòu)。這個(gè)過程涉及到將一種被稱為光刻膠的光敏材料涂覆到硅片上,然后使用掩模(或稱為光罩)上的特定圖案暴露于光源之下。在光照的區(qū)域,光刻膠的化學(xué)結(jié)構(gòu)會(huì)發(fā)生改變,使得在后續(xù)步驟中,這些區(qū)域能夠被選擇性地去除(正膠工藝)或保留(負(fù)膠工藝)。之后,經(jīng)過一系列的化學(xué)和物理處理過程,最終形成所需的電路圖案。

傳統(tǒng)的光刻技術(shù)通常使用深紫外光(DUV)作為光源,波長大約在193納米。由于光波的波長限制了光刻工藝中最小可制造的特征尺寸(即分辨率極限),因此隨著電子設(shè)備對(duì)更高性能和更小尺寸的需求增加,傳統(tǒng)的DUV光刻技術(shù)已經(jīng)接近其物理極限。

EUV光刻使用波長僅為13.5納米的光源,遠(yuǎn)遠(yuǎn)小于DUV光源的波長。這使得EUV光刻能夠創(chuàng)建更小的特征尺寸,并因此實(shí)現(xiàn)更高密度的集成電路設(shè)計(jì)。EUV光刻技術(shù)的引入是為了滿足先進(jìn)節(jié)點(diǎn),如7納米、5納米以及更小技術(shù)節(jié)點(diǎn)的制造需求。

EUV光刻的引入不僅提高了芯片的性能,還減少了制造過程中需要的掩模數(shù)量,因?yàn)楦俚难谀1┞恫襟E就可以達(dá)到同樣的特征細(xì)節(jié)。

03

但是光刻之前,我們得有硅片,對(duì)吧?制作硅片的過程也是講究滿滿。從單晶硅的生長開始,單晶硅是大多數(shù)集成電路生產(chǎn)中使用的基本材料,單晶硅的質(zhì)量直接影響到集成電路的性能和可靠性。為了生產(chǎn)單晶硅,Czochralski(CZ)提拉法是其中最重要的技術(shù)之一。關(guān)于提拉法技術(shù)大家可以去查詢資料了解,這里不做過多講述。

生長好的單晶硅錠需要經(jīng)過切割、拋光和清洗等后續(xù)加工步驟才能最終轉(zhuǎn)化為可用于集成電路制造的硅片。硅錠首先會(huì)在切割機(jī)中被切割成薄片,這個(gè)過程通常使用金剛石線鋸或內(nèi)部應(yīng)力控制的刀具來進(jìn)行,以減少材料的損耗并提高切割的精度。切割后的硅片厚度通常只有幾百微米。

切割完成后,硅片表面會(huì)非常粗糙,因此需要經(jīng)過拋光的工藝以獲得平滑的表面。拋光過程包括機(jī)械和化學(xué)兩個(gè)階段,通常被稱為CMP(化學(xué)機(jī)械平坦化)。這個(gè)過程可以移除表面的微裂痕和雜質(zhì),減少缺陷,從而保證硅片的質(zhì)量符合集成電路制造的嚴(yán)格標(biāo)準(zhǔn)。

最后,硅片還需要進(jìn)行嚴(yán)格的清洗過程,以去除在切割和拋光過程中產(chǎn)生的所有污染物。清洗通常包括酸、堿、超純水沖洗等多個(gè)步驟,每一步都要在潔凈室環(huán)境下進(jìn)行,以避免任何新的雜質(zhì)附著在硅片表面上。

通過這些精密的工藝流程,高品質(zhì)的單晶硅片最終將為下一步的集成電路制造做好準(zhǔn)備。

04

硅片做好了,還得經(jīng)過離子注入和摻雜,這可是調(diào)整硅片電導(dǎo)率的關(guān)鍵所在。用一些高科技裝備,把必要的雜質(zhì)原子射入硅片,從而賦予硅片特定的電性,聽起來是不是有點(diǎn)像科幻電影里的情節(jié)?

我們的電路圖繪制好了,電導(dǎo)性也調(diào)整好了,下一步就是要在硅片上沉積各種薄膜,這就需要用到化學(xué)氣相沉積(CVD)技術(shù)了。這個(gè)過程中,我們會(huì)用到等離子體增強(qiáng)CVD和低壓CVD等手段,確保薄膜均勻、牢固地附著在硅片上。

05

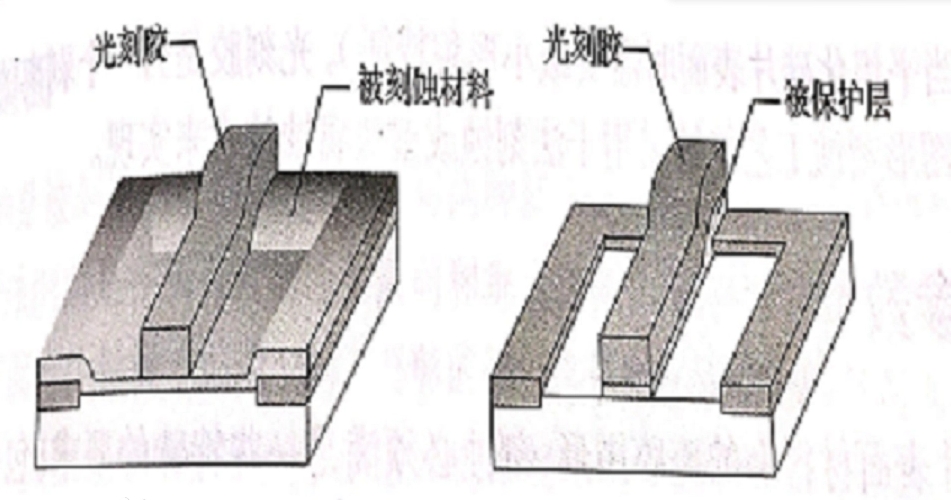

沉積薄膜之后,就得通過刻蝕技術(shù)來去除多余的部分,形成精確的電路圖案。在半導(dǎo)體制造過程中,刻蝕技術(shù)是用來去除硅片上特定區(qū)域的材料,以形成電路圖案的方法。刻蝕工藝主要分為干法刻蝕和濕法刻蝕兩大類。

干法刻蝕(Dry Etching)是利用氣體等離子體產(chǎn)生的化學(xué)活性粒子來移除硅片表面的材料。這種方法的特點(diǎn)是刻蝕過程可以非常精確地控制,因此廣泛應(yīng)用于微細(xì)加工領(lǐng)域。干法刻蝕能夠?qū)崿F(xiàn)高度各向異性的刻蝕,意味著它能垂直于硅片表面精確地移除材料,適合用于制造具有陡峭邊壁的復(fù)雜結(jié)構(gòu)。此外,干法刻蝕過程是在封閉的真空系統(tǒng)中進(jìn)行,可以減少污染,提高制造環(huán)境的清潔度。

濕法刻蝕(Wet Etching)則是使用液體化學(xué)溶劑來溶解和移除硅片上的材料。這種方法操作簡(jiǎn)單,成本較低,但是其刻蝕過程通常是各向同性的,這意味著刻蝕會(huì)沿著水平和垂直方向同時(shí)進(jìn)行,導(dǎo)致邊緣不夠銳利,不適合高精度的圖案制造。然而,在某些應(yīng)用中,比如大面積的材料去除和初步的圖案制造,濕法刻蝕仍然是非常有效和經(jīng)濟(jì)的選擇。

總結(jié)來說,干法刻蝕和濕法刻蝕各有特點(diǎn)和適用范圍,隨著集成電路設(shè)計(jì)的不斷進(jìn)步,這些刻蝕技術(shù)也在不斷地發(fā)展,以滿足更嚴(yán)格的制造要求。

06

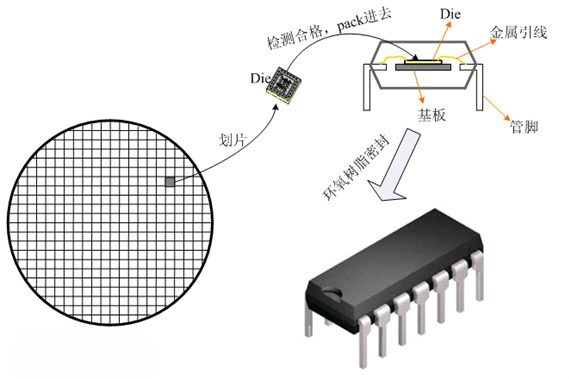

電路造好了,但還不能直接使用,還需要封裝保護(hù)。芯片封裝是半導(dǎo)體制造過程中至關(guān)重要的一步。其主要目的在于保護(hù)微觀尺度的集成電路免受物理損傷、化學(xué)腐蝕、濕氣侵蝕以及電磁干擾等外界因素的影響。封裝過程還能提供電氣連接,將微小的芯片引腳擴(kuò)展至足夠大的引線或焊球,以便于在電路板上進(jìn)行安裝。此外,封裝還有助于散熱,防止集成電路在工作過程中因溫度過高而損壞。

芯片封裝過程一般包括以下幾個(gè)步驟:

準(zhǔn)備裸片:通過切割硅晶圓,將其分割成單獨(dú)的芯片。

安裝芯片:將裸片安裝到一個(gè)支持結(jié)構(gòu)(通常是一個(gè)鉛框或塑料基板)上。

引線鍵合:通過金線鍵合、銀膠鍵合或者焊球貼附等方式,將芯片上的電極連接到封裝引腳上。

封裝:使用塑料、陶瓷或金屬材料將芯片和引線鍵合部分封裝起來,常見的封裝方式有SOIC、QFP、BGA等。

切割和成型:將封裝后的產(chǎn)品切割成單個(gè)封裝單元,并對(duì)引腳進(jìn)行成型處理。

最終檢驗(yàn):對(duì)封裝好的芯片進(jìn)行視覺和電氣性能檢驗(yàn),確保其符合要求。

07

芯片封裝完成之后,我們還得測(cè)試一下。芯片的功能、性能,乃至可靠性,都得通過嚴(yán)格的測(cè)試來驗(yàn)證。

功能測(cè)試是驗(yàn)證芯片是否按照其設(shè)計(jì)規(guī)格正常工作的過程。通過模擬芯片在實(shí)際應(yīng)用中的條件,檢查所有的邏輯功能是否正確執(zhí)行。

性能測(cè)試則是對(duì)芯片的速度和其他性能參數(shù)進(jìn)行評(píng)估。這包括但不限于頻率、功耗、時(shí)序特性等。性能測(cè)試確保了芯片在規(guī)定的性能范圍內(nèi)穩(wěn)定工作。

可靠性測(cè)試是為了評(píng)估和保證產(chǎn)品的長期穩(wěn)定性和耐用性。可靠性測(cè)試可能包括高溫操作壽命(HTOL)、溫度循環(huán)、濕度測(cè)試、機(jī)械沖擊和振動(dòng)測(cè)試等。這些測(cè)試通常在極端條件下進(jìn)行,旨在模擬芯片在整個(gè)預(yù)期使用壽命內(nèi)的環(huán)境變化。

通過這些測(cè)試,制造商能夠確保每一顆芯片都能在其應(yīng)用環(huán)境中提供穩(wěn)定、可靠的性能。如果測(cè)試發(fā)現(xiàn)有任何問題,相關(guān)的芯片可以在批量生產(chǎn)并投入市場(chǎng)之前及時(shí)被篩選出來。這些嚴(yán)格的測(cè)試流程是確保電子產(chǎn)品質(zhì)量和可靠性的關(guān)鍵步驟。

08

未來的路還很長,新材料、量子計(jì)算、納米技術(shù),每一項(xiàng)都可能是革命性的發(fā)展。芯片制造技術(shù)就像是一場(chǎng)永無止境的馬拉松,每一步的創(chuàng)新都可能改變整個(gè)行業(yè)的走向。

看到這里,我想你應(yīng)該對(duì)對(duì)芯片生產(chǎn)有了更深的理解,雖然它是個(gè)技術(shù)密集型的過程,但正是這些復(fù)雜又精妙的技術(shù),讓我們的芯片越來越強(qiáng)大,同時(shí)也越來越實(shí)惠。技術(shù)的創(chuàng)新從未停歇,我們也將一直期待著它帶來的新奇和進(jìn)步。

-

傳感器

+關(guān)注

關(guān)注

2557文章

51747瀏覽量

758901 -

芯片

+關(guān)注

關(guān)注

459文章

51600瀏覽量

429905 -

半導(dǎo)體

+關(guān)注

關(guān)注

335文章

28032瀏覽量

225585

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

如果需要使用DMD進(jìn)行成像控制,需要用到哪些部件?

你的方案需要用到加密芯片嗎?

線纜生產(chǎn)是否需要用到單向測(cè)徑儀?

在冶金生產(chǎn)過程中需要用到的傳感器

運(yùn)算放大電路什么情況下需要用到運(yùn)放調(diào)零?

智能配電房一般都需要用到哪些相關(guān)設(shè)備

汽車芯片的分類 一輛汽車需要用到多少芯片

SMT貼片加工所需要用的主要生產(chǎn)設(shè)備是哪些?

食品檢測(cè)項(xiàng)目需要用到哪些儀器設(shè)備

物聯(lián)網(wǎng)開發(fā)中需要用到哪些編程語言?

一文看懂芯片生產(chǎn)整個(gè)過程以及需要用到哪些技術(shù)

一文看懂芯片生產(chǎn)整個(gè)過程以及需要用到哪些技術(shù)

評(píng)論