Arm Neoverse S3 是 Arm專門面向基礎(chǔ)設(shè)施的第三代系統(tǒng) IP,應用范圍涵蓋高性能計算 (HPC) 、機器學習 (ML)、邊緣和顯示處理單元,是新一代基礎(chǔ)設(shè)施系統(tǒng)級芯片 (SoC) 的理想技術(shù)根基。

Neoverse S3 設(shè)計實現(xiàn)了芯粒 (Chiplet) 與機密計算 (Confidential Compute) 等關(guān)鍵創(chuàng)新,為合作伙伴提供了支持 UCIe、DDR5、CXL 3.1 和 PCIe Gen5/Gen6 等行業(yè)標準的現(xiàn)成功能。

Neoverse S3 提供了一整套系統(tǒng) IP,能夠?qū)崿F(xiàn)高度可組合性、更高的 IO 吞吐量和增強的安全特性。其主要特性包括:

支持設(shè)備分配機密計算的 Arm 機密領(lǐng)域管理擴展 (Realm Management Extension, RME) 功能,并且符合行業(yè)標準 DPE,進行“使用中”的數(shù)據(jù)保護。

支持 PCIe Gen6、CXL 3.1、DDR5 和 HBM3 的 IO 與內(nèi)存系統(tǒng)。

通過基于 UCIe 的 AMBA CHI C2C 的標準化芯粒接口,搭配定制的芯粒開發(fā)工具包,可與 Arm CPU 配合使用。

實現(xiàn)機密計算

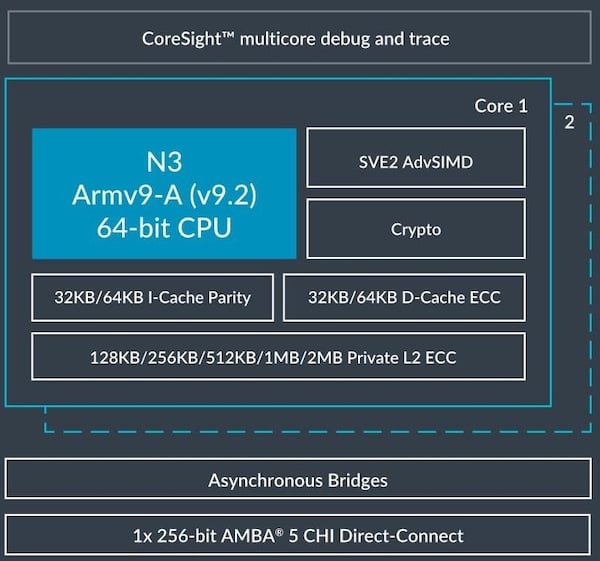

安全性是涉及各類 IP 的 SoC 系統(tǒng)級問題。多年來,加密技術(shù)廣泛應用于數(shù)據(jù)的安全存儲和傳輸,也就是用來保護“靜態(tài)”或“傳輸中”的數(shù)據(jù)。目前基于硬件的安全性改進著重于保護“使用中”的內(nèi)存數(shù)據(jù)。“機密計算”是一個表示加密內(nèi)存中數(shù)據(jù)的行業(yè)術(shù)語。Armv9 架構(gòu)使用硬件技術(shù) RME 來為 Arm 機密計算架構(gòu) (CCA) 提供支持。Neoverse S3 率先支持 RME,使得 Arm Neoverse V3 核心能夠支持完全加密的云虛擬機。

通過 PCIe 和 CXL 掛載的網(wǎng)卡或加速器等 IO 外設(shè)設(shè)備會引入一些潛在的安全威脅。Neoverse S3 系統(tǒng) IP 可確保外部連接的設(shè)備在不影響應用的性能的同時, 僅能訪問授權(quán)的內(nèi)存。這是通過“設(shè)備分配”技術(shù)而實現(xiàn)的,該技術(shù)允許外設(shè)通過直接內(nèi)存訪問 (DMA) 將數(shù)據(jù)傳輸?shù)郊用軆?nèi)存中。除了安全優(yōu)勢之外,該技術(shù)還讓連接設(shè)備可以繞過龐雜的軟件層直接共享數(shù)據(jù),大大增強 I/O 性能。

這種將高效通用計算與高性能加速器結(jié)合起來的能力,是新推出的 Arm Neoverse 計算子系統(tǒng) (CSS) —— Neoverse CSS V3 和 Neoverse CSS N3 的核心。CSS 產(chǎn)品旨在幫助 Arm 合作伙伴通過前所未有的方式,以更低的成本,更迅速、高效地向市場提供針對工作負載優(yōu)化的定制芯片。Microsoft Azure Cobalt 100 便是基于 Neoverse CSS 的軟硬件共同開發(fā)的成果。這些 CSS 產(chǎn)品展示了基于 Arm Neoverse 解決方案的未來,與 Arm 相關(guān)的整個行業(yè)和生態(tài)系統(tǒng)正致力于打造成本更低、復用性更強的基于 Arm 架構(gòu)的芯粒。如果沒有 Neoverse S3 系統(tǒng) IP 這個“無名英雄”打下的基礎(chǔ),這一切都將無法實現(xiàn)。

為行業(yè)標準和芯粒提供支持

PCIe Gen5/Gen6、CXL 3.1、UCIe 和 DDR5 等行業(yè)標準是基礎(chǔ)設(shè)施級 SoC 的關(guān)鍵。但正確實現(xiàn)這些標準并非易事。為支持這些標準,Arm Neoverse S3 完成了許多復雜的工作,并與請求方和物理層 (PHY) 等關(guān)鍵第三方 IP 進行了互操作性測試。Neoverse 為我們的合作伙伴提供了符合這些行業(yè)標準的現(xiàn)成功能,使其能夠更專注于打造差異化、定制化的產(chǎn)品。

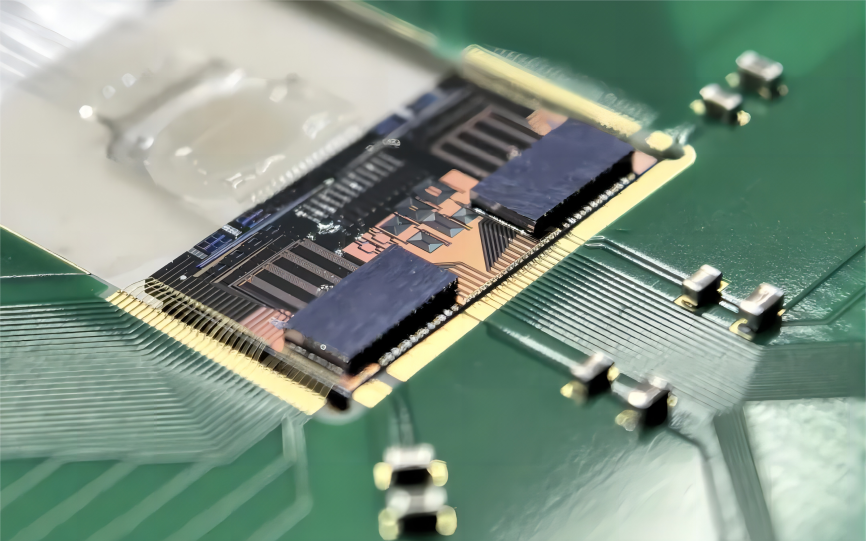

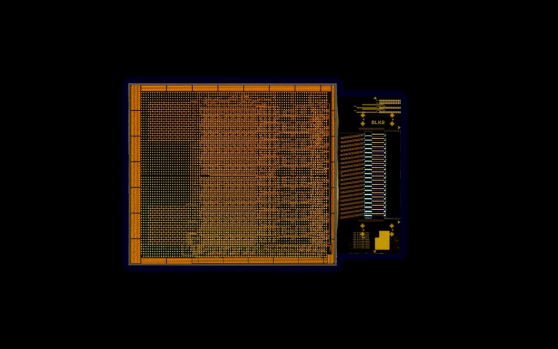

先進工藝的成本不斷飆升,但并不是所有的芯片設(shè)計都能一樣地進行擴展。換言之,只有特定的系統(tǒng)組件(例如 CPU 核心)可以有效地利用工藝進步的成果。芯粒技術(shù)能夠?qū)?SoC 分解到系統(tǒng)級封裝 (SoaP) 中,以便更經(jīng)濟地采用不同工藝節(jié)點來構(gòu)建系統(tǒng)。SoaP 支持以模塊化方式打造解決方案,從而將芯粒開發(fā)的成本分攤到不同解決方案中。

不過,這種模塊化設(shè)計不能增加架構(gòu)和軟件設(shè)計的復雜性。Arm Neoverse 解決方案下的芯粒采用標準化接口并帶有預定義芯粒配置,這樣 Arm Neoverse 生態(tài)系統(tǒng)中的每個芯粒供應商都能夠構(gòu)建兼容 Neoverse CSS 的芯粒。這些芯粒標準包括:

AMBA CHI C2C 涵蓋了 SoaP 不同子系統(tǒng)通信的應用層和鏈路層協(xié)議。

Arm 芯粒系統(tǒng)架構(gòu) (Arm Chiplet System Architecture)涵蓋了定義地址轉(zhuǎn)換、中斷處理、系統(tǒng)管理和安全的架構(gòu)合規(guī)性標準。

Arm 基礎(chǔ)系統(tǒng)架構(gòu) (Arm Base System Architecture) 涵蓋了對軟件提供標準支持的硬件需求。

為了進一步推廣 AMBA CHI C2C 和芯粒的普及,Arm 提供了基于 Neoverse S3 設(shè)計的芯粒設(shè)計套件。該設(shè)計套件為 IO 一致性和完全一致性加速,或分解式芯粒奠定了基礎(chǔ)。

Neoverse CSS和定制芯片的基礎(chǔ)

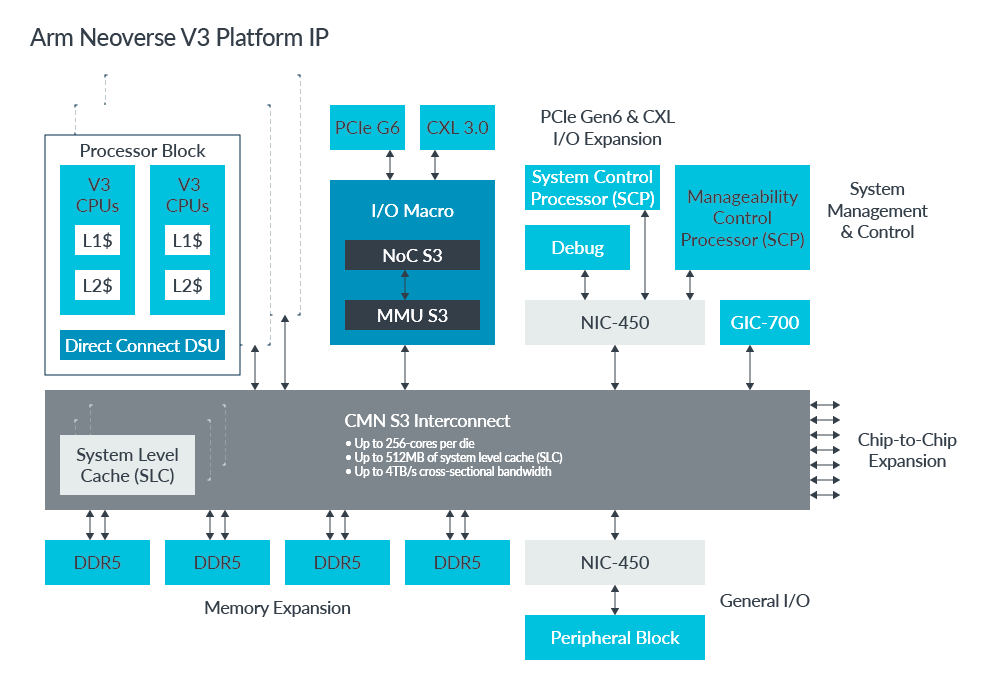

圖:Arm Neoverse 系統(tǒng)中 Neoverse S3 設(shè)計示意圖,

其中包括 CMN S3、MMU S3 和 NOC S3

Neoverse S3 系統(tǒng) IP 由 Neoverse CMN S3、Neoverse MMU S3 和 Neoverse NOC S3 所組成,這三者共同構(gòu)成了一個成熟可靠的強大平臺,幫助合作伙伴構(gòu)建其 SoC。

CMN S3 建立在 CMN-700 IP 基礎(chǔ)之上,為性能更高、數(shù)據(jù)需求量更大的 Neoverse 核心提供一致性的支持。CMN S3 專為全新的芯粒技術(shù)而構(gòu)建,支持機密計算,同時提高了性能和可擴展性,而這恰巧是實現(xiàn)互連的關(guān)鍵所在。

CMN S3 能夠安全且高性能(高帶寬、低延遲)地連接核心和加速器芯粒,這對于開發(fā)高能效、高性價并針對工作負載優(yōu)化的 SoC 至關(guān)重要。領(lǐng)先的云服務提供商都利用數(shù)據(jù)處理單元 (DPU) 從主機 CPU 卸載安全、存儲和網(wǎng)絡功能。它們還會部署和開發(fā) GPU、NPU 和 TPU,以加速現(xiàn)代云軟件中的人工智能 (AI) 和 ML 功能。與此同時,電信提供商也在 5G RAN 和邊緣基礎(chǔ)設(shè)施中部署包括 CPU 和加速器的異構(gòu) SoC 。

內(nèi)存管理單元 MMU S3 建立在行業(yè)標準化的 MMU-700 IP 基礎(chǔ)之上,可為片上、芯粒和插入式卡提供高性能,機密計算支持,并支持 PCIeG6 與 CXL3.1的 IO MMU 功能。

片上網(wǎng)絡 NOC S3 是基于 NI-700 構(gòu)建的新型非一致性互連技術(shù),專為 IO 一致性加速器芯粒而打造,能夠幫助合作伙伴如之前基于片上 AMBA 的設(shè)計一樣, 輕松簡便地構(gòu)建高性能的分解式 SoC。

Neoverse S3 是我們的第三代 Neoverse 系統(tǒng) IP,同時也是 Neoverse CSS V3 和 Neoverse CSS N3 的基礎(chǔ),可以為構(gòu)建從云服務到邊緣 DPU 的高水平基礎(chǔ)設(shè)施 SoC 提供所需的基本功能,該平臺不僅符合關(guān)鍵的行業(yè)標準,并且成為了行業(yè)標桿。Neoverse S3 將提供現(xiàn)成的機密計算和芯粒功能,助力合作伙伴實現(xiàn)新一代創(chuàng)新的定制芯片。

審核編輯:劉清

-

加速器

+關(guān)注

關(guān)注

2文章

817瀏覽量

38620 -

SoC芯片

+關(guān)注

關(guān)注

1文章

621瀏覽量

35421 -

HPC

+關(guān)注

關(guān)注

0文章

331瀏覽量

24048 -

機器學習

+關(guān)注

關(guān)注

66文章

8470瀏覽量

133672 -

PCIe接口

+關(guān)注

關(guān)注

0文章

121瀏覽量

9942

原文標題:Neoverse S3 系統(tǒng) IP 為打造機密計算和多芯粒基礎(chǔ)設(shè)施 SoC 夯實根基

文章出處:【微信號:Arm社區(qū),微信公眾號:Arm社區(qū)】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

相關(guān)推薦

國內(nèi)首款2Tb/s 3D集成硅光芯粒成功出樣,華為、英偉達等巨頭爭相布局

PoE交換機如何助力智慧城市基礎(chǔ)設(shè)施建設(shè)?

Arm正式發(fā)布芯粒系統(tǒng)架構(gòu)首個公開規(guī)范

Arm宣布其芯粒系統(tǒng)架構(gòu)正式推出首個公開規(guī)范

今日看點丨Arm 發(fā)布芯粒系統(tǒng)架構(gòu)首個公開規(guī)范;納芯微推出車規(guī)級D類音頻功率放大器

亞馬遜云科技發(fā)布Amazon S3新功能

高鴻信安全國產(chǎn)可信低空經(jīng)濟信息基礎(chǔ)設(shè)施解決方案

奇異摩爾32GT/s Kiwi Link Die-to-Die IP全面上市

NVIDIA助力印度打造AI基礎(chǔ)設(shè)施

強勢入局芯粒技術(shù)鏈 東方晶源PanSys產(chǎn)品重磅發(fā)布

英特爾OCI芯粒在新興AI基礎(chǔ)設(shè)施中實現(xiàn)光學I/O(輸入/輸出)共封裝

英特爾實現(xiàn)光學IO芯粒的完全集成

芯品# 高性能計算芯片

炬芯科技智能手表SoC采用芯原2.5D GPU IP

Arm新Arm Neoverse計算子系統(tǒng)(CSS):Arm Neoverse CSS V3和Arm Neoverse CSS N3

評論