PL通過NoC讀寫DDR4實(shí)驗(yàn)

實(shí)驗(yàn)VIvado工程為“pl_rw_ddr”

1.1硬件介紹

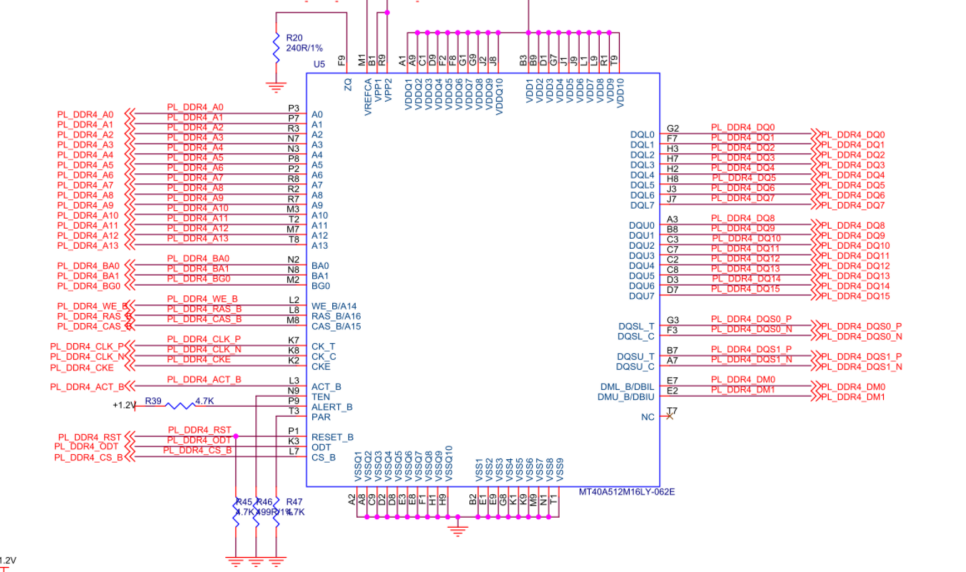

開發(fā)板的PL端有4顆16bit ddr4

1.2Vivado工程建立

Versal的DDR4是通過NoC訪問,因此需要添加NoC IP進(jìn)行配置。

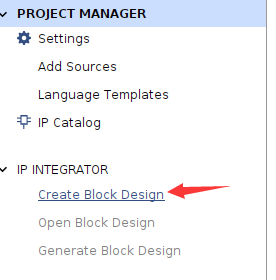

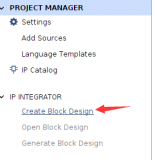

1.2.1創(chuàng)建一個Block design并配置NoC

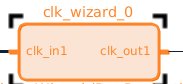

1)選擇Create Block Design

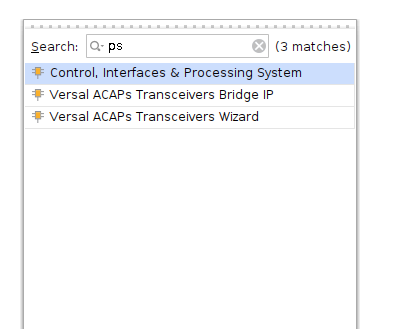

2)添加CIPS

? ?

? ?

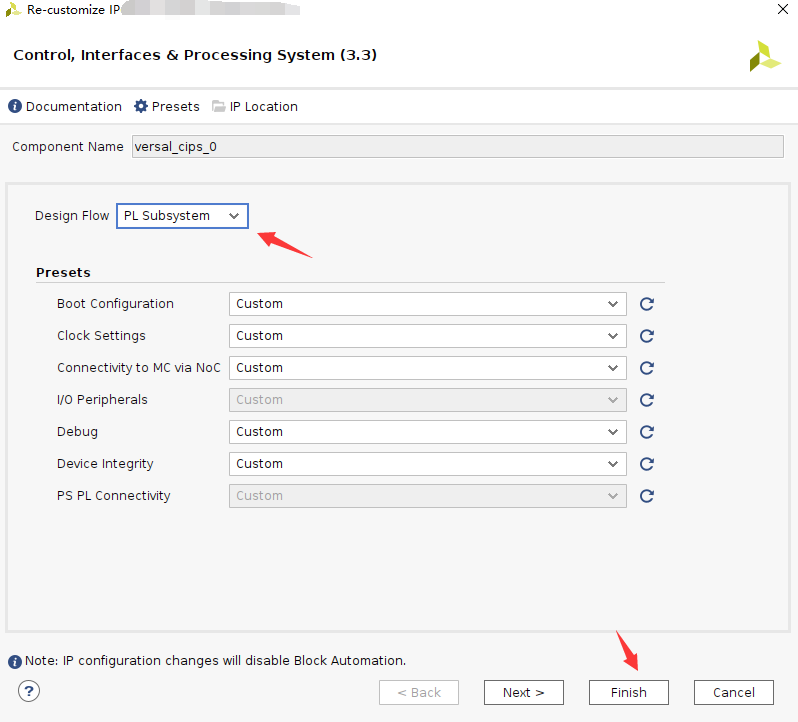

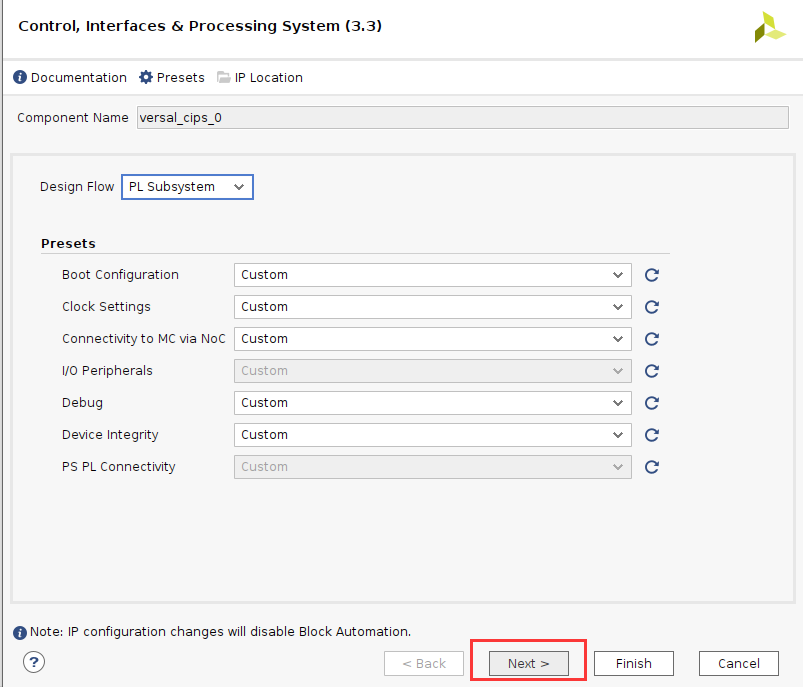

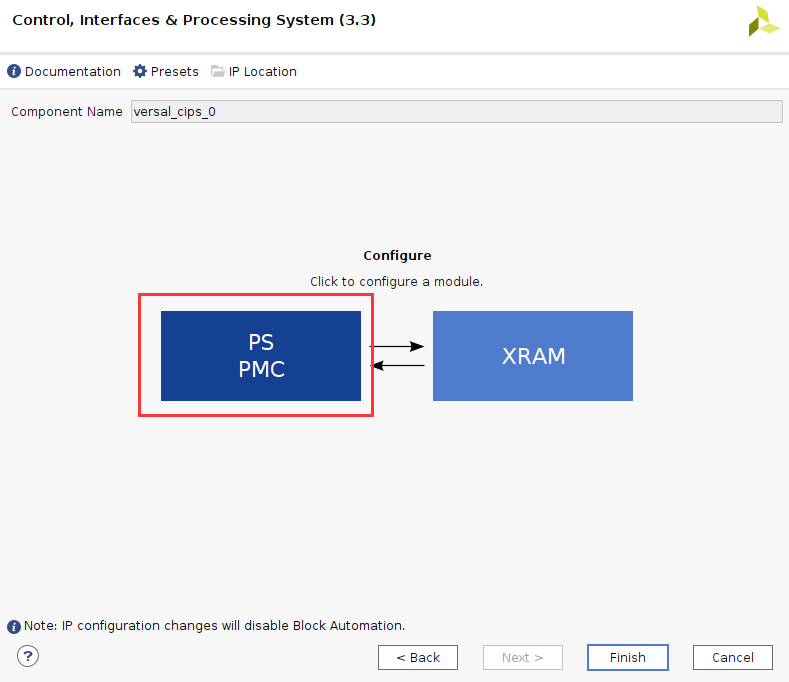

3)雙擊CIPS,選擇PL_Subsystem,只有PL端的邏輯

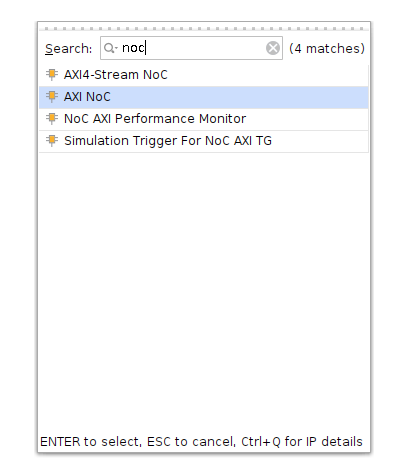

4)添加NoC IP

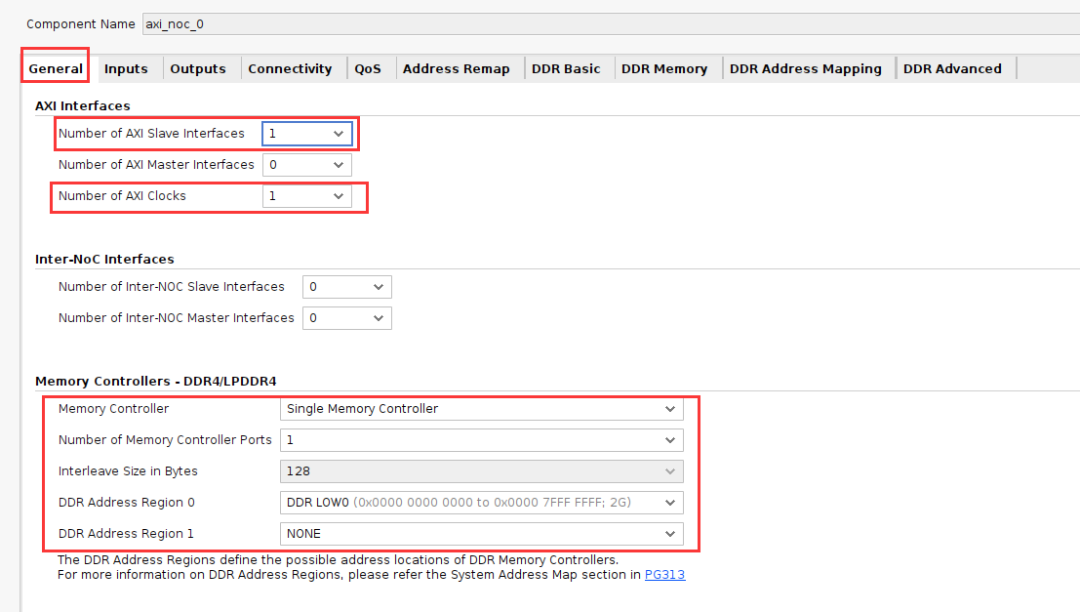

5)配置NoC

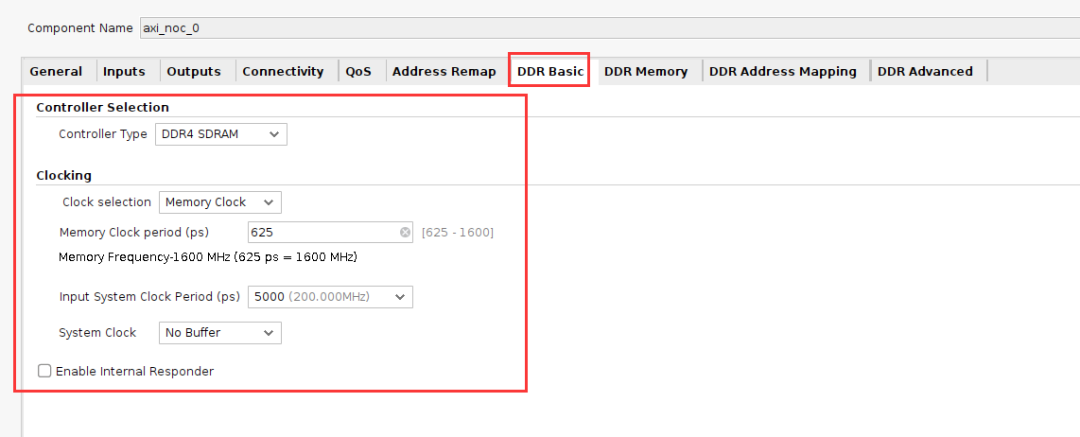

選擇一個AXI Slave和AXI Clock,選擇”Single Memory Controller”

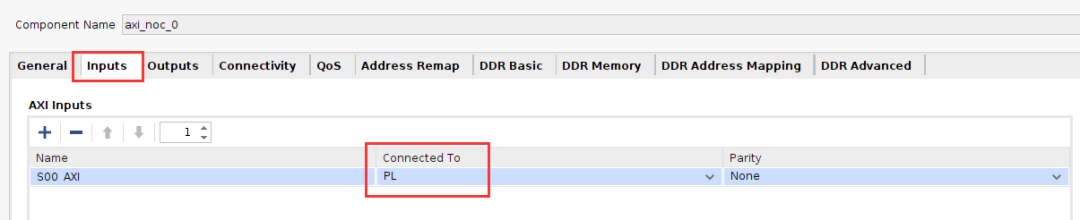

選擇Inputs為PL

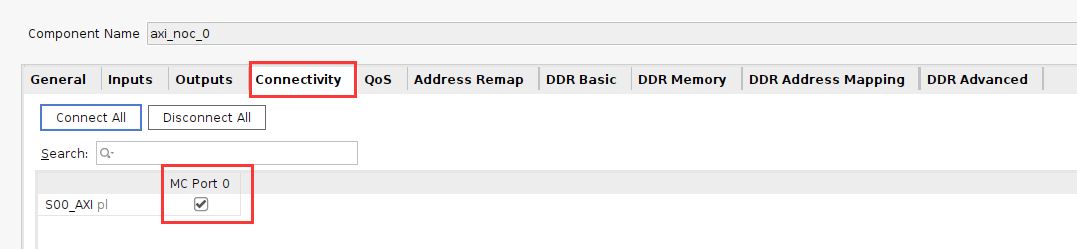

連接port

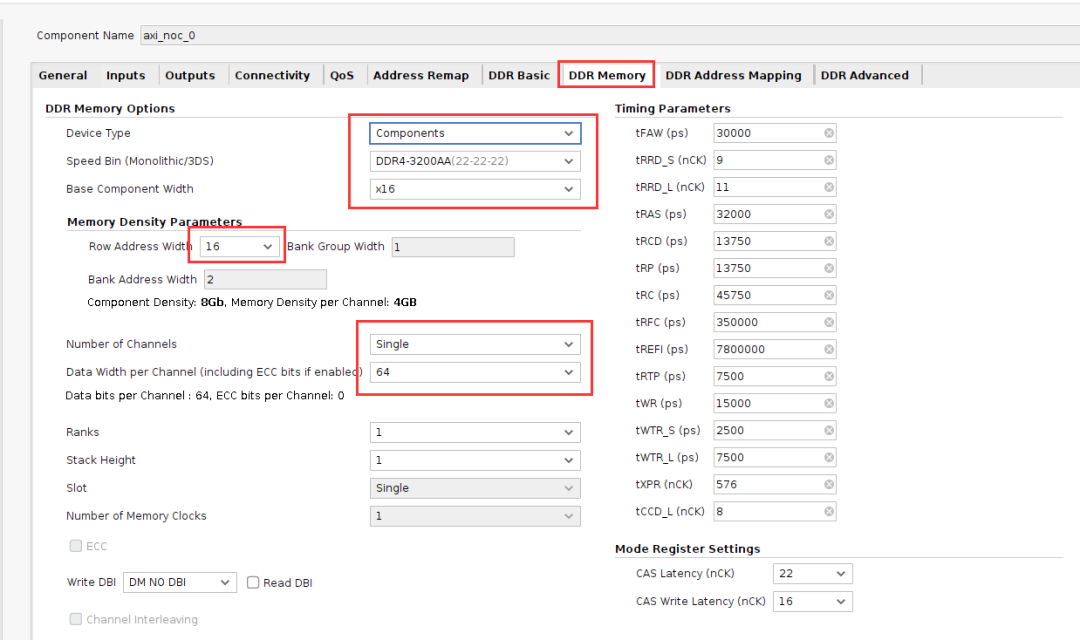

DDR4配置

配置完成,點(diǎn)擊OK

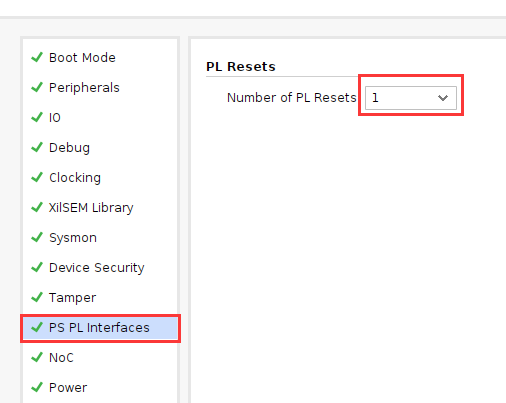

6)配置CIPS,添加復(fù)位

? ?

? ?

點(diǎn)擊Finish

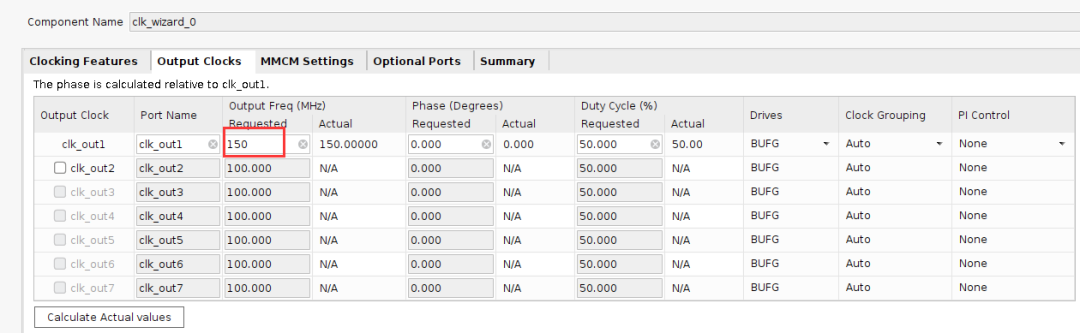

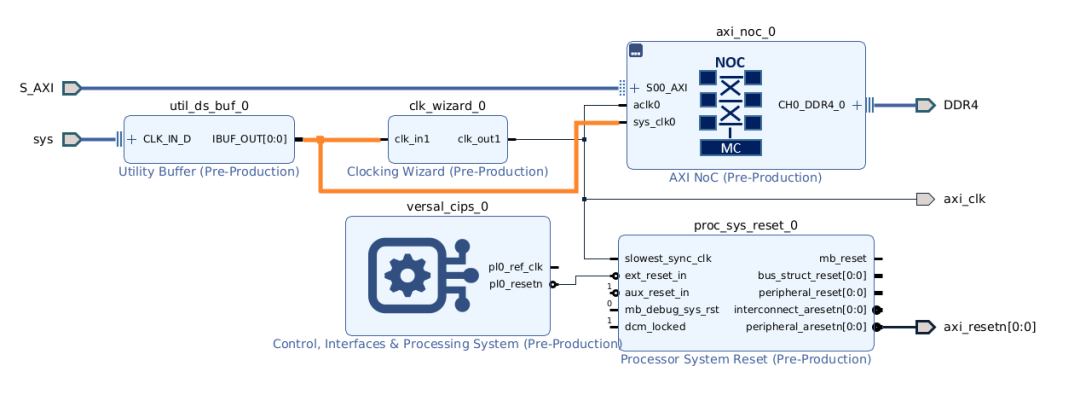

7)添加Clocking Wizard,配置輸出時鐘150MHz,作為PL端讀寫時鐘

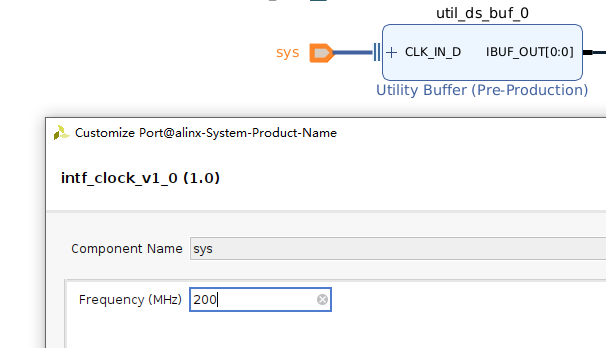

8)添加IBUFDS為NoC和Clocking Wizard提供參考時鐘,并導(dǎo)出S00_AXI,CH0_DDR4_0等總線,添加axi_clk,axi_resetn為PL端提供時鐘和復(fù)位。

雙擊參考時鐘引腳,并配置頻率為200MHz

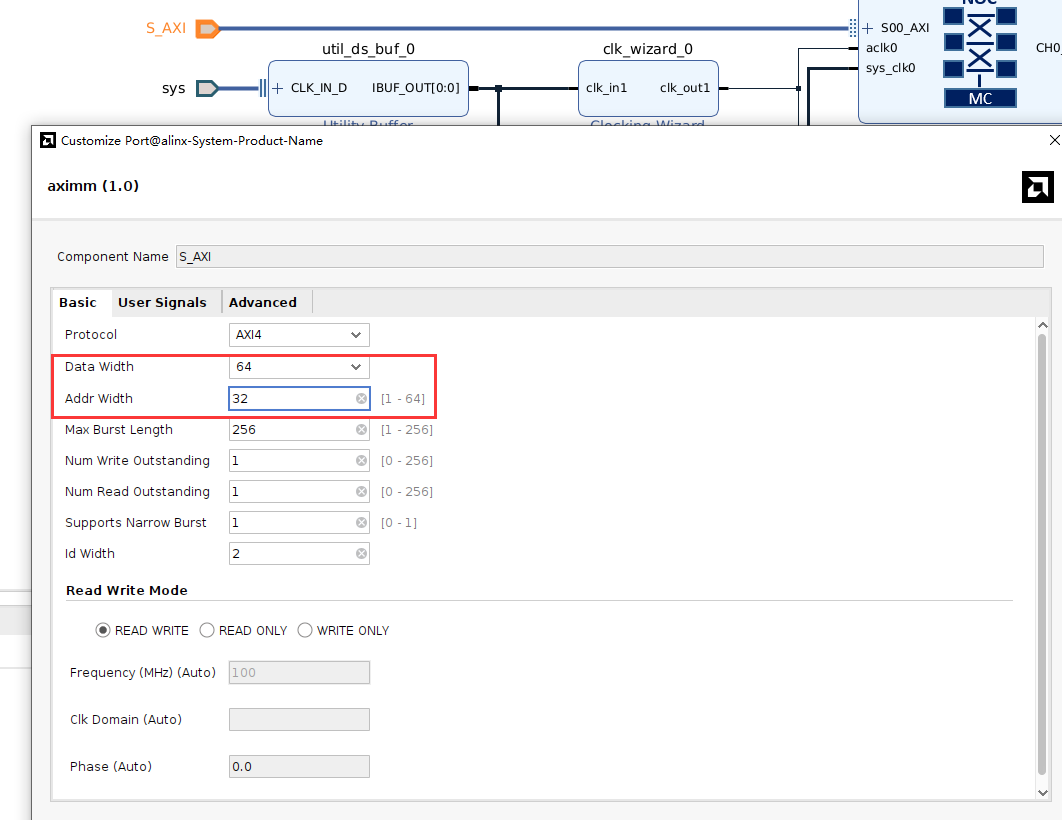

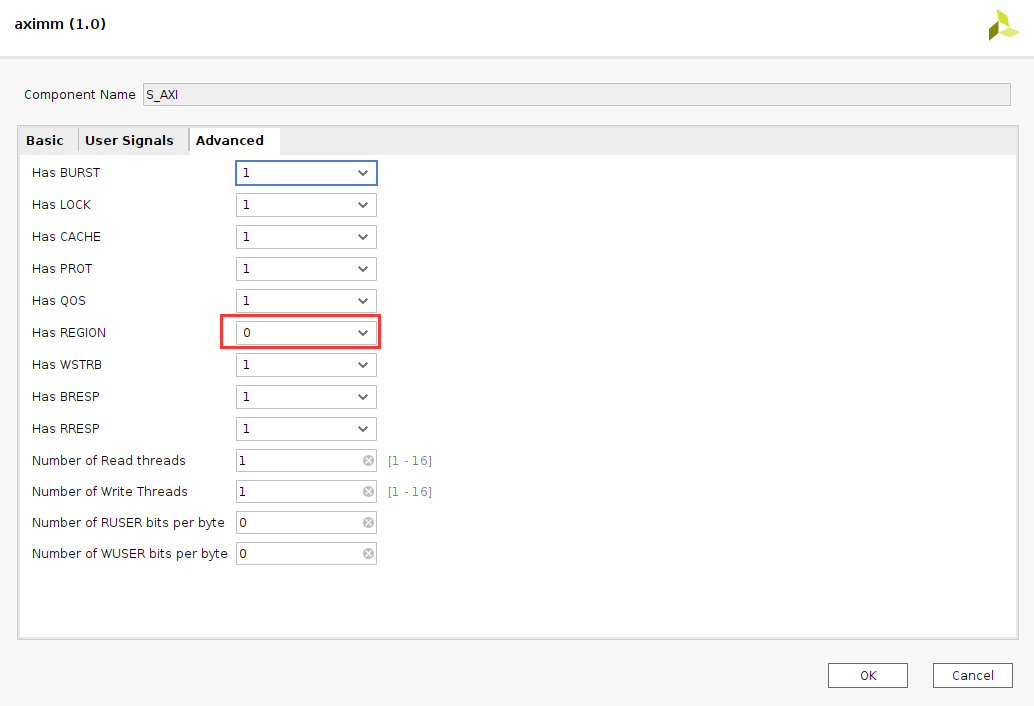

雙擊AXI總線,并配置

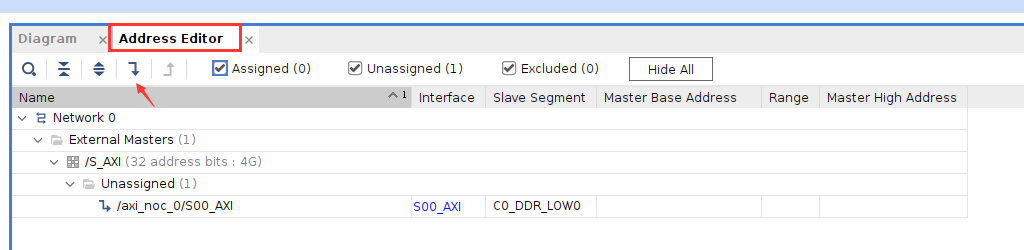

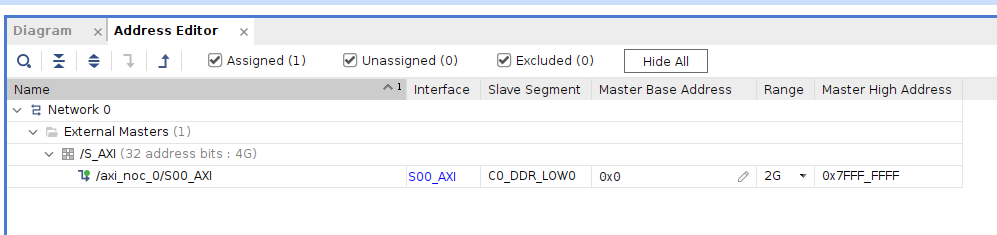

9)分配地址

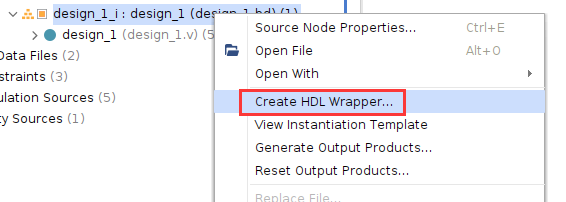

10)Create HDL

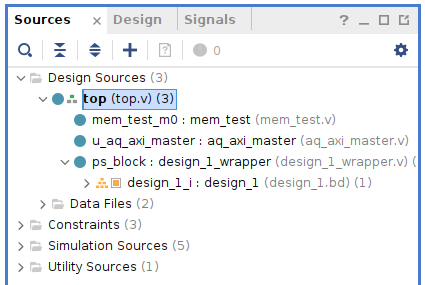

1.2.2添加其他測試代碼

其他代碼主要功能是讀寫ddr4并比較數(shù)據(jù)是否一致,這里不做詳細(xì)介紹,可參考工程代碼。

? ??

? ??

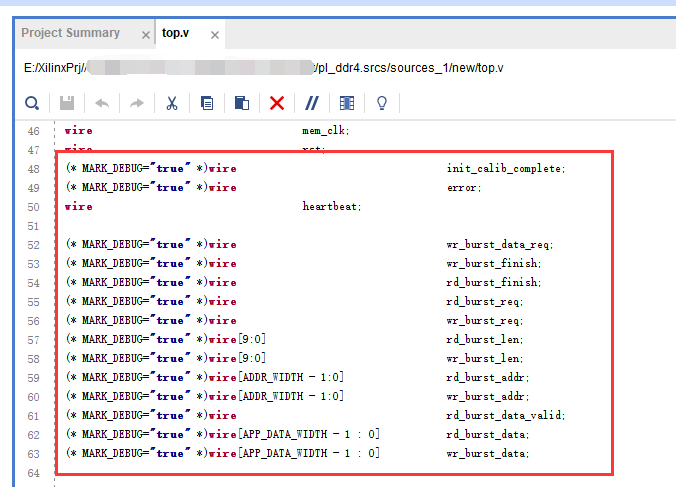

1)在mem_test.v中添加mark_debug調(diào)試

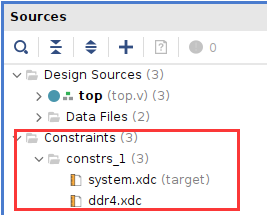

2)引腳綁定

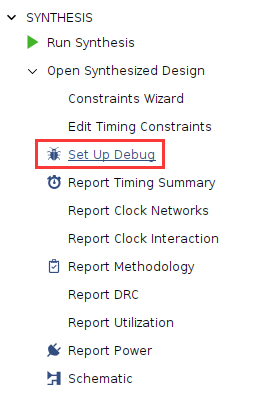

3)綜合

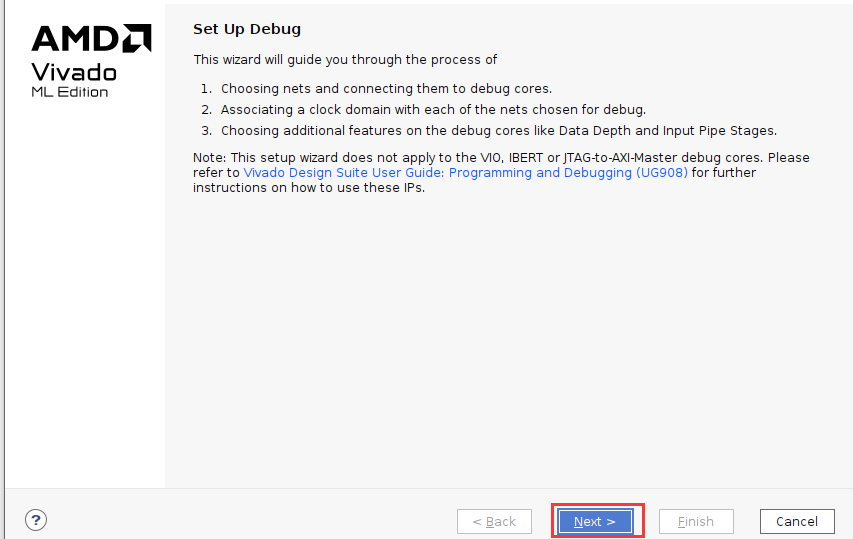

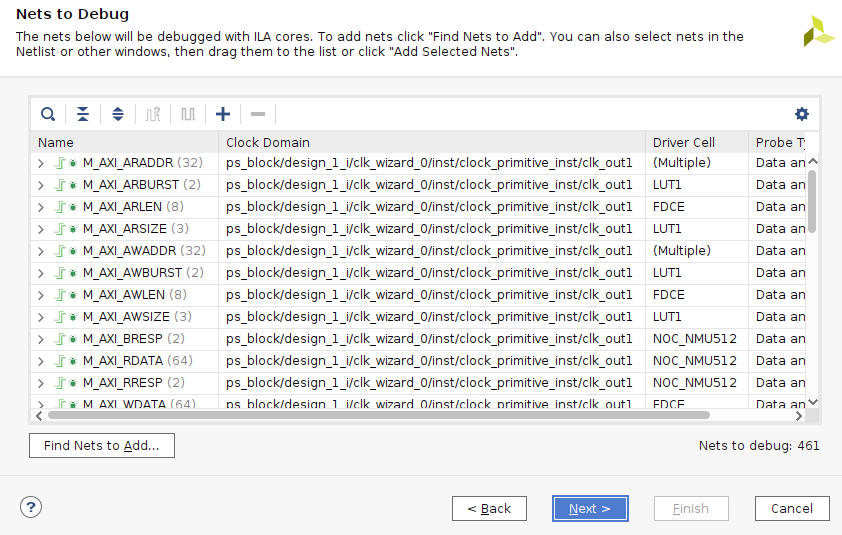

4)綜合完成后點(diǎn)擊Set up debug

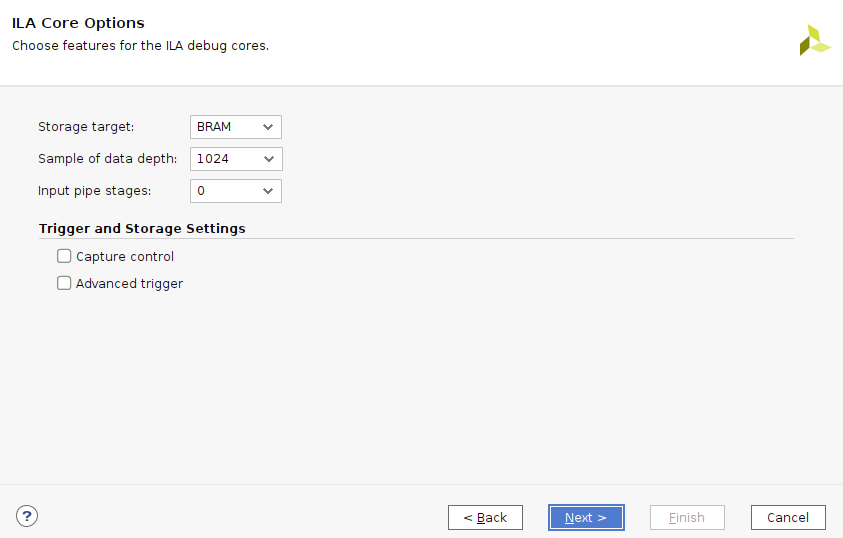

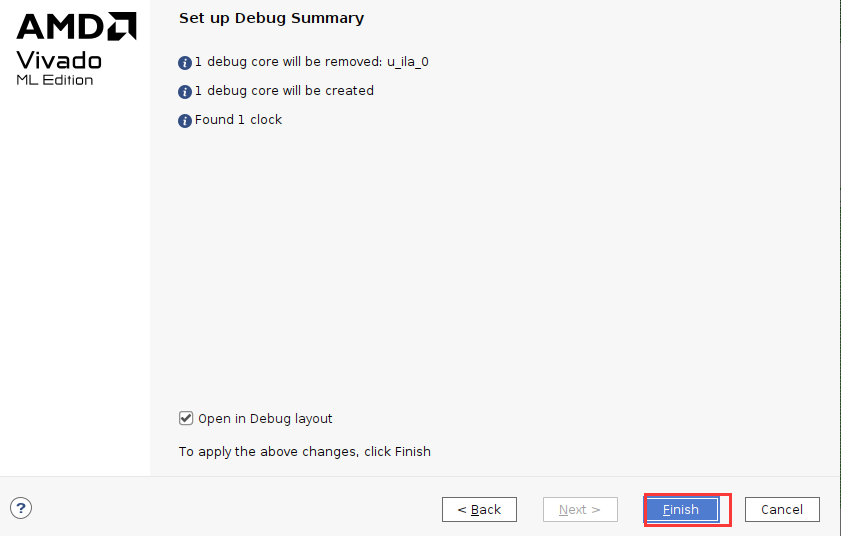

根據(jù)需求設(shè)置采樣點(diǎn)數(shù)

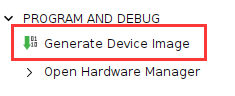

之后保存,并生成pdi文件

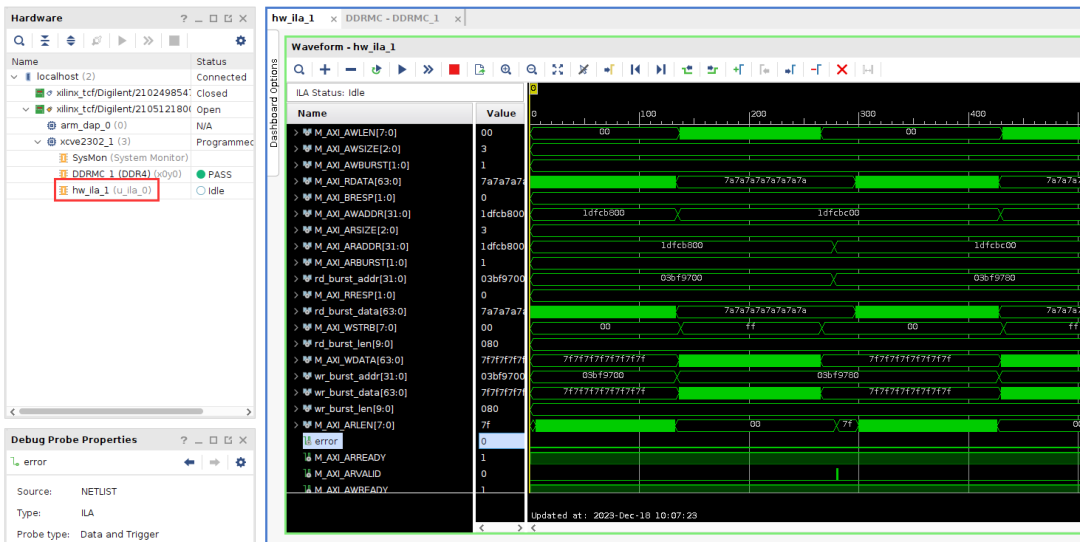

1.3下載調(diào)試

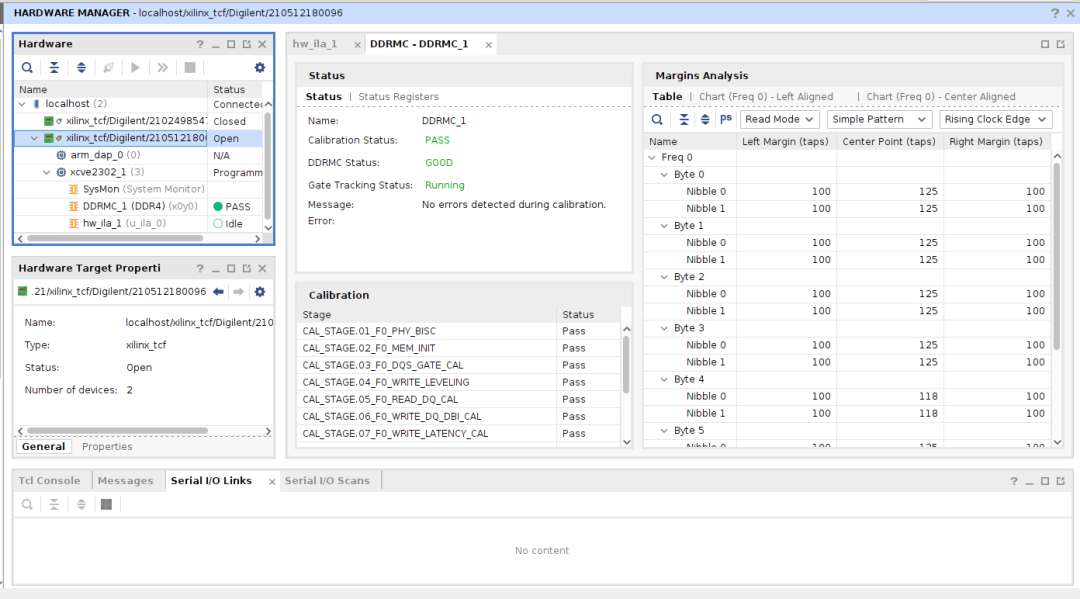

生成pdi文件以后,使用JTAG下載到開發(fā)板,在MIG_1窗口會顯示DDR4校準(zhǔn)等信息

在hw_ila_1中可以查看調(diào)試信號

1.4實(shí)驗(yàn)總結(jié)

本實(shí)驗(yàn)通過PL端Verilog代碼直接讀寫ddr4,主要了解NoC的配置方法,如何通過NoC訪問DDR4,后續(xù)的實(shí)驗(yàn)中都要用到此配置。

審核編輯:劉清

-

JTAG

+關(guān)注

關(guān)注

6文章

403瀏覽量

72255 -

DDR4

+關(guān)注

關(guān)注

12文章

323瀏覽量

41223 -

AXI總線

+關(guān)注

關(guān)注

0文章

66瀏覽量

14398 -

NoC

+關(guān)注

關(guān)注

0文章

38瀏覽量

11820 -

CLK

+關(guān)注

關(guān)注

0文章

127瀏覽量

17343

原文標(biāo)題:【ALINX 技術(shù)分享】AMD Versal AI Edge 自適應(yīng)計(jì)算加速平臺之PL通過NoC讀寫DDR4 實(shí)驗(yàn) (4)

文章出處:【微信號:ALINX,微信公眾號:ALINX】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

相關(guān)推薦

AMD Versal AI Edge自適應(yīng)計(jì)算加速平臺之Versal介紹(2)

【ALINX 技術(shù)分享】AMD Versal AI Edge 自適應(yīng)計(jì)算加速平臺之準(zhǔn)備工作(1)

【ALINX 技術(shù)分享】AMD Versal AI Edge 自適應(yīng)計(jì)算加速平臺之 Versal 介紹(2)

AMD Versal AI Edge自適應(yīng)計(jì)算加速平臺PL LED實(shí)驗(yàn)(3)

AMD Versal AI Edge自適應(yīng)計(jì)算加速平臺之PL LED實(shí)驗(yàn)(3)

AMD Versal AI Edge自適應(yīng)計(jì)算加速平臺之體驗(yàn)ARM,裸機(jī)輸出(7)

Xilinx推出Versal:業(yè)界首款自適應(yīng)計(jì)算加速平臺,支持快速創(chuàng)新

賽靈思發(fā)布自適應(yīng)計(jì)算加速平臺芯片系列Versal

賽靈思Versal自適應(yīng)計(jì)算加速平臺助于高效實(shí)現(xiàn)設(shè)計(jì)目標(biāo)

賽靈思Versal自適應(yīng)計(jì)算加速平臺指南

DDR4/LPDDR4硬核控制器I/O plannin的設(shè)計(jì)和實(shí)現(xiàn)

Versal:首款自適應(yīng)計(jì)算加速平臺(ACAP)

AMD發(fā)布第二代Versal自適應(yīng)SoC,AI嵌入式領(lǐng)域再提速

ALINX受邀參加AMD自適應(yīng)計(jì)算峰會

AMD Versal自適應(yīng)SoC DDRMC如何使用Micron仿真模型進(jìn)行仿真

評論