共讀好書

陳聰 李杰 姜理利 吳璟 張巖 郁元衛 黃旼 朱健

(南京電子器件研究所 微波毫米波單片集成和模塊電路重點實驗室)

摘要:

隨著輕量化、小型化及模塊功能多樣化的發展,由二維平面到三維高度上的先進封裝技術應運而生。微凸點作為實現芯片到圓片異構集成的關鍵結構,可有效縮短信號傳輸距離,提升芯片性能。利用電沉積法在 Si基板上以 Cu作支撐層、Ni作阻擋層淀積微米級別的 Au/Sn凸點,所制得的多層凸點直徑約 60 μm、高度約 54 μm,其高度可控、尺寸可調,并研究了 Die內凸點高度的一致性,同時對凸點進行了剪切強度和推拉力測試。結果表明,Die內凸點高度均勻性≤2%,剪切力可達 61.72 g以上,與化合物芯片(另一側為 Au)鍵合后推拉力可達 7.5 kgf,可實現與化合物芯片的有效集成。

引言

隨著異構集成模塊功能和特征尺寸的不斷增加、芯片尺寸的不斷減小,I/O 數量相應大幅增加,對芯片的布線密度提出了更加苛刻的要求。三維異構集成技術的誕生為此提供了解決思路[1?3],通過對立體空間的充分利用實現高密度、多材料的芯片堆疊,在降低功耗、提升性能的同時使得電子產品的尺寸和質量得以大幅縮減[4?6]。而金屬/焊料微凸點之間的互連是實現芯片三維疊層的關鍵,為了提高芯片三維疊層封裝互連的可靠性,制備出具有高互連可靠性的微凸點對微電子封裝技術的進一步發展具有重要的作用。

與傳統的引線鍵合相比,凸點結構使得互連長度更短,互連電阻和電感更小,器件的電性能得到了明顯提高和改善。與此同時,芯片工作時產生的熱可通過凸點直接傳到基板上,大幅提高了散熱性能。更為重要的是,凸點可呈周邊式和面陣式分布,提高了封裝密度,縮減了封裝體積。以 Au/Sn合金為例,作為半導體后道封裝中常用的焊料之一,因其優良的導熱和導電性、潤濕性、耐腐蝕性和抗蠕變性以及在焊接中無需助焊劑等優點在三維封裝技術中得到了廣泛應用[7?8]。對于 Au/Sn 合金而言,比例控制至關重要,這將決定金屬間化合物的組合,從而決定鍵合的質量,比例的差異將導致膜組成發生變化而脫離共融數值,從而降低鍵合特性[9] 。

目前,因凸點下金屬層(UBM)和凸點沉積工藝的不同,相應的凸點制備工藝存在較大差異。常用的凸點制備技術主要包括:蒸發/濺射沉積法、絲網印刷法、植球法和電沉積法等。隨著凸點尺寸及節距的減小,絲網印刷法、植球法等的成本急劇上升,電沉積法成為小尺寸微凸點制備的唯一選擇[10] ,具有 工 藝 簡 單 、易 于 批 量 生 產 及 凸 點 定 位 精 確 等優點。

本文利用電沉積法在 Si 基板上以 Cu 作支撐層、Ni作阻擋層淀積微米級別的 Au/Sn 凸點,前者用于增加凸點高度,后者用于實現芯片互連。在對其外觀形貌進行監測的基礎上研究單個電路單元(Die)內凸點高度的一致性,同時對凸點進行相關性能測試,主要包括剪切強度和推拉力測試,以評估該工藝方法下所制備的 Au/Sn凸點的可靠性。

1 實驗

1.1 試樣制備

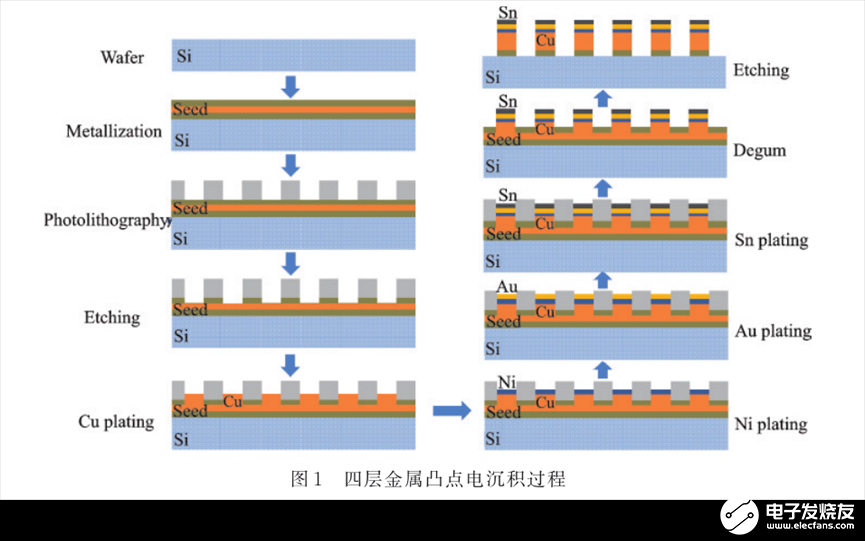

以直流模式自下而上依次進行 Cu?Ni?Au/Sn四層金屬凸點材料的淀積,整體高度控制在 50 μm左右。其中,Cu?Ni?Sn的電沉積由德國微電鍍技術(MOT)公司所生產的電鍍系統完成,Au 的淀積由上海新陽晶圓水平電鍍系統完成,相應的藥水均由對應廠家提供。工藝過程中,在維持添加劑濃度適當的前提下通過調節電流密度、電流值及工藝時間,以改善凸點表面形貌及高度的一致性,進而對相關工藝參數進行固定。需要指出的是,本文所制得的 Au/Sn凸點的高度及厚度比例是經過篩選的,包括 Au/Sn=6 μm/4 μm,6 μm/5 μm,6 μm/6 μm,8 μm/7 μm,10 μm/10 μm 及 5 μm/5 μm 等。最終的驗證結果表明,Au/Sn比例接近于 1/1,Sn層高度適當(5~6 μm)時,效果相對較優。具體工藝參數的設定與圓片的占空比及目標高度有關,故此處僅說明相 關的 電流 密度 ,具體 為:Ni ? 2.5ASD、Au ?0.3ASD、Sn?2ASD(ASD,指電極單位面積所通電的安培數,常以 A/dm2 表示),并根據測試結果進一步確定工藝時間。作為支撐層的 Cu層較高,對于整個凸點高度的一致性起著決定性影響,故需對淀積Cu 的工藝參數進行一定篩選。若不考慮相關前置工藝,四層金屬凸點的電沉積過程如圖 1所示。

1.2 檢測方法

試樣工藝完成后去膠、腐蝕、甩干,并進行相關檢驗,主要包括:利用金相顯微鏡觀測 Au/Sn 凸點表面形貌;采用 P?17 臺階儀測量圓片及 Die 內凸點高度,并計算高度一致性;制樣后利用掃描電子顯微鏡(SEM)觀測凸點整體形貌及各層金屬厚度;利用剪切力測試設備測試其剪切強度;在與化合物芯片鍵合后(另一側為 Au)利用拉力測試裝置進行推拉力測試,以評估其鍵合質量。

2 結果與分析

2.1 關鍵工藝參數篩選

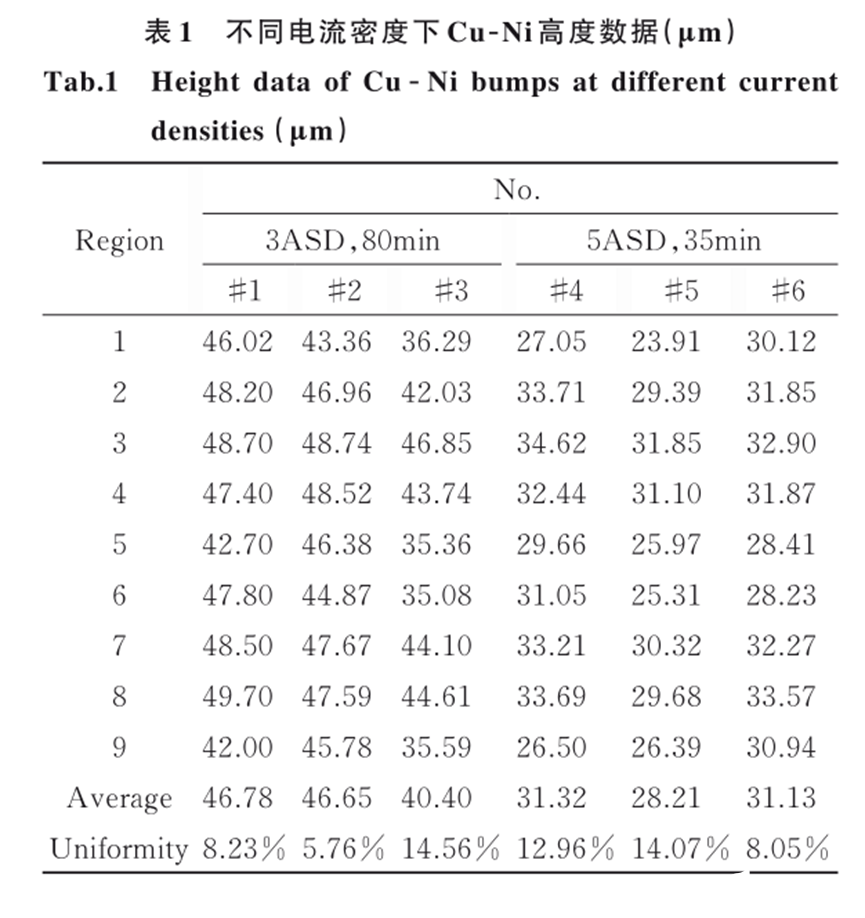

凸點各層金屬自下而上分別為 Cu/Ni/Au/Sn,作為支撐層的 Cu層較高,對于整個凸點高度的一致性起著決定性影響。因此,首先對 Cu淀積時的工藝參數進行篩選,此處選取關鍵工藝參數,即電流密度,以研究不同電流密度下圓片內九點區域處(自上而下、從左到右)Cu/Ni凸點的高度差異,并對圓片內凸點的一致性進行驗證,具體結果見表 1。結果 表 明 ,3ASD 下電 沉積 速率 約為 0.6 μm/min,5ASD 電沉積速率約為 1.0 μm/min,這一數值同理論 Cu 電沉積速率相吻合。但因理論占空比與實際值存在差異,故實際高度值與理論值有所偏差。同時,受限于機臺,在相同工藝條件下 Cu/Ni凸點的片間重復性較差。可以明確的是,就一致性而言,3ASD下 Cu/Ni凸點的片內均勻性相對較優。

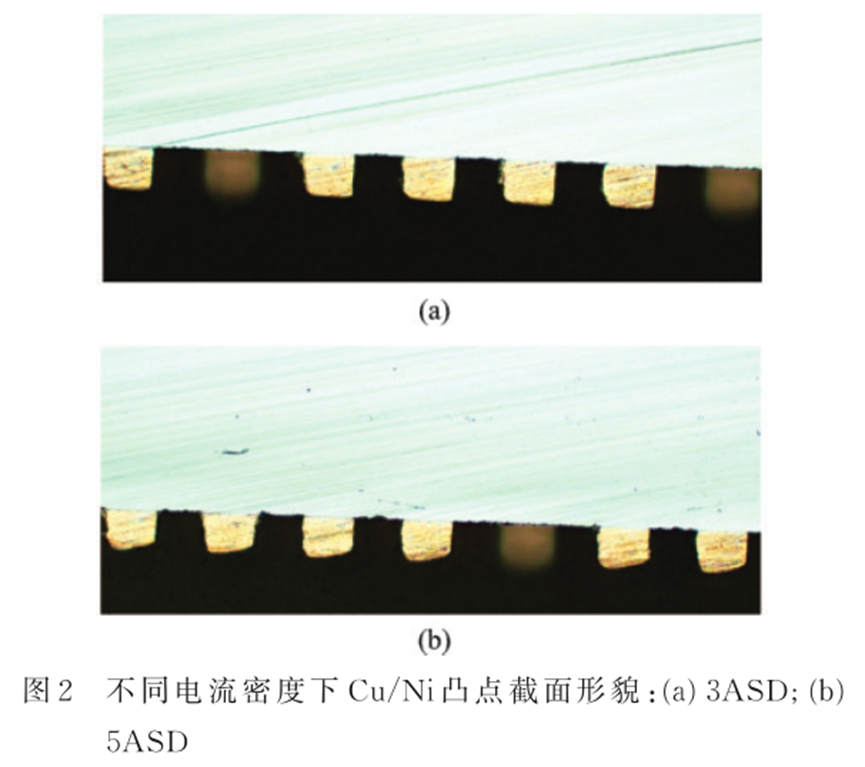

為進一步對比不同電流密度下 Cu/Ni凸點的差異性,分別對 3ASD 和 5ASD 下所制得的微凸點進行劃片后觀測,結果如圖 2 所示。結果表明,3ASD下所制得的凸點較為平整,表面無明顯傾斜。這是因為隨著電流密度的增加,陰極極化作用隨之增強,但當其過高時,鍍層表面分布極不均勻平整,各點間生長速率存在差異,進而導致鍍層質量下降。因此,綜合考慮時間成本和鍍層質量,本文選擇3ASD作為最佳電流密度。

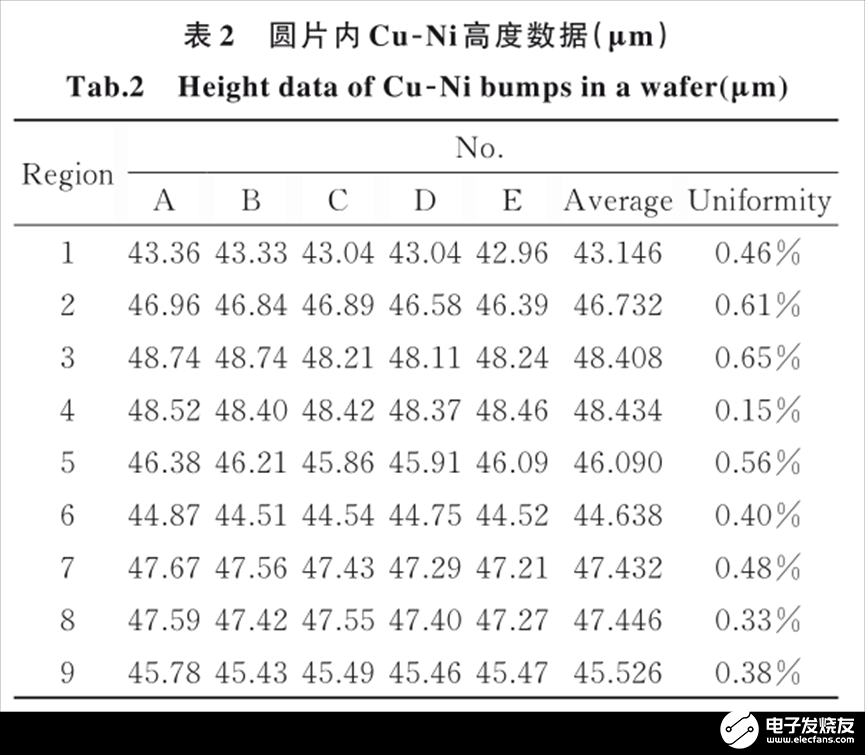

就芯片到圓片的堆疊(D2W)工藝而言,Die 內凸點高度的一致性較片內均勻性而言更為重要,故進一步對 3ASD 下九點區域處 5 連續 Cu/Ni凸點的一致性進行測量,此處選#2片,具體結果見表 2。結果顯示,雖然片內均勻性不佳,但各個區域內 Cu/Ni凸點高度波動不大,5連續凸點(A?E)高度均勻性最高不超過 0.7%,此處一致性計算方法為:最大偏差/均值/2×100%。

2.2 形貌分析

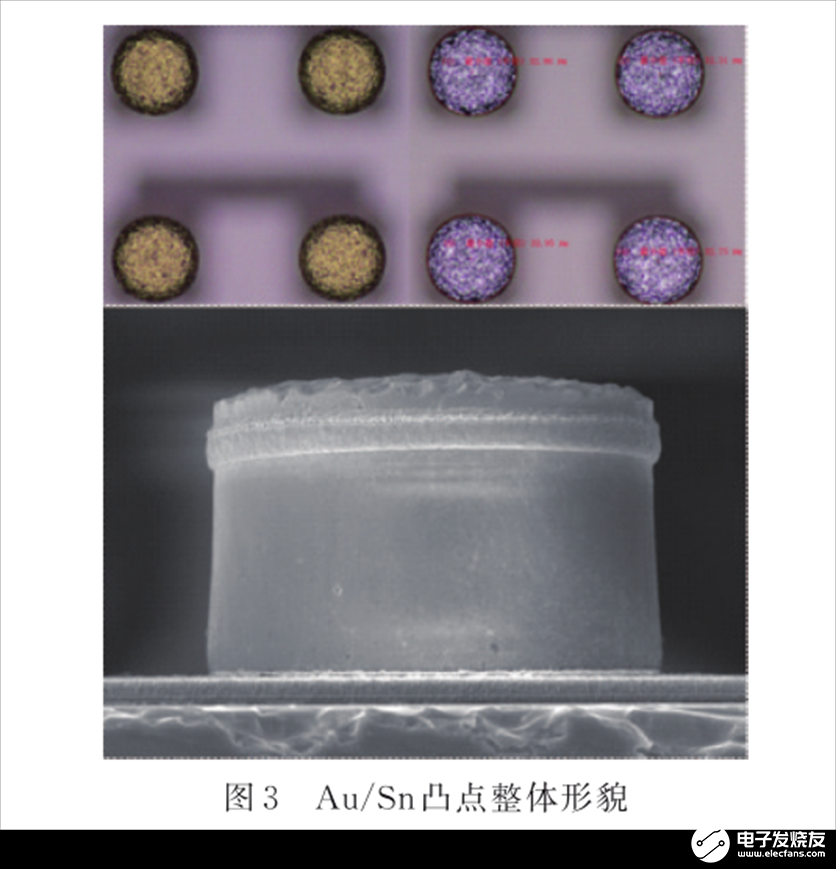

采用直流模式進行電沉積工藝,在 Cu柱頂端進一步沉積一層 Ni進而制備 Au/Sn 凸點,其中,Ni作阻擋層。電沉積工藝所得 Au/Sn 凸點如圖 3 所示,其直徑約為 65 μm,表面圓滑,尺寸均勻,可見分層明顯。需要注意的是,Au 電鍍液含氰,所用光刻膠存在不耐受的問題,故在電沉積 Au 時存在細微的外擴現象,因此,在工藝開發時需考慮外擴量,以保證 Au/Sn層厚度均滿足要求。

2.3 高度均勻性分析

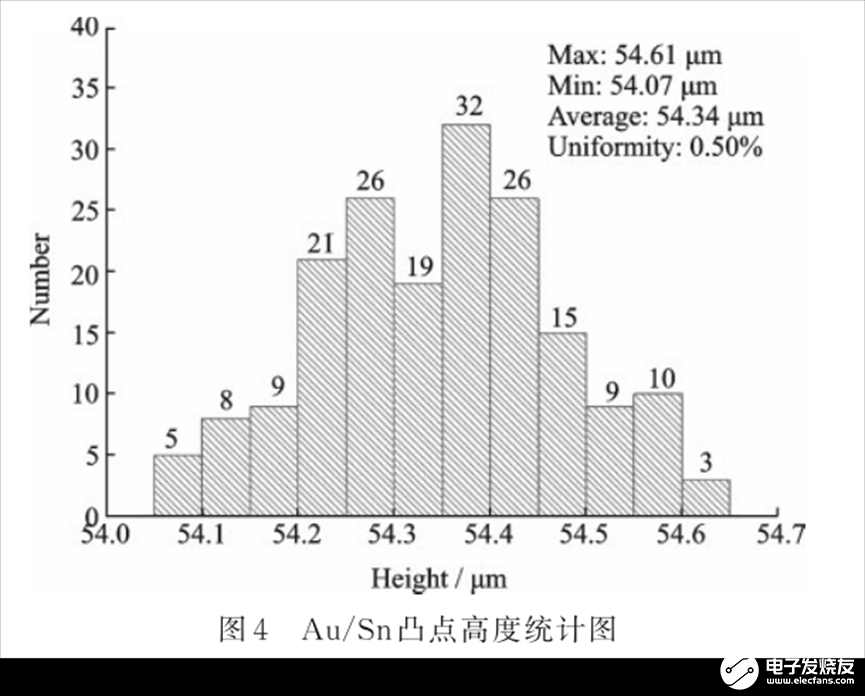

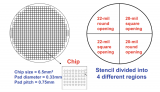

上述對最佳電流密度進行篩選時,但尚未對淀積 Au/Sn后整個凸點的一致性進行驗證,故在圓片內隨機抽取 1 個 Die,其中共包括 183 個凸點,利用臺階儀測量所有 Au/Sn 凸點的高度,結果見圖 4。測量結果顯示,在抽取的單個 Die內,Au/Sn凸點高度分布于 54.07~54.61 μm 之間,最大偏差不超過0.54 μm,高度均值為 54.34 μm,一致性高達 0.5%。

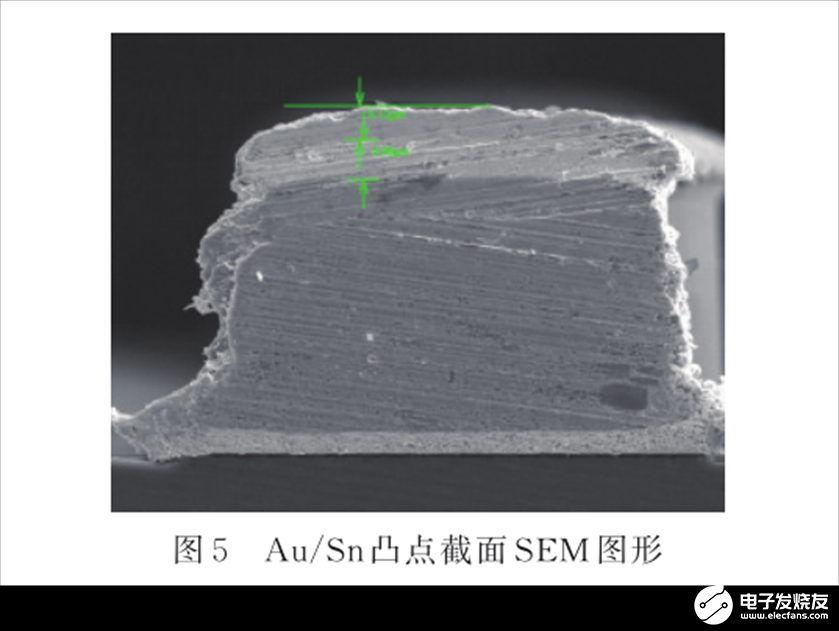

凸點整體高度關系著能否鍵合完全,而 Au/Sn凸點比例控制則決定著鍵合質量。為更精確地獲取 Au/Sn 各層高度,劃片后對其進行截面分析,得到如圖 5所示的 Au/Sn凸點剖面圖形。圖中,Cu層與 Au層之間存在清晰的界面,而 Ni層與 Cu層之間的界面并不清晰。一方面,Ni層相對較薄;另一方面,制樣過程中的切削在一定程度上對 Ni層有所掩蓋。同樣,由于自擴散作用的存在,Au相與 Sn相之間的界面相對模糊,若忽略測量誤差,Au相與 Sn相的厚度比例約為 5.95 μm/5.13 μm,接近于 1/1。

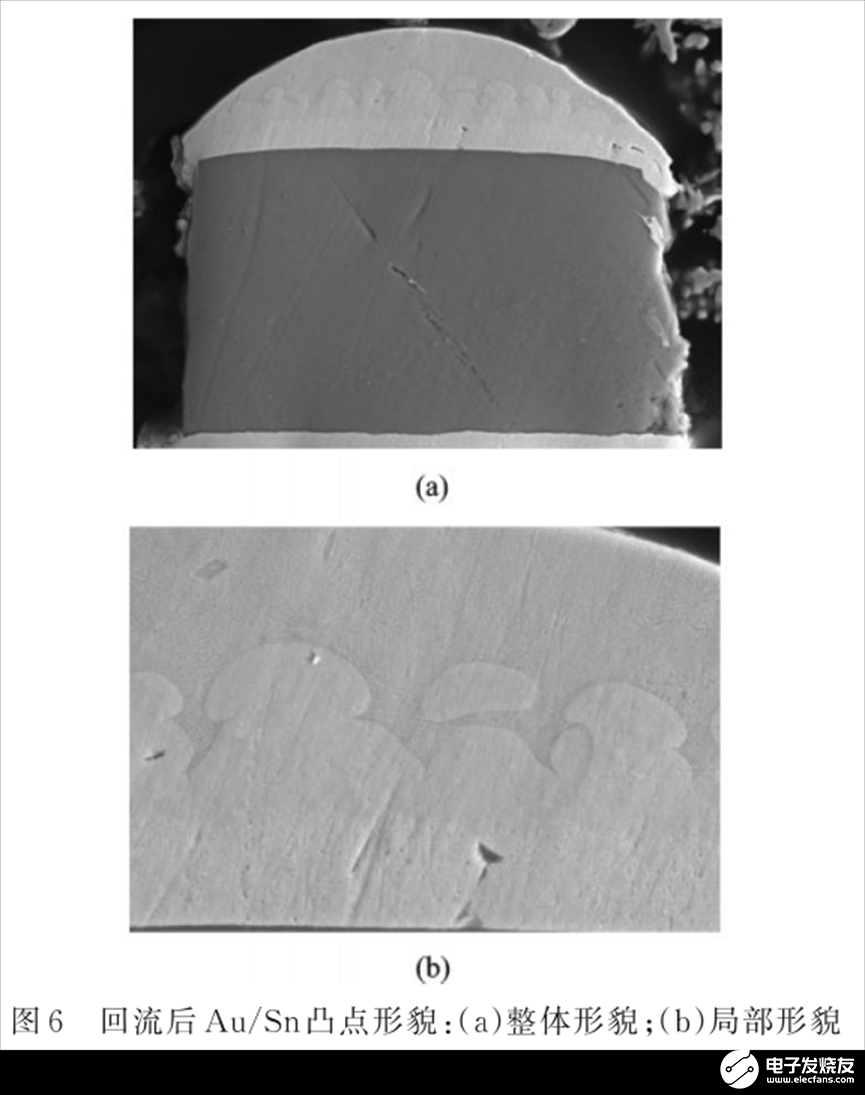

為更好地分析此工藝條件下 Au/Sn 凸點的比例 是 否 合 適 ,對 樣 品 進 行 了 回 流 ,回 流 條 件 為280℃,回流后得到的 Au/Sn 凸點形貌如圖 6 所示。由圖可見,回流后 Au/Sn 凸點呈“蘑菇狀”,表面圓滑,形成了明顯的 Au/Sn 共晶組織。同時,表層金屬 Sn 在回流后未沿凸點邊緣外溢,表明 Sn 含量相對合適。

2.4 剪切力測試

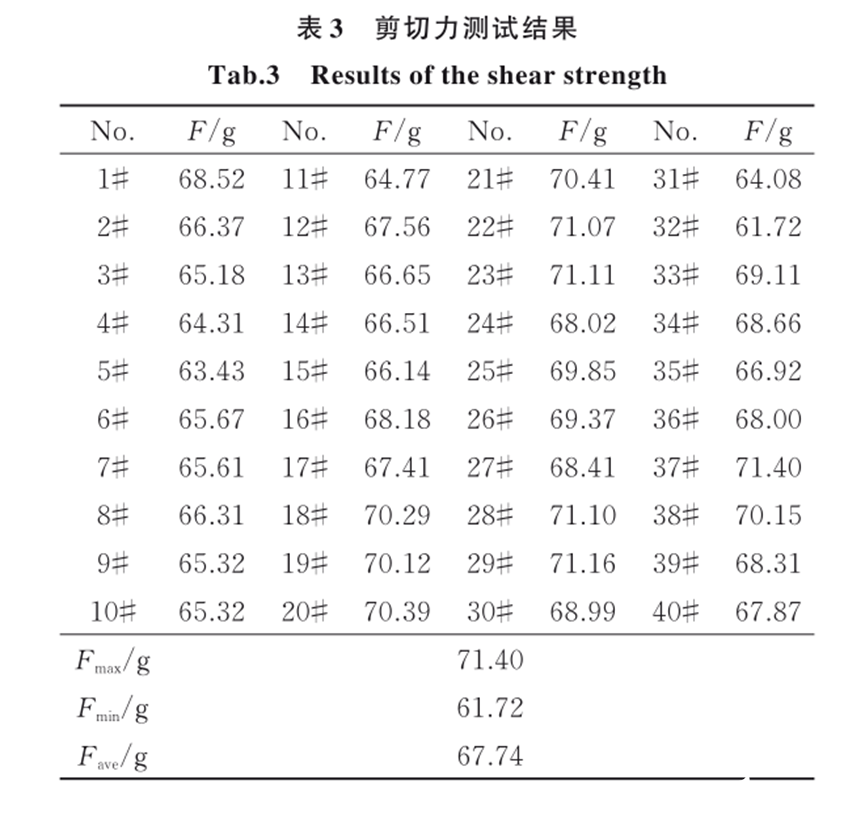

對于微凸點工藝可靠性而言,剪切強度是衡量封裝質量的一個重要指標。為評判圓片內凸點的整體剪切強度,隨機抽取 40只芯片,利用剪切測試儀對單個凸點的剪切力進行檢驗,剪切位置大致位于凸點自下而上 1/4處。實驗依據標準條款為檢驗標準GJB548B,測試數據如表 3所示。測試結果表明,單個凸點剪切力的平均值為67.74 g,最大值為71.40 g,最小值為 61.72 g,整體數值相差不大。由此可見,底層金屬 Cu 鍍層質量相對良好,個體差異較小,這一點同電沉積Cu后的表觀形貌觀測結果相吻合。

2.5 鍵合界面分析

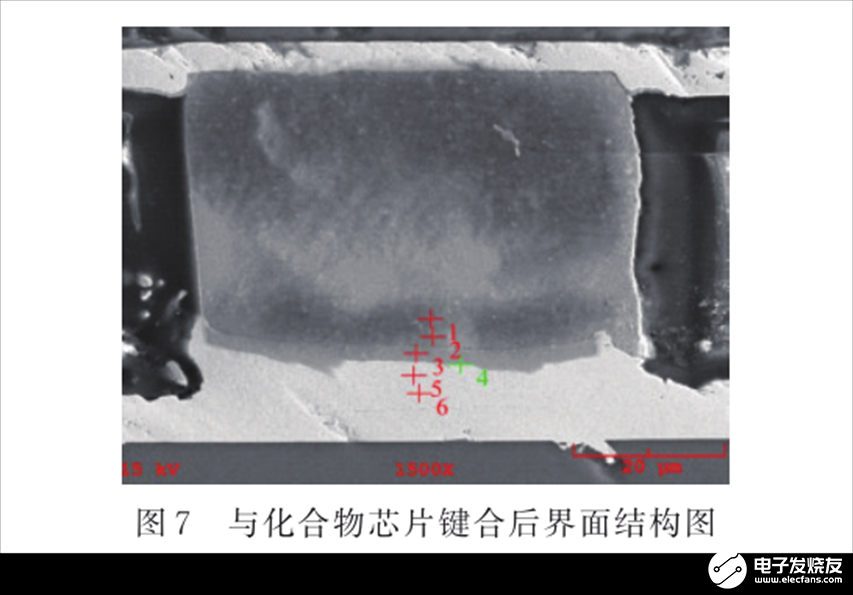

共晶鍵合的質量和可靠性很大程度上依賴界面金屬化合物(IMC)的組成及微結構。因此,將加工有 Au/Sn凸點的 Si基芯片與化合物芯片(另一側為 Au)進行鍵合,并對鍵合界面進行分析,鍵合界面如圖 7 所示。由圖可見,鍵合后可見明顯的 Cu?Ni分層及 Ni?Au/Sn 化合物分層,前者是因為電沉積Cu后未及時進行 Ni層的淀積,導致 Cu層表面存在氧化。同時,不存在表層金屬 Sn沿凸點邊緣大量外溢的現象,表明 Sn 含量相對合適,但因制樣問題界面較為粗糙,未見明顯的 Au/Sn共晶組織。

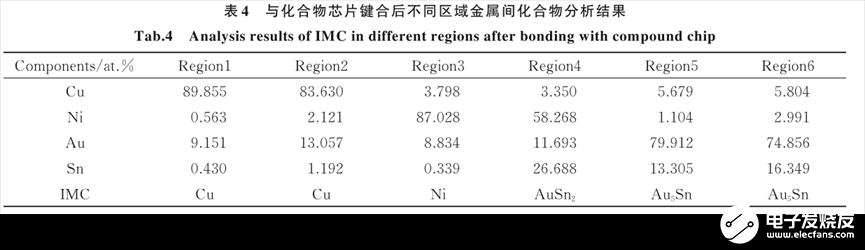

為更好地確定鍵合后界面金屬的組成,采用SEM 對選定的 7 個區域的界面金屬進行了成分分析,通過光譜確定界面共晶體的化學成分,從而判斷化合物組成構成形式,數據結果見表 4。由表可知,區域 1、2均為電沉積所制備的 Cu層;區域 3為電沉積所制備的 Ni層;區域 4為 Ni與 Au/Sn化合物界面,若僅考慮 Au/Sn 共晶相,因擴散作用形成了ε相[6](AuSn 2 ),該相具有較大的脆性;區域 5、6 皆形成了ξ相(Au 5 Sn),厚度相對較厚,可有效保證鍵合強度。Au/Sn相圖表明,富 Sn的 η(AuSn 4 )首先形成于217℃,ε相(AuSn 2 )形成于 252℃,δ相(AuSn)形成于281℃,而在278℃時,共晶組織隨著δ和ξ的液相反應開始轉變,隨著溫度的進一步升高,ξ相將繼續生長,且晶相生長機制不再發生變化。因 Ni的導熱性弱于Au,故在靠近 Ni層的區域 4 多形成 ε相。需要注意的是,區域 4處 γ相 AuSn 2 若與 Ni反應生成(Au,Ni,Sn)這一復雜的三相金屬間化合物,其焊接效果將大大降低,這一點仍需后續進行實驗論證。

2.6 推拉力測試

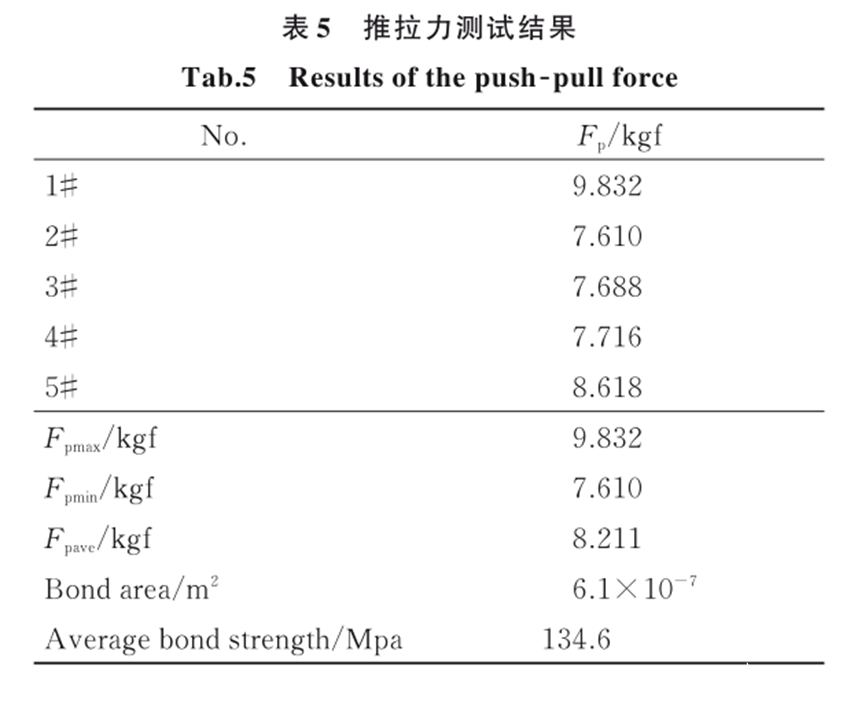

為更直觀地反映鍵合質量,加工有 Au/Sn凸點的 Si基芯片在熱回流后將其與化合物芯片(另一側為 Au)進行鍵合,并對鍵合后的整個芯片進行推拉力測試,此處鍵合方式為 D2W,具體推拉力測試結果見表 5。結果顯示,鍵合后的整個芯片推拉力均值為 8.211 kgf,最小值為 7.610 kgf,均在 7.5 kgf 以上,滿足>5.0 kgf的使用要求。同時進一步檢驗其鍵合質量,Au/Sn單個凸點的直徑約為 65 μm,化合物芯片與之對應的鍵合區域為邊長約 80 μm 的正方形,故單個鍵合區域面積為 3.318×103 μm 2 ,整個 Die內共 183 個凸點,整個鍵合區域面積為 6.10×10-7m2 ,平均鍵合強度為 134.6 Mpa。

3 結論

利用電沉積法在 Si 基板上以 Cu 作支撐層、Ni作阻擋層淀積微米級別的 Au/Sn凸點,制得的多層金屬凸點直徑約 60 μm、高度約 54 μm,其高度可控、尺寸可調,Die 內凸點高度一致性≤2%,有效改善了高尺寸下金屬凸點的均勻性,使得與異質芯片D2W 互連的可靠性提高。同時,通過前期對 Au/Sn比例的篩選,確定 Au/Sn 實際比例接近于 1/1 時效果相對較優,經回流后可形成表面圓滑的“蘑菇狀”凸點,共晶組織明顯,與化合物芯片鍵合后發現界面多為 Au 5 Sn 相。此外,剪切力和推拉力測試結果表明,最小剪切力為 61.72 g,整體數值相差不大,鍵合后推拉力達 7.5 kgf及以上,為實現不同體態芯片的異質異構集成打下了良好的基礎。

審核編輯 黃宇

-

芯片

+關注

關注

455文章

50714瀏覽量

423158 -

封裝

+關注

關注

126文章

7873瀏覽量

142894

發布評論請先 登錄

相關推薦

研究透視:芯片-互連材料

先進封裝中的翻轉芯片技術概述

濺射薄膜性能的表征與優化

先進封裝中互連工藝凸塊、RDL、TSV、混合鍵合的新進展

晶圓微凸點技術在先進封裝中的應用

無鉛共晶焊料在厚Cu凸點下金屬化層上的潤濕反應

用于表征光纖的熱受激發光

倒裝芯片封裝凸點剪切力測試實例,推拉力測試機應用全解析!

日月光半導體推出VIPack? 平臺先進互連技術協助實現AI創新應用

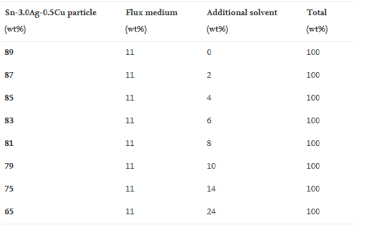

錫膏合金比例對焊接凸點的影響

用于不同體態芯片互連的凸點制備及性能表征

用于不同體態芯片互連的凸點制備及性能表征

評論