01

什么是去耦電容,為什么要去耦

1.簡介

去耦(decoupling)電容也稱退耦電容,一般都安置在元件附近的電源處,用來濾除高頻噪聲,使電壓穩定干凈,保證元件的正常工作。

2.分析

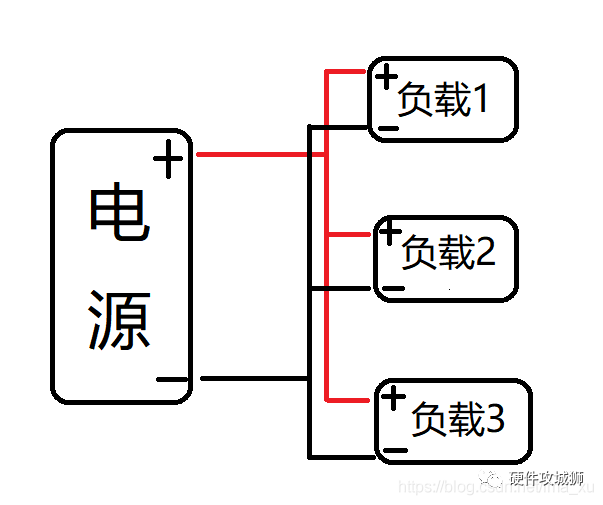

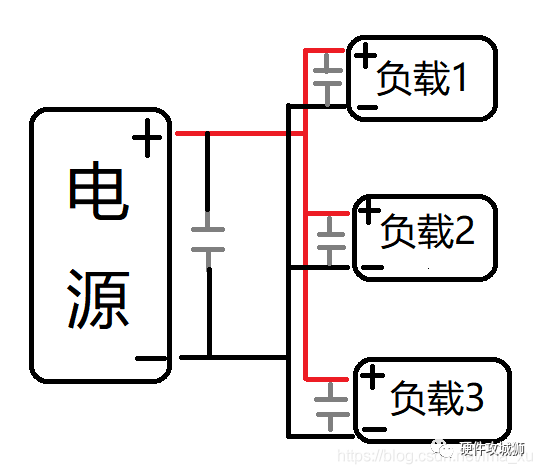

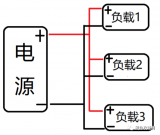

對于一個電路系統來說,一般有多個負載,這些負載的供電都來自于同一個電源

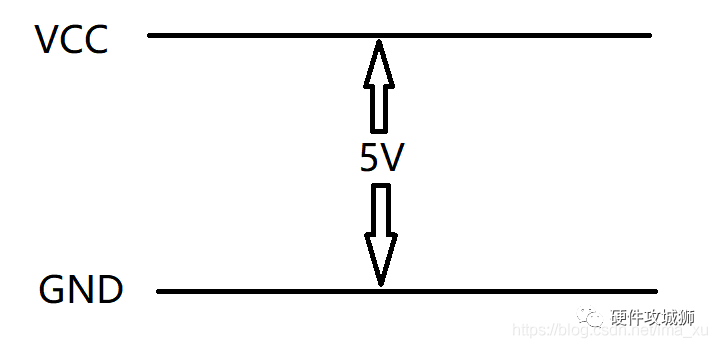

理想情況下,對于某個負載,電源應該是這樣子的

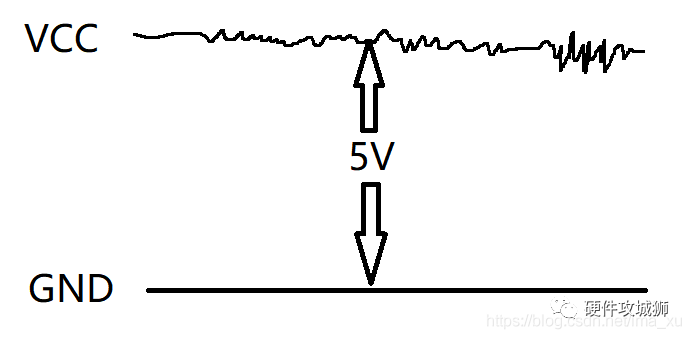

但是電路板上各個負載的工作都要動態地吸收電流,造成的供電電壓的不穩,變成了下面這樣子

也就是在5V的DC上疊加了各種高頻率的噪聲,這些噪聲是由于器件對供電電流的需求導致的電壓波動,可以看成是在DC 5V上“耦和”了由于器件工作帶來的AC噪聲。

這樣耦和了AC的DC供電電壓不僅會影響本負載區域內的電路的工作,也會影響到其它連接在同一個VCC上的其它負載的工作,有可能導致那些負載的電路工作出現問題。

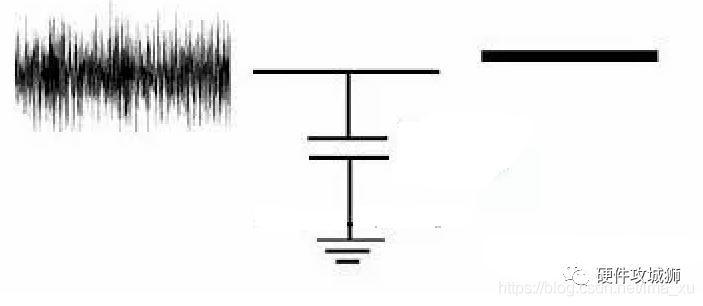

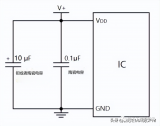

解決的方法就是在電源兩端并上一個小容量電容

從電源上看,沒有去耦電容的時候如左側的波形,加上了去耦電容之后變成了右側的樣子,供電電壓的波形變得干凈了,我們稱該電容的作用是去掉了耦和在干凈的DC上的噪聲,所以該電容被稱之為去耦電容,當然也可以被稱之為旁路(Bypass)電容,因為該電容將DC上耦和的噪聲給旁路到地上去了,只留下干凈的DC給后續的電路供電。

在整個系統每個負載都加一個去耦電容

至于電源輸入端,也要加上電容去耦做輸入濾波,彌補負載的濾波指數不夠的情況。

02

去耦電容的選用

1.問題

了解了什么是去耦電容后,那么問題來了:

究竟需要多大容量的電容才能達到去耦的效果?

這么多不同種類的電容選用哪種電容合適呢?

為什么在很多電路上看到針對一個電源管腳會有多個容量大小不同、類型也不相同的電容一起工作呢?

2.分析

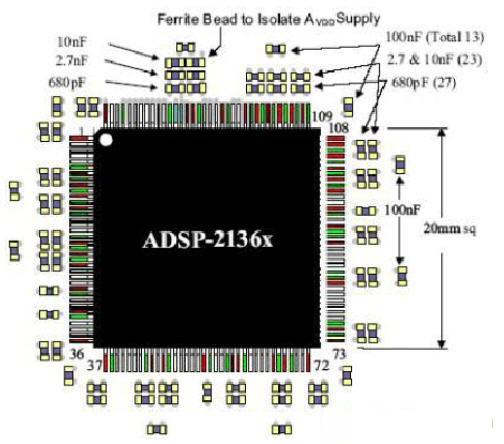

在一個芯片(比如FPGA/MCU)的電源管腳上需要多個不同容值、不同類型的電容并聯達到較好的去耦效果。

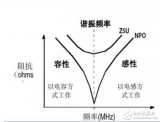

我們用來去耦的電容器(不論是哪一種)用于在電源線上的瞬態干擾期間快速提供電流,它們都不只有“電容”一個屬性,還有兩個阻礙電流流動的部分:電阻(ESR) - 無論頻率如何都呈現固定阻抗; 電感(ESL)- 隨著頻率的增加其阻抗也變得更高。而這三部分的值與電容的類型、容值、封裝都有很大的關系。

作為最常用的去耦神器 - 陶瓷電容具有很低的ESR和ESL(它們也很便宜),其次是鉭電容,提供適中的ESR和ESL,但相對有較高的電容/體積比,因此它們用于更高值的旁路電容,用于補償電源線上的低頻變化。對于陶瓷和鉭電容,較大的封裝通常意味著較高的ESL。

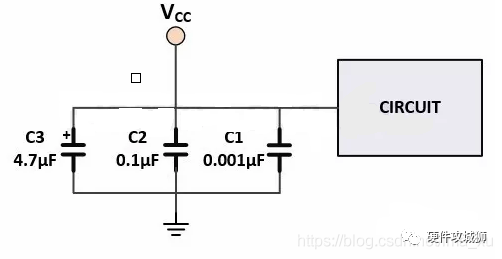

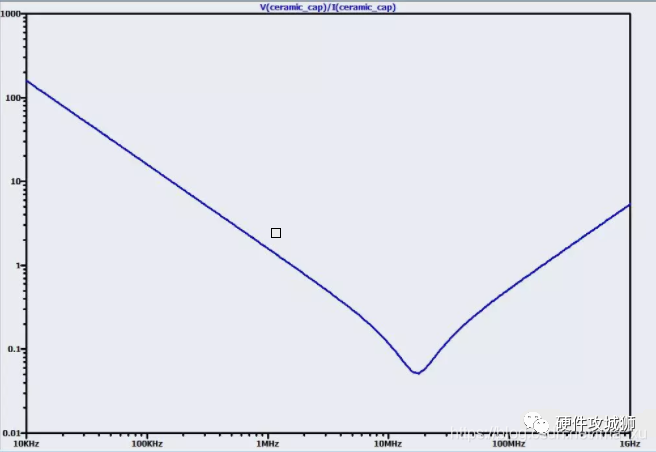

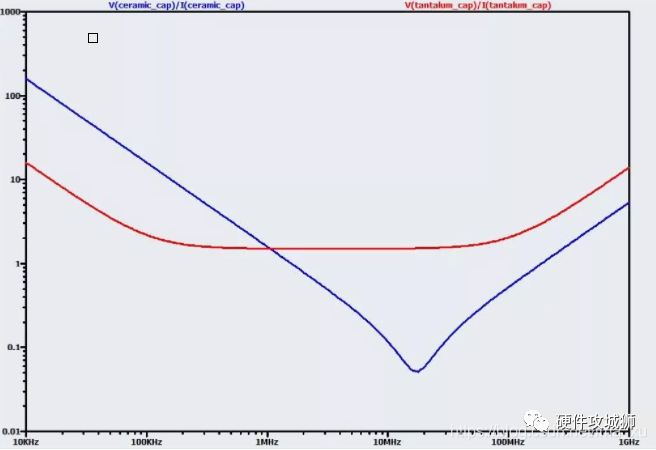

下圖顯示了0.1μF,封裝為0603的陶瓷電容器的阻抗,該電容器具有850pH的ESL和50mΩ的ESR:

正如前面討論的,去耦電容的作用就是平滑掉高頻變動的紋波電流,理想的電容器可以很容易地實現這一點,因為電容器的阻抗隨著頻率的增加而降低。但由于ESL的存在,在某個頻率下阻抗實際上隨頻率開始上升,這個頻率點又被稱為自諧振頻率點。我們再對比一下1μF的鉭電容器,它有2200pH的ESL和1.5Ω的ESR。

由于其較高的電容值,鉭電容器的阻抗在開始階段低于陶瓷的阻抗,但是較高的ESR和ESL的影響導致阻抗在100kHz附近變平,在1MHz-10MHz高于陶瓷電容的阻抗,在10MHz附近高出陶瓷的阻抗10倍。設想一下,如果電路中的噪聲頻率是在10MHz左右,即使鉭具有更高的電容,也不如放置一顆0.1μF的陶瓷電容更有效。如果我們要旁路掉更高頻率的噪聲,即使這個陶瓷電容也會存在太大的阻抗,我們就需要更低的ESL,也就是更小的封裝。

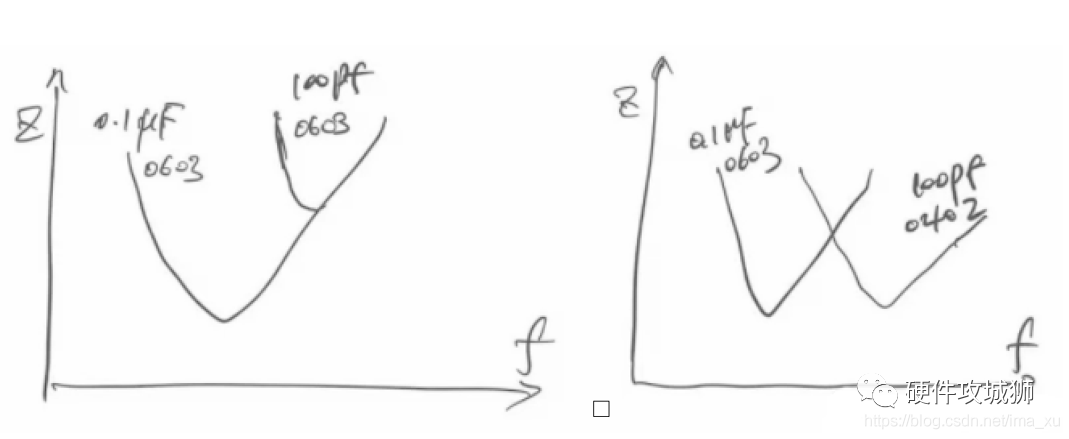

下圖左側表明兩個同樣是0603封裝的電容并不改變其對高頻噪聲的去偶性能,只是相當于去耦電容的容量為二者的和而已,后面看到這個容量對旁路噪聲的效果其實沒有什么差別;而下圖的右側,一個0.1μF封裝為0603的電容和100pF封裝為0402的電容并聯在一起,就可以覆蓋更寬的高頻范圍,能夠對兩個頻點的噪聲進行去偶。

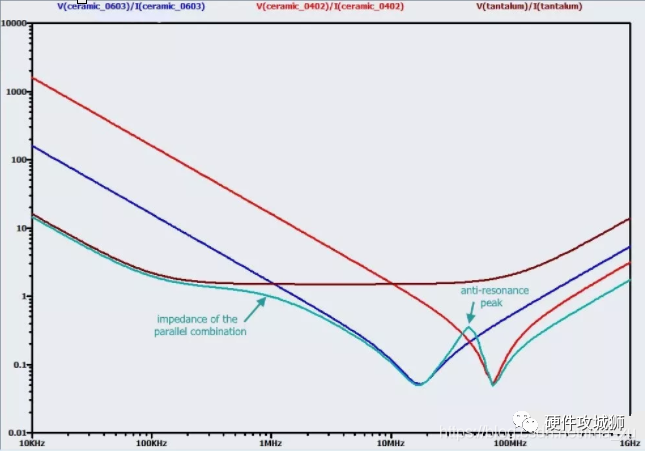

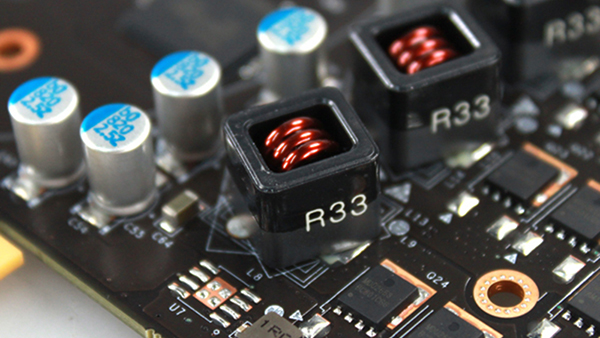

回到本篇文章第一個圖,在同一個電源管腳并聯了三個去耦電容:

4.7μF的鉭電容,對比較低頻率的噪聲濾除比較有效;

0.1μF、0603的陶瓷電容,對1-50MHz區域的噪聲濾除效果比鉭電容有效;

0.001μF、0402的陶瓷電容,對于50MHz以上的高頻噪聲濾除比較有效;

具體的噪聲頻段可以通過電路分析(時鐘頻率)以及測量進行確定,由此需要選用相應類型、相應封裝的電容進行去耦。多數的情況下我們用0.1μF陶瓷電容搭配一個鉭電容,就足以滿足系統對電源噪聲的去耦效果。

所以,不同類型,不同容量,不同封裝的電容,去耦的有效頻率段也是不同的

陶瓷電容相對與電解電容,最低的等效阻抗的頻率點更高

容量越小的電容,最低的等效阻抗的頻率點更高

封裝越小的電容,最低的等效阻抗的頻率點更高

03

去耦電容的PCB布局布線

1.原理

先看一個很形象的動圖,直觀體會一下一個電容放置位置不同起到的作用有多大的差異。

這張動圖傳遞了如下的信息:

在電源管腳上放置一個104(0.1μF)的電容能夠有效抑制電源上的噪聲,也就是能夠對電源噪聲去耦;

“電源 – 去耦電容 – 地”三點一線的距離越近,則去耦的效果越好;

相同材料的電容,即便電容容量減少為1/10,去耦的效果并不會有什么明顯變化,我們對于高頻去耦用同樣封裝的器件,容值為0.01μF、0.1μF、1μF效果相差不大;

同樣容值,貼片(SMD)封裝的電容比穿孔的電容效果更好,原因就是穿孔電容的管腳等效的電感要大很多,影響了去耦的效果;

電源平面和地平面的使用,一方面可以讓三點一線的路徑更短,而且兩個平面相當于一個大電容,也起到了去耦的作用

2. 實例

來看具體的實例

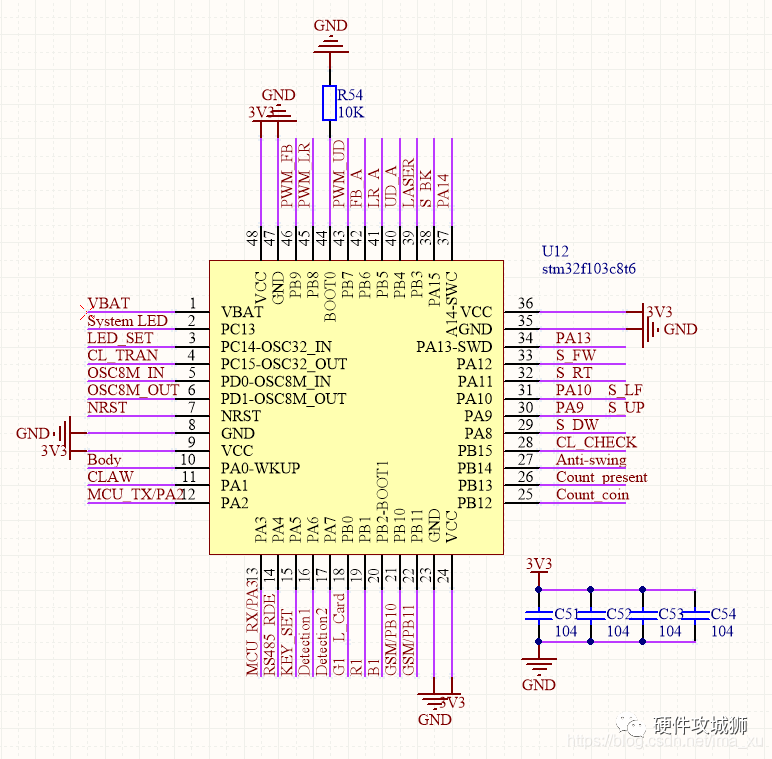

在常用單片機stm32f103c8t6最小系統中,常常有這樣四個去耦電容,分別對應芯片的四對供電引腳。

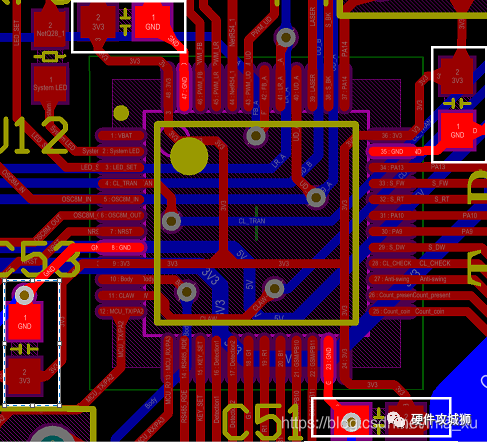

而在PCB中,這四個電容(圖中白色框框中)在擺放合理的情況下越靠近mcu越好。

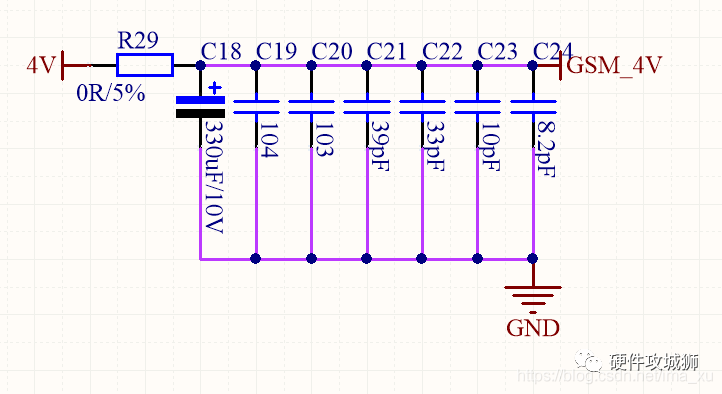

而在多電容去耦(對電源穩定要求極為苛刻的電路中),比如GSM的電源,需要多個不同容量/種類的電容。

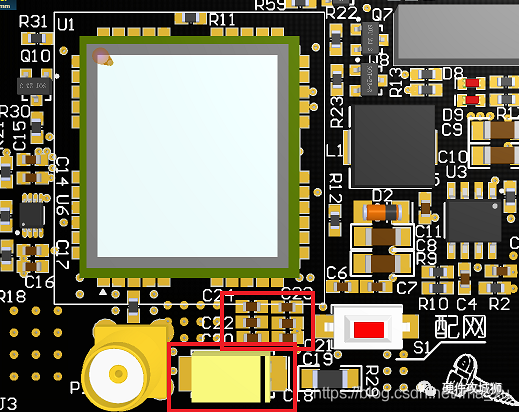

對應下面紅框框出的6+1個電容,其中越小的電容應當越靠近GSM的電源腳,比如C24是8.2pF,離GSM最近,C19是100nf,離GSM較遠,最遠的則是容量最大的330uf的鉭電容

04

總結

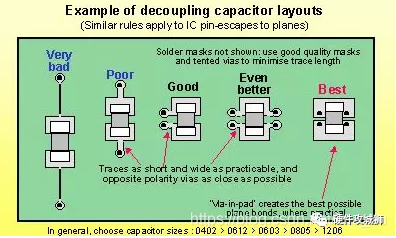

下面的圖是去耦電容通過過孔與地進行連通的方法比較,從最左側的效果最差依次編號,直到最右側效果最佳,當然具體采用那種方式還要取決于其它一些因素,綜合考慮后做一個折衷。

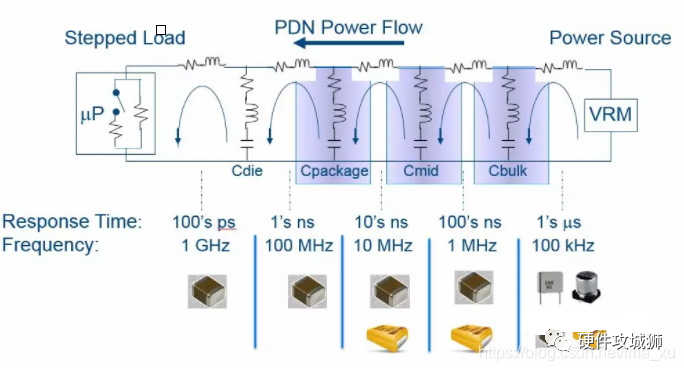

下圖是一個實際電子產品系統的供電分布網絡,為了強調噪聲的起源(最左側),把電源模塊(VRM)放到了最右側。PCB上的走線、過孔、相關的器件引腳等都會產生寄生電阻、電感等,在圖中以R+L的方式等效表達出來。在這個圖中可以看出針對IC器件內部(Die)、針對整個IC器件(Package)、針對某一個功能模塊中的電路單元都有相應的去耦電容,最左側(靠近內核)采用頻率響應很高的小容值、小封裝的陶瓷電容,到右側則是低頻率、容量比較大的電解電容。

總之一句話:去耦電容的PCB布局擺放原則是最小化電阻,最小化電感。

(部分參考自電子開發學習)。

審核編輯:黃飛

-

電容器

+關注

關注

64文章

6573瀏覽量

102028 -

pcb

+關注

關注

4357文章

23439瀏覽量

407287 -

陶瓷電容器

+關注

關注

1文章

223瀏覽量

25790 -

去耦電容

+關注

關注

11文章

319瀏覽量

22845 -

電路系統

+關注

關注

0文章

71瀏覽量

13083

原文標題:十分透徹!詳解去耦電容!文科生看完都理解了!

文章出處:【微信號:mcu168,微信公眾號:硬件攻城獅】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

PCB布局時去耦電容擺放經驗分享

什么是去耦電容?為什么要去耦?

PCB布線技巧:去耦電容的擺放

去耦電容的容值計算和布局布線

評論