sr鎖存器不定狀態怎么理解

SR鎖存器,結構簡單,一般由兩個與非門或者兩個或非門組成,原理比較簡單,就是具有保持和鎖存電平的作用,但是也有缺陷不定態存在,很多書上指出只要輸入滿足SR=1,輸出就是不確定狀態,但事實真的如此?

1 SR鎖存器原理

先根據電路粗略講解一下SR鎖存器功能,熟悉的同學可以跳過這部分。

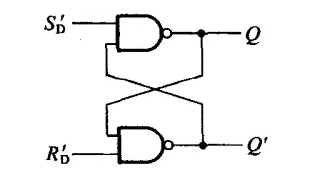

1圖1 與非門構成的SR鎖存器

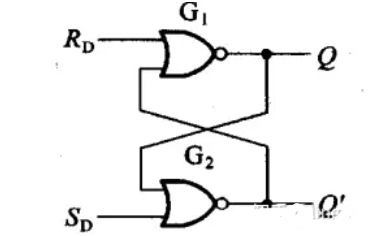

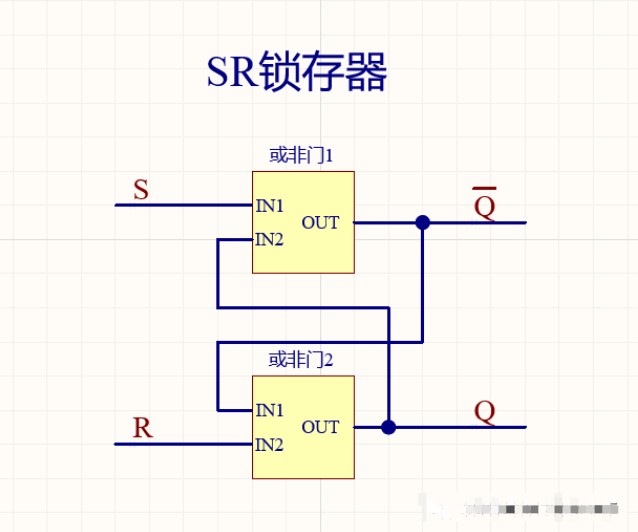

圖2 或非門構成發SR鎖存器

上面兩圖分別是使用兩個與非門和兩個或非門組成的SR鎖存器,本文以圖2兩個或非門組成的SR鎖存器進行功能分析。

當SD=1,RD=0時,或非門G2一端以SD作為輸入,故G2輸出低電平,G2和RD作為G1的輸入,所以G1輸出為高電平,此時SR鎖存器輸出Q端為高電平,Q‘為低電平。Q的次態與Q的現態無關,輸出端Q均為高電平,故SD被稱為置數端。

當SD=0,RD=1時,因為或非門G1的RD端輸入高電平,所以G1輸出端輸出低電平,或非門G2輸入均為低電平,則Q非為高電平,故SR鎖存器Q輸出為低電平,Q’輸出高電平。Q的次態與Q現態無關,輸出端均為低電平,RD被稱為SR鎖存器清零端。

當SD=0,RD=0,Q的現態為0時,則Q‘的次態為高電平,進而推出或非門G1的輸出為低電平,所以Q的次態為0;當Q的現態為1時,則或非門G2的輸出為0,或非門G1將RD和或非門G2輸出作為輸入,所以或非門G1輸出高電平,即Q的次態為高電平,由此可知,Q端的次態和現態保持相同,所以當SD與RD端輸入數據均無效時,SR鎖存器具有保持功能。

SR鎖存器不定態

分析1:SD端與RD端均有效,即SD=1且RD=1時,由于兩個或非門G1,G2均有一個輸入端為高電平,則Q和Q‘均為低電平,此時SR鎖存器的輸出是確定的,并不是所謂的不定態。

分析2:繼分析1,當SD端和RD端輸入均為高電平時,Q與Q’均輸出低電平,此時SD由高電平變為低電平,RD保持高電平。由于或非門G2輸入均為低電平,所以G2輸出高電平,即Q‘為高電平。而或非門G1輸入均為高電平,故G1輸出為低電平,即Q為低電平,此時SR鎖存器的輸出也是確定的。

分析3:繼分析1,當SD端和RD端輸入均為高電平時,Q與Q’均輸出低電平,此時RD由高電平變為低電平,SD保持高電平。則或非門G1輸入均為低電平,G1輸出則為高電平,即Q輸出高電平。

SR鎖存器不定狀態的出現,主要是由于理想狀態與實際工作狀況之間的差異。理論上,SR鎖存器的各種組合都有明確的輸出狀態,但在實際使用中,由于器件本身的差異以及信號噪聲的影響,每個端口從“0邏輯電平電壓”升高到“1邏輯電平電壓”的時間并不相同。

具體來說,當SR同時從00變為11時,由于上述因素的影響,中間會引入“01”或“10”這樣的中間狀態,而具體引入哪種狀態無法確定,這就是“狀態不定”的根本原因。

因此,在實際應用中,需要避免SR同時為高電平的情況,以防止SR鎖存器進入不定狀態。同時,對于電路的設計和布局也需要進行細致的考慮,以減少信號噪聲和器件差異對SR鎖存器工作的影響。

此外,時序問題也可能導致SR鎖存器出現不定狀態。RS鎖存器是異步的,對輸入的變化沒有時鐘信號的依賴,輸入信號的瞬時變化可能導致不確定的輸出。

審核編輯:黃飛

-

鎖存器

+關注

關注

8文章

924瀏覽量

42282 -

或非門

+關注

關注

0文章

33瀏覽量

15570 -

高電平

+關注

關注

6文章

201瀏覽量

22009 -

時序問題

+關注

關注

0文章

3瀏覽量

2017 -

與非門

+關注

關注

1文章

130瀏覽量

13084

發布評論請先 登錄

評論