共讀好書

劉倩,邱忠文,李勝玉

(中國(guó)電子科技集團(tuán)公司第二十四研究所)

摘要:

為了響應(yīng)集成電路行業(yè)更高速、更高集成度的要求,硅通孔技術(shù)(ThroughSilicon Via, TSV)成為了半導(dǎo)體封裝核心技術(shù)之一,解決芯片垂直方向上的電氣和物理互連,減小器件集成尺寸,實(shí)現(xiàn)封裝小型化。本文介紹了硅通孔技術(shù)的可靠性,包括熱應(yīng)力可靠性和工藝技術(shù)可靠性兩方面。過大熱應(yīng)力可能會(huì)導(dǎo)致通孔側(cè)壁粗糙,并影響內(nèi)部載流子遷移率,從而使器件功能失效。可以通過采用熱硅通孔、淺層溝槽隔離技術(shù)、合理調(diào)整通孔結(jié)構(gòu)和深寬比來減小熱應(yīng)力。TSV 工藝可靠性主要體現(xiàn)在通孔側(cè)壁光滑程度和通孔導(dǎo)電材料填充效果,可通過循環(huán)氧化、在電鍍液中加入抑制劑和加速劑以及熔融法進(jìn)行改善。

引言

在過去的半個(gè)世紀(jì)里,摩爾定律引導(dǎo)著集成電路行業(yè)朝著低功耗和高性能的目標(biāo)邁進(jìn),推動(dòng)著科學(xué)技術(shù)的發(fā)展。但隨著集成電路的不斷發(fā)展和人們對(duì)電子產(chǎn)品的需求不斷提高,對(duì)芯片能夠?qū)崿F(xiàn)越來越多功能的要求也更加急迫,通過不斷縮小芯片特征尺寸來提高系統(tǒng)集成程度和處理速度的局限性就凸顯出來。當(dāng)芯片的尺寸不斷減小,會(huì)出現(xiàn)散熱降低、泄露電流增加等問題,導(dǎo)致器件性能參數(shù)漂移,器件甚至直接失效[1] 。為了克服這些問題,可以從兩方面進(jìn)行研究:一方面積極研究使用新型材料和結(jié)構(gòu)來設(shè)計(jì)制造器件,實(shí)現(xiàn)摩爾定律的延續(xù);另一方面,不再局限于傳統(tǒng)的二維結(jié)構(gòu),在平面的基礎(chǔ)上向垂直方向發(fā)展,實(shí)現(xiàn)高密度小尺寸封裝。三維封裝技術(shù)的發(fā)展和成熟使得器件封裝密度的不斷提高成為了可能,如何將多個(gè)芯片在垂直方向上進(jìn)行層疊并實(shí)現(xiàn)電氣互連成為了未來集成電路發(fā)展的重要方向之一,即芯片互連。

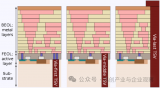

為了在芯片與芯片、芯片與基板之間進(jìn)行信號(hào)的傳遞,芯片互連技術(shù)對(duì)于實(shí)現(xiàn)物理連接和電氣連接都有不可或缺的重要作用。其中,硅通孔技術(shù)是實(shí)現(xiàn)這種物理和電氣連接的關(guān)鍵技術(shù)之一,該技術(shù)是在垂直方向上堆疊的晶圓之間制作通道,在通孔內(nèi)進(jìn)行高導(dǎo)電性材料的填充,晶圓以較大密度堆疊在一起,從而能夠?qū)崿F(xiàn)目前電子器件多功能集成且封裝尺寸更小的技術(shù)要求。因此,TSV 也被稱第四代互連封裝技術(shù),為加快三維集成封裝技術(shù)的迅速發(fā)展提供了可能[2] 。

1 可靠性概述

目前,TSV 技術(shù)主要是以小孔徑尺寸和高深寬比通孔為發(fā)展目標(biāo)和方向,不僅帶來了集成電路行業(yè)發(fā)展的機(jī)遇,也迎來了新的挑戰(zhàn)。作為實(shí)現(xiàn)晶圓或芯片之間電氣和物理連接的重要技術(shù),TSV 技術(shù)對(duì)于三維封裝技術(shù)的實(shí)現(xiàn)以及多系統(tǒng)整合有著不可替代的作用。因此,TSV 技術(shù)的高可靠性對(duì)于高集成度芯片可靠性發(fā)展至關(guān)重要,其可靠性涉及了熱應(yīng)力和工藝等方面。

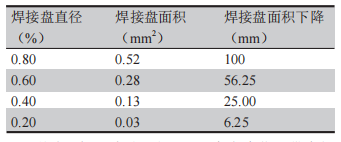

隨著三維封裝技術(shù)的應(yīng)用和芯片封裝密度的增大,芯片工作時(shí)不能迅速有效散熱,會(huì)引起嚴(yán)重的熱應(yīng)力問題[3] 。銅、硅和二氧化硅的熱膨脹系數(shù)之間有較大的差別,這種不同材料間熱膨脹系數(shù)的差距引起的熱應(yīng)力會(huì)使得二氧化硅和填充材料之間的界面發(fā)生分層,導(dǎo)致器件出現(xiàn)性能參數(shù)漂移、使用壽命縮短等問題,會(huì)嚴(yán)重影響器件的使用可靠性 [4, 5] 。另外,在高溫下,硅通孔的存在引入的熱應(yīng)力會(huì)使器件有源區(qū)受到影響,使得器件內(nèi)部載流子遷移率發(fā)生改變,也可能會(huì)引起器件發(fā)生重大的可靠性問題[6] 。根據(jù)研究顯示,孔徑大的硅通孔會(huì)產(chǎn)生較大的熱應(yīng)力,這種熱應(yīng)力的存在會(huì)改變晶體管內(nèi)部的載流子遷移率。相關(guān)數(shù)據(jù)表明,在 100 MPa 應(yīng)力的作用下,晶體管內(nèi)部載流子的遷移率能達(dá)到 7 % [7] 。因此,解決硅通孔引起的熱應(yīng)力問題對(duì)于保證器件的正常使用至關(guān)重要。

從工藝角度考慮,目前通用的硅通孔刻蝕技術(shù)有兩種,干法刻蝕和濕法刻蝕,其中干法刻蝕工藝中常用的是 Bosch 刻蝕。先使用六氟化硫氣體與硅刻蝕反應(yīng)形成通孔,然后用八氟環(huán)丁烷氣體與之反應(yīng),在通孔的內(nèi)側(cè)和底部形成鈍化膜,再使用六氟化硫刻蝕鈍化層和硅層[8] 。這種刻蝕和鈍化過程相間進(jìn)行的干法刻蝕方法會(huì)導(dǎo)致通孔的內(nèi)側(cè)壁粗糙,產(chǎn)生扇貝紋,如圖 1 所示,進(jìn)而妨礙了后續(xù)其他導(dǎo)電材料的填充,致使導(dǎo)電材料和硅層之間的界面不平滑,從而嚴(yán)重影響了 TSV 的導(dǎo)電性能,進(jìn)而影響芯片的功能和使用壽命[9] 。因此,通過改進(jìn)當(dāng)前的技術(shù)工藝,可以進(jìn)一步提高 TSV 技術(shù)的可靠性,從而提高三維封裝可靠性。

2 熱應(yīng)力可靠性

2.1 采用 TTSV 降低 TSV 熱應(yīng)力

對(duì)于三維集成技術(shù)來說,實(shí)現(xiàn)了多層疊堆和高集成度,卻不可避免地影響芯片的散熱問題。從提高導(dǎo)熱性能方面出發(fā),可以采用熱硅通孔(thermal through siliconvia,TTSV)來促進(jìn)垂直方向上堆疊的芯片之間產(chǎn)生的熱量傳遞,增強(qiáng)芯片的散熱,以減小熱應(yīng)力的產(chǎn)生。通過插入具有銅芯和氧化物襯底的 TTSV,最高芯片溫度將顯著降低約 62 ℃[10] 。不同于傳統(tǒng)的 TSV,TTSV 有較高的熱傳導(dǎo)率,能夠迅速傳導(dǎo)熱量。崔玉強(qiáng)[11]等通過有限元方法仿真發(fā)現(xiàn),與使用鎢、銅作為 TTSV 導(dǎo)熱芯相比,使用碳納米管作為 TTSV 的導(dǎo)熱芯材料能夠明顯降低芯片溫度。盡管與其他填充材料相比,碳納米管的傳熱性能十分突出,在芯片降溫方面優(yōu)勢(shì)顯著,但是其在實(shí)際應(yīng)用當(dāng)中仍然有較多問題函待解決,例如,碳納米管的成本與性能之間的矛盾,且工藝復(fù)雜等。

2.2 采用 STI 降低 TSV 熱應(yīng)力

目前常用的改善器件內(nèi)部熱應(yīng)力問題的方法是在硅通孔附近劃分一個(gè)保留區(qū)域(keep-outzone,KOZ) [12] ,一般不會(huì)將對(duì)應(yīng)力敏感的器件放置在載流子遷移率大于5 %的區(qū)域內(nèi)。這種方案雖然改善了熱應(yīng)力對(duì)載流子遷移率的消極影響,卻使得襯底面積被大量浪費(fèi),也不能適應(yīng)高集成度的需求。一種淺層溝槽隔離技術(shù)(ShallowTrench Isolation,STI)可以在提高襯底面積利用率的同時(shí)更有效地降低硅通孔熱應(yīng)力的產(chǎn)生,這種 STI 技術(shù)是通過在硅通孔和有源區(qū)之間刻蝕一圈淺層溝槽來減小熱應(yīng)力。先在半導(dǎo)體基底上沉淀一層氮化硅,接著通過腐蝕在 KOZ 區(qū)得到一個(gè)溝槽,然后將溝槽進(jìn)行氧化,沉淀二氧化硅,最后對(duì)側(cè)壁進(jìn)行平坦化,提高其光滑程度。相關(guān)試驗(yàn)發(fā)現(xiàn),這種技術(shù)會(huì)引起硅通孔周圍產(chǎn)生壓縮應(yīng)力[13] ,將該應(yīng)力充分利用,使其與硅通孔所引入的熱應(yīng)力進(jìn)行疊加抵消,可以明顯削弱熱應(yīng)力。通過仿真計(jì)算對(duì)比使用 STI 技術(shù)的 TSV 和沒有 STI的 TSV 的 KOZ區(qū),STI 技 術(shù) 使 得 KOZ 減 小 了(0.644~4.346)μm(10.3~25.8)% [14] 。事實(shí)證明使用淺層溝槽隔離技術(shù)可以有效減小 KOZ 區(qū)域大小,從而在不浪費(fèi)面積的同時(shí),降低了熱應(yīng)力的負(fù)面影響。孫漢

[15]等人為了解決大尺寸硅通孔結(jié)構(gòu)熱應(yīng)力問題,設(shè)計(jì)了一種熱應(yīng)力釋放槽結(jié)構(gòu)。通過仿真分析發(fā)現(xiàn),由于釋放槽的存在,TSV 槽外的熱應(yīng)力約為沒有釋放槽 TSV 的 50 %,同時(shí)還減小了 KOZ區(qū)的面積,提高襯底面積使用率,且應(yīng)力釋放槽與硅通孔的距離越遠(yuǎn),基片表面熱應(yīng)力的減小程度越大。

2.3 不同深寬比和通孔結(jié)構(gòu)的影響

采用有限元軟件對(duì)銅填充 TSV 進(jìn)行仿真分析,得出其等效熱應(yīng)力大小及分布。仿真分析表明,最大熱應(yīng)力出現(xiàn)在金屬層與介質(zhì)層的界面處,且最大熱應(yīng)力點(diǎn)與最高溫度值點(diǎn)相對(duì)應(yīng)。當(dāng)硅通孔的孔徑大小不變時(shí),隨著通孔深度的不斷增大,其產(chǎn)生的最大熱應(yīng)力也隨之減小,同時(shí)通孔附近的最高溫度值也隨之降低,這說明通孔越深,TSV 的散熱性能越強(qiáng);當(dāng) TSV 深度保持不變,通孔的尺寸越小時(shí),其熱應(yīng)力越小,即硅通孔的深寬比越大,產(chǎn)生的熱應(yīng)力就越小,其散熱功能越強(qiáng)[17, 18] 。

通孔結(jié)構(gòu)對(duì)于熱應(yīng)力也有一定影響。將圓柱型 TSV與圓臺(tái)型 TSV 的熱應(yīng)力等效值進(jìn)行對(duì)比,發(fā)現(xiàn)圓臺(tái)型TSV 熱應(yīng)力比圓柱型的大,且圓臺(tái)型的平均溫度也比圓柱型的高,這表明圓柱型硅通孔能夠更好的進(jìn)行散熱。另外,根據(jù)熱應(yīng)力云圖可以發(fā)現(xiàn),圓臺(tái)型 TSV 的熱應(yīng)力主要集中在小孔徑處,而圓柱型 TSV 的熱應(yīng)力主要集中在上表面。總的來說,圓柱型硅通孔的總體散熱性能明顯強(qiáng)于圓臺(tái)型,但圓臺(tái)型硅通孔的熱應(yīng)力更集中,在大孔徑處的熱應(yīng)力反而低于圓柱型的[19] 。掌握通孔結(jié)構(gòu)和不同深寬比通孔對(duì) TSV 熱應(yīng)力的影響,可以更好地進(jìn)行硅通孔散熱方面的設(shè)計(jì),對(duì)其可靠性也具有積極的指導(dǎo)作用。

3 工藝可靠性

3.1 降低通孔內(nèi)壁扇貝紋起伏

硅片經(jīng)過刻蝕工藝形成硅通孔,不同的刻蝕工藝會(huì)得到不同光滑程度的通孔內(nèi)側(cè),而內(nèi)側(cè)的光滑程度對(duì)于后續(xù)進(jìn)行金屬導(dǎo)電材料的填充有著直接的影響,填充效果對(duì)于 TSV 的物理和電氣連接可靠性來說至關(guān)重要。目前廣泛使用的硅通孔刻蝕技術(shù)之一是Bosch 刻蝕技術(shù),但該方法不可避免地會(huì)在通孔內(nèi)壁形成扇貝紋[20] 。通孔內(nèi)壁的光滑程度越高,硅通孔引起的平均熱應(yīng)力也會(huì)越小。同時(shí),內(nèi)壁扇貝紋的形成會(huì)引起峰值應(yīng)力的產(chǎn)生,其值明顯高于平均熱應(yīng)力,這種現(xiàn)象的出現(xiàn)使得峰值應(yīng)力所在區(qū)域的應(yīng)力差異過大,這種應(yīng)力值差異甚至?xí)鸸柰椎慕Y(jié)構(gòu)失效,嚴(yán)重影響 TSV 技術(shù)的可靠性[8] 。因此,降低通孔內(nèi)壁扇貝紋的出現(xiàn)對(duì)于提高硅通孔以及芯片的可靠性是非常重要的。

Morikawa 等人[21]采用平面磁中性環(huán)路放電等離子體深孔刻蝕技術(shù),雖然能夠得到高深寬比和無扇貝紋的通孔,但通孔側(cè)壁仍然具有一定的粗糙度。趙鴻[22]等人基于電感耦合等離子體(ICP)技術(shù)也實(shí)現(xiàn)了小孔徑、高深寬比通孔的刻蝕,并且,使用 ICP 技術(shù)能夠降低襯底溫度,同時(shí)縮短刻蝕和鈍化時(shí)間,削弱了扇貝紋起伏幅度,但依然不能完全消除。采用反應(yīng)離子刻蝕(RIE)技術(shù)避免了通孔頂部的側(cè)壁波紋,與傳統(tǒng)的 Bosch 刻蝕工藝進(jìn)行對(duì)比發(fā)現(xiàn),最大均方根粗糙度由 15.1 nm 降至6.89 nm [23] 。采用循環(huán)氧化法也可以有效降低扇貝紋的出現(xiàn)。先將硅片進(jìn)行熱氧化操作,之后通過濕法腐蝕進(jìn)行清洗,可以得到較為光滑的通孔內(nèi)側(cè)壁。經(jīng)過重復(fù)循環(huán)高溫?zé)嵫趸透g二氧化硅的過程 , 可明顯減小扇貝紋尺寸,得到更加光滑的硅通孔內(nèi)壁[24] 。

3.2 導(dǎo)電材料填充技術(shù)

硅是一種半導(dǎo)體材料,通過在通孔中進(jìn)行導(dǎo)電物質(zhì)的填充來實(shí)現(xiàn)硅通孔的導(dǎo)電性能,其中銅是一種被廣泛使用的導(dǎo)電物質(zhì)。通孔導(dǎo)電材料填充技術(shù)的主要關(guān)鍵點(diǎn)在于一方面要能夠高效率、低成本地進(jìn)行通孔導(dǎo)電材料的填充,另一方面又要保障填充后通孔內(nèi)部無空洞,且在受到劇烈溫度變化刺激時(shí),界面不會(huì)發(fā)生分層或開裂等現(xiàn)象[6] 。為了達(dá)到通孔內(nèi)部無空洞的填充效果,在減緩金屬在硅片表面沉積速度的同時(shí)需要提高金屬在硅通孔內(nèi)的沉積速度,可以通過在電鍍液中加入抑制劑和加速劑等添加劑的方法實(shí)現(xiàn)。這兩種添加劑的存在可以在電鍍過程中減小電鍍液的表面張力,同時(shí)增強(qiáng)其分散能力。當(dāng)下常用的加速劑通常是小分子含硫有機(jī)物,可加速銅離子的沉積;常用的抑制劑一般是大分子物質(zhì),如聚乙二醇,這種抑制劑可以吸附在通孔頂部和底部的表面,從而抑制頂部和底部的沉積速率[25] 。

熔融法填充硅通孔是一種可以實(shí)現(xiàn) TSV 通孔導(dǎo)電材料快速、無空洞填充的技術(shù),在真空壓力下將熔融狀態(tài)的金屬填充進(jìn)通孔中,可以實(shí)現(xiàn)快速、無空洞的充填,且生產(chǎn)效率高,但是在多次高低溫循環(huán)的過程中,由于不同材料的熱膨脹系數(shù)也不同,金屬材料填充物與硅之間的界面會(huì)產(chǎn)生裂縫[26] 。采用一種新的 Bi-Sn-Ag 合金材料作為硅通孔的導(dǎo)電填充材料,這種新型材料可用于超小尺寸通孔的填充,且具有高耐熱性(>260 ℃)和低溫填充能力(<300 ℃),填充效率高[27] 。

4 結(jié)束語

在未來先進(jìn)封裝技術(shù)中,硅通孔技術(shù)是支撐多芯片垂直方向上物理和電氣連接的關(guān)鍵技術(shù)。該技術(shù)順應(yīng)了集成電路高密度、快速響應(yīng)速度、低成本和低功耗的發(fā)展趨勢(shì),滿足未來電子設(shè)備更小尺寸封裝結(jié)構(gòu)和多功能集成的需求。因此,提高硅通孔技術(shù)的可靠性可以推動(dòng)集成電路行業(yè)的高速可靠發(fā)展。

本文主要從兩方面介紹 TSV 可靠性,熱應(yīng)力可靠性和工藝可靠性。從熱應(yīng)力角度,可以采用TTSV增強(qiáng)散熱,利用 STI 技術(shù)有效降低 KOZ,同時(shí)掌握通孔結(jié)構(gòu)和不同深寬比對(duì) TSV 設(shè)計(jì)有重要意義。在工藝可靠性方面,采用循環(huán)氧化法可明顯削弱扇貝紋起伏,提高 TSV 內(nèi)壁的平滑程度;在電鍍液中加入抑制劑和加速劑兩種添加劑,可較大程度地改善導(dǎo)電材料在通孔內(nèi)的填充效果;熔融法填充技術(shù)可以實(shí)現(xiàn)高效率、無空洞的導(dǎo)電材料填充。如今,雖然高可靠性的硅通孔技術(shù)的工藝成本仍較高,但隨著工藝技術(shù)的不斷提高與成熟,TSV 技術(shù)會(huì)被大量應(yīng)用于三維封裝,推動(dòng)集成電路朝著更小尺寸、更多功能、更低成本、更高效率、更高可靠度的方向發(fā)展。

原文標(biāo)題:硅通孔技術(shù)可靠性技術(shù)概述

文章出處:【微信公眾號(hào):半導(dǎo)體封裝工程師之家】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

-

集成電路

+關(guān)注

關(guān)注

5387文章

11530瀏覽量

361639 -

硅通孔

+關(guān)注

關(guān)注

2文章

24瀏覽量

11838 -

硅通孔技術(shù)

+關(guān)注

關(guān)注

0文章

3瀏覽量

3434

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

搶先領(lǐng)取!高壓CoolGaN? GIT HEMT可靠性白皮書推薦

先進(jìn)封裝中的TSV/硅通孔技術(shù)介紹

不同制造商TOPCon光伏組件的老化測(cè)試:性能、穩(wěn)定性與可靠性

PCB高可靠性化要求與發(fā)展——PCB高可靠性的影響因素(上)

基于TI電感傳感技術(shù)的高可靠性低成本金屬按鍵設(shè)計(jì)

基于可靠性設(shè)計(jì)感知的EDA解決方案

汽車功能安全與可靠性的關(guān)系

請(qǐng)問FATFS文件系統(tǒng)可靠性如何?

半導(dǎo)體封裝技術(shù)的可靠性挑戰(zhàn)與解決方案

2024年新電子電路可靠性與電磁兼容技術(shù)研討會(huì)圓滿落幕

如何確保IGBT的產(chǎn)品可靠性

IGBT的可靠性測(cè)試方案

一文詳解硅通孔技術(shù)(TSV)

硅通孔技術(shù)可靠性技術(shù)概述

硅通孔技術(shù)可靠性技術(shù)概述

評(píng)論