Efinity版本:2023.1及以前版本。

易靈思器通過jtag bridge燒寫flash時需要自己生成一個jtage birdge文件。jtage bridge 工程的目的是為了打通JTAG與flash的連接。

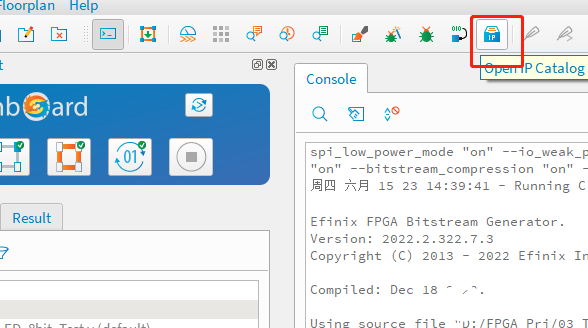

(1)打開IPM

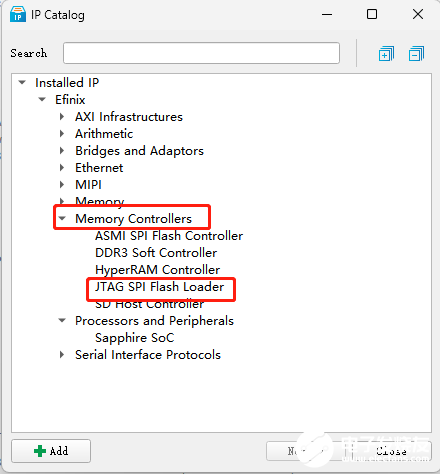

(2)選擇Memory Controllers -->Jtag spi flash loader

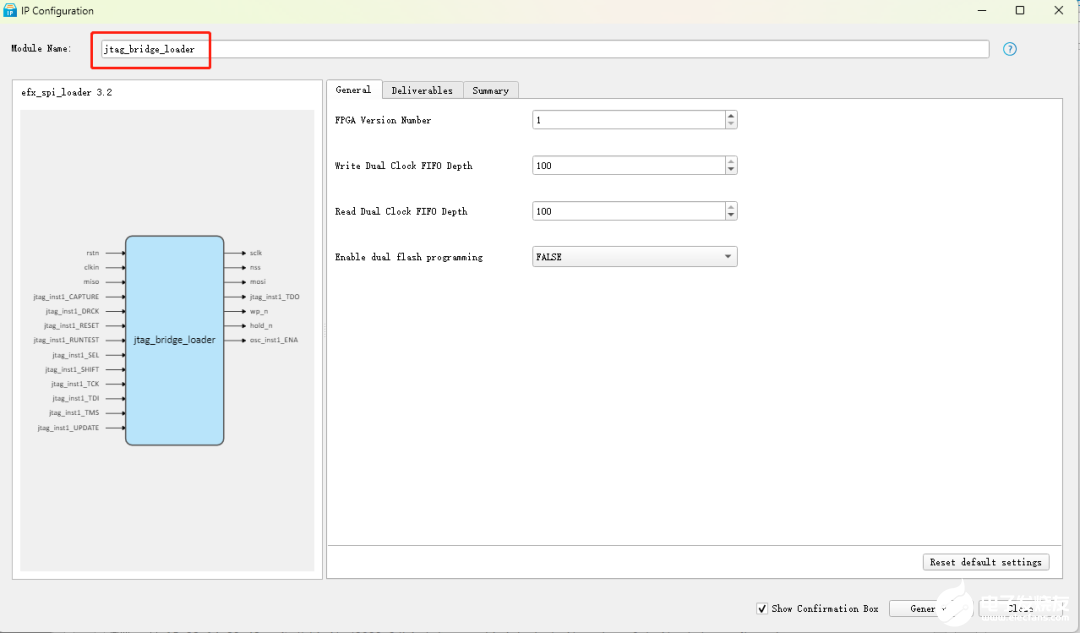

(3)隨便命個名。可以考慮把fifo深度加大。

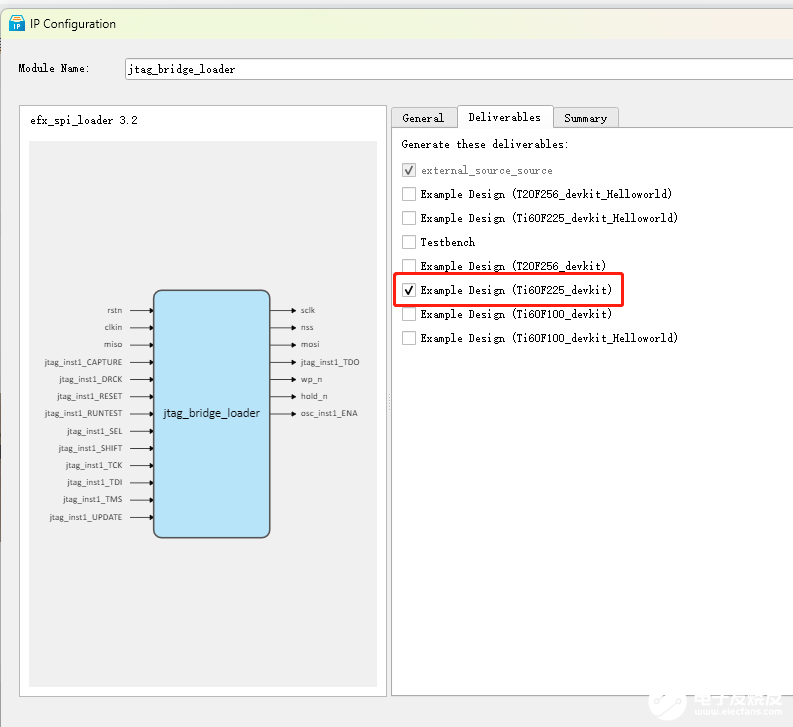

(4)在Deliverables界面根據自己的需要選擇相應的demo,如果沒有找到自己想用的器件就選擇相近的生成之后自己修改器件 。

(5)生成IP之后,會在IP目錄文件夾下生成一個example design,打開該工程。

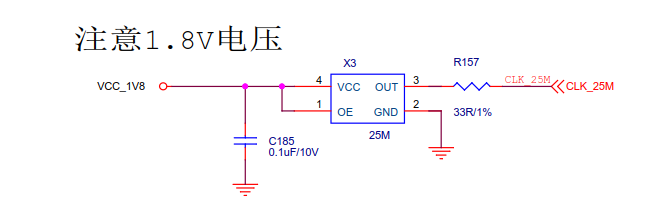

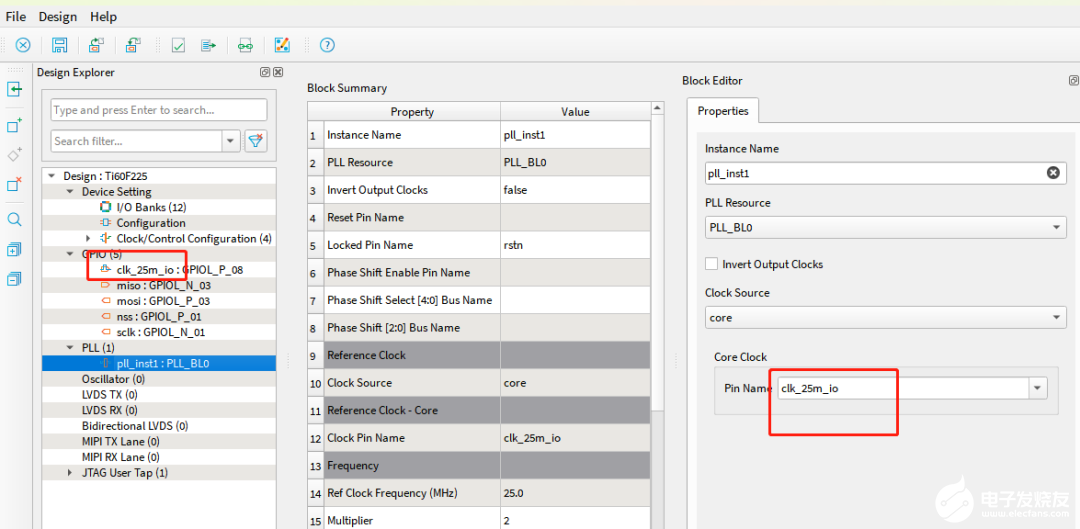

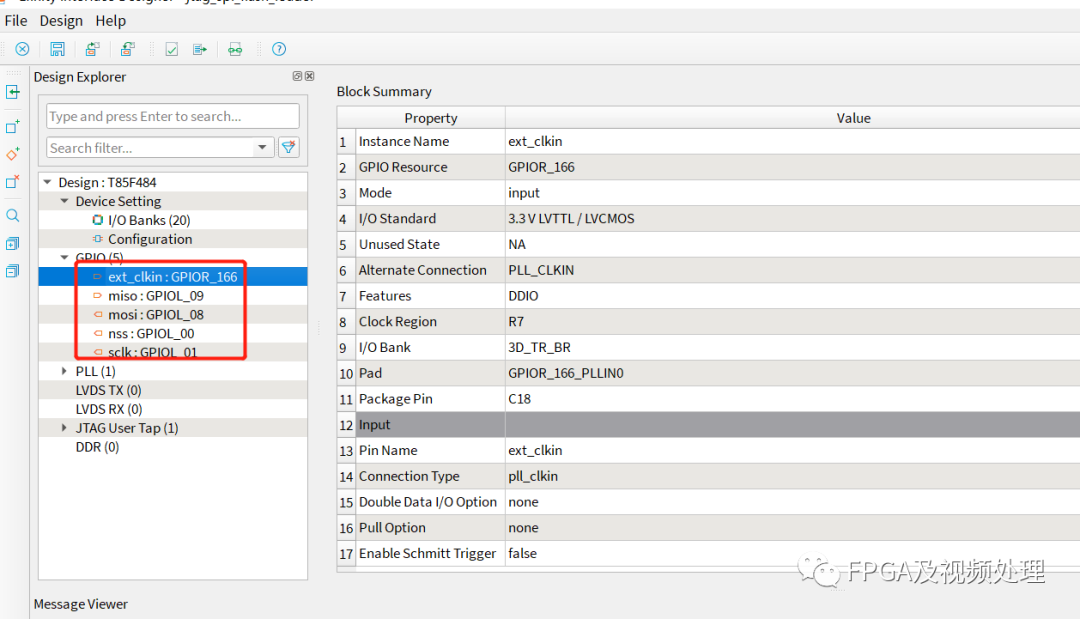

這里需要說明的是,如果是Trion系列FPGA因為沒有片內晶振,所以需要外部提供,這時要打開interface Designer然后自己指定電路板上提供的時鐘。比如在demo板上有一個外掛25M晶振,參考用法如下圖。

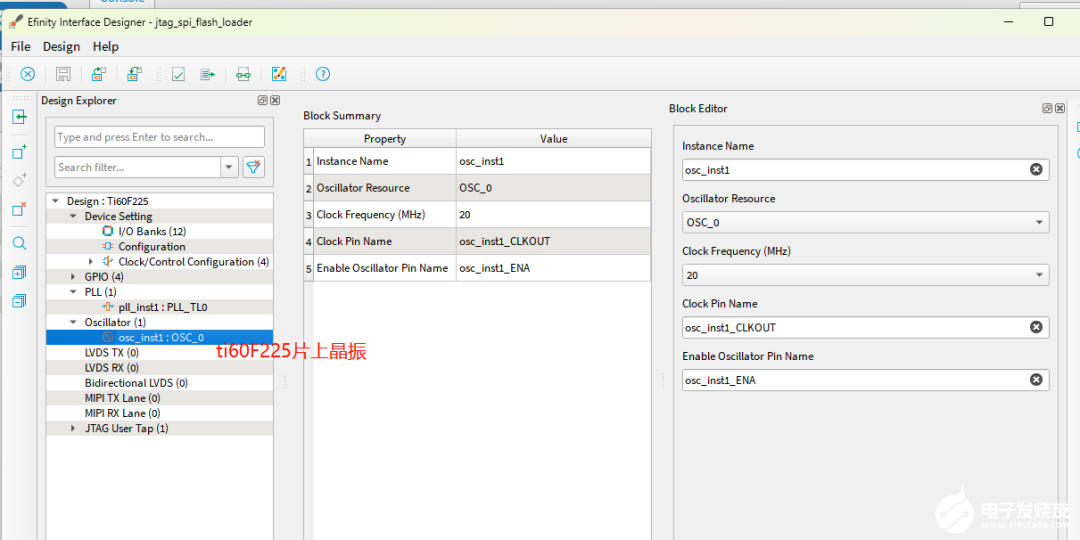

如果是鈦金系列,可以使用片上晶振可以用作PLL的參考時鐘,生成demo時也是默認使用片上晶振。所以只在編譯即可使用。

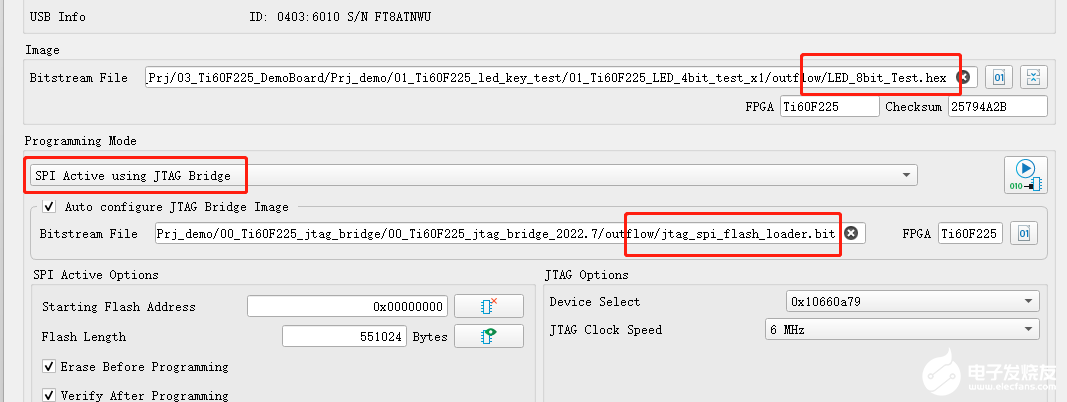

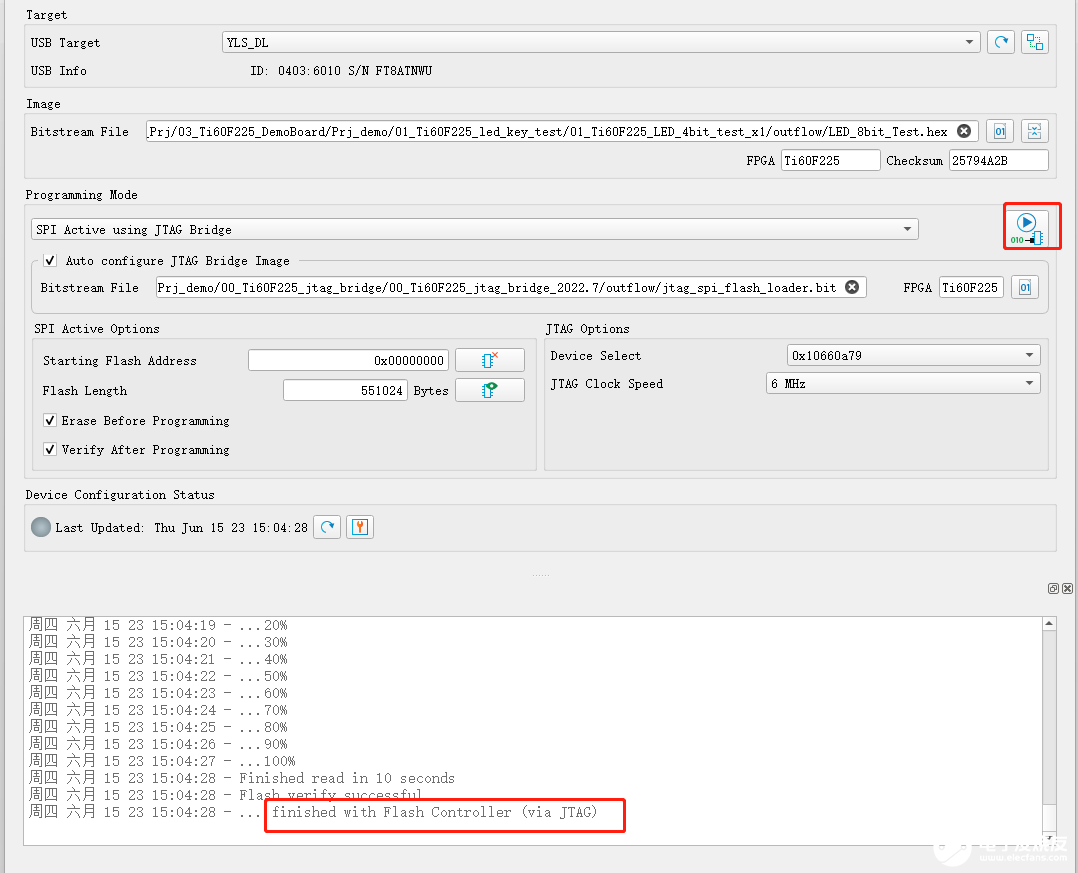

(6)配置程序時,選擇SPI Active using JTAG Bridge。在Auto configure jtag bridge Image欄選擇生成的bit文件。上面的Image欄選擇自己的工程hex數據流。

(7)燒寫。點擊start,燒寫完成后會提示finished with Flash Controller(via JTAG)表示燒寫成功。

Efinity版本:2023.2

可能有人在想為什么別的廠家的燒寫的時候不需要生成bridge文件呢,那是因為他們已經提前做好了。在2023.2版本及以后易靈思也對鈦金器件進行了相應的支持。

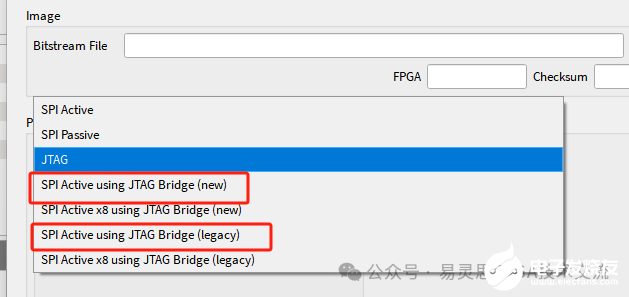

打開programmer,并選擇Programming Mode可以看到,2023.2已經支持Jtage Bridge(new)和(legacy)兩種方式,其中legacy方式就是指2023.1及以前的版本的使用的方式,需要自己生成bridge工程。而new這種方式是易靈思內部提供了相應的bridge文件,以我的電腦為例,在C:Efinity2023.2pgmflititanium路徑下。而且客戶只要選擇new這種方式軟件也會默認自動選擇對應器件的bridge文件。而且這種方式的birdge文件燒寫程序的速度要比lgeacy方式的快很多。

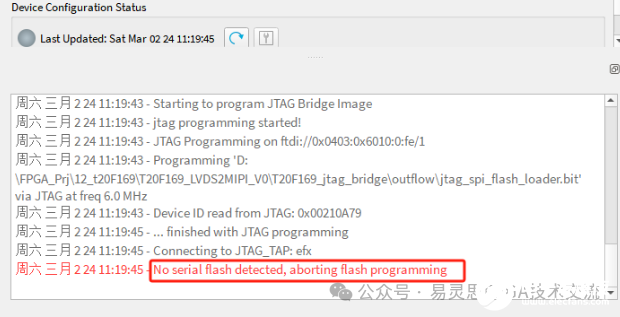

另外有一點要強調一下,是否可以用2023.2自帶的birdge文件用于老版本的燒寫從而把速度提上來呢?結論是不行的。如果這樣操作就會報No serial flash detected,aborting flash programming的錯誤。

對于trion器件,因為沒有內部晶振的原因,所以必須要指定外部時鐘管腳,所以暫時還沒有提供相應的工程。

打完收功,操作比較簡單,不啰嗦。如有問題歡交流。

-

FPGA

+關注

關注

1629文章

21729瀏覽量

603044 -

FlaSh

+關注

關注

10文章

1633瀏覽量

147953 -

JTAG

+關注

關注

6文章

400瀏覽量

71673 -

易靈思

+關注

關注

5文章

46瀏覽量

4862

發布評論請先 登錄

相關推薦

易靈思(Elitestek)FPGA編程器功能特點及驅動安裝方法

微雪電子ST-LINK/V2 STM32仿真器簡介

微雪電子ST-LINK/V2 STM32仿真器簡介

Kinect v2(Microsoft Kinect for Windows v2 )配置移動電源解決方案

FPGA應用--易靈思Programming Mode的幾種配置模式

易靈思RAM使用--Update3

易靈思FPGA產品的主要特點

易靈思Jtag_bridge_loader生成-v2

易靈思Jtag_bridge_loader生成-v2

評論