概述

目前人們對(duì)于高清視頻的需求日益普遍,極致的視覺(jué)體驗(yàn)帶來(lái)的是技術(shù)上的革新,高清視頻數(shù)據(jù)帶寬在HD視頻的基礎(chǔ)上不斷增長(zhǎng),以單路4Kx2K分辨率,30Hz刷新率超高清視頻而言為例,單幀無(wú)壓縮視頻數(shù)據(jù)量約為3840x2160x24≈189.84Mbits,每秒需完成緩存的數(shù)據(jù)量約為189.84x30≈5.56Gbits,如何傳輸及實(shí)時(shí)處理大量的高清視頻數(shù)據(jù)成為當(dāng)前的一大技術(shù)需求。

對(duì)此,本作品設(shè)計(jì)了一種基于FPGA的分布式視頻處理平臺(tái),能夠?qū)⒏咔逡曨l流通過(guò)PCIE接口以及SFP光傳輸接口進(jìn)行從上位機(jī)到分布式視頻處理平臺(tái)以及分布式視頻處理平臺(tái)之間的高速傳輸。同時(shí),本作品采用FPGA并行處理視頻流,具有低時(shí)延,高算法拓展能力的特點(diǎn),可以實(shí)現(xiàn)高帶寬高清視頻流的實(shí)時(shí)處理。

本項(xiàng)目平臺(tái)設(shè)計(jì)了PCIE 2.0*8接口、2路SFP/SFP+高速光傳輸接口以及4路HDMI輸出接口,針對(duì)高清視頻數(shù)據(jù),兼具遠(yuǎn)距離高速傳輸、實(shí)時(shí)處理以及本地同步顯示的能力,最多能傳輸處理10路以上的1080p高清視頻流。同時(shí)本項(xiàng)目平臺(tái)具有高達(dá)4GB容量的高速圖像緩存,以支持多路高清視頻流的緩存與算法處理。在FPGA基礎(chǔ)上,本項(xiàng)目平臺(tái)具有的雙核ARM Cortex-A9以及1GB容量的程序執(zhí)行緩存,可以支持更高層算法的實(shí)現(xiàn)。

主要?jiǎng)?chuàng)新點(diǎn)

1.提出了一個(gè)針對(duì)高分辨率的視頻流的高速傳輸與實(shí)時(shí)處理方案,包含了驅(qū)動(dòng)卡與接收卡兩個(gè)部分。

本作品平臺(tái)為基于FPGA的分布式視頻處理平臺(tái),面向高分辨率的視頻流實(shí)現(xiàn)高帶寬視頻數(shù)據(jù)的高速傳輸與實(shí)時(shí)處理,平臺(tái)系統(tǒng)完備,包含了視頻驅(qū)動(dòng)卡與接收卡兩個(gè)部分。

2.軟硬件全部自主設(shè)計(jì)開(kāi)發(fā),系統(tǒng)完善

本作品硬件軟件自主設(shè)計(jì)開(kāi)發(fā)。硬件部分包括43頁(yè)原理圖和12層高速PCB設(shè)計(jì)。軟件部分包括發(fā)送高清視頻流數(shù)據(jù)的上位機(jī)軟件模塊、本地視頻數(shù)據(jù)接收與轉(zhuǎn)發(fā)的視頻處理平臺(tái)模塊、分布式視頻數(shù)據(jù)接收顯示的視頻處理平臺(tái)模塊,包含PCIE數(shù)據(jù)接收模塊、SFP數(shù)據(jù)轉(zhuǎn)發(fā)模塊、視頻分割算法、DDR3高速緩存讀寫控制、視頻數(shù)據(jù)輸出模塊、視頻處理芯片配置模塊等,有很強(qiáng)的原創(chuàng)性和先進(jìn)性。

3.采用Xilinx Zynq-7000 SoC系列Zynq7045芯片,包含350K可編程邏輯資源以及Cortex-A9的雙核ARM,F(xiàn)PGA與ARM通信接口采用AXI總線協(xié)議,穩(wěn)定性好。

本設(shè)計(jì)采用的SoC芯片資源豐富,結(jié)合了FPGA與ARM的優(yōu)點(diǎn),從硬件設(shè)計(jì)層面提高了算法開(kāi)發(fā)容量和算法處理效率,保障了高清視頻數(shù)據(jù)處理的實(shí)時(shí)性,與現(xiàn)有技術(shù)相比,具有視頻處理速度快、延時(shí)低、擴(kuò)展性好等優(yōu)勢(shì)。

4.針對(duì)視頻處理與程序執(zhí)行部分分別設(shè)計(jì)了4GB與1GB的高速緩存,提升系統(tǒng)性能。

本系統(tǒng)FPGA部分采用多片DDR3高速存儲(chǔ)顆粒應(yīng)對(duì)大量的視頻數(shù)據(jù),能夠保證視頻傳輸處理的實(shí)時(shí)性和高效性。同時(shí)ARM部分也配備了多片DDR3高速存儲(chǔ)顆粒,保障程序執(zhí)行,為后續(xù)算法拓展提供支持。

5.通過(guò)PCIE*8接口從上位機(jī)獲取高清視頻數(shù)據(jù),最高數(shù)據(jù)速率理論可達(dá)32Gbps

本作品可通過(guò)一路PCI Express8-lane接口,從上位機(jī)讀取4k高清視頻流數(shù)據(jù),串行傳輸速率理論最高能達(dá)到32Gbps,最高支持2路4k@60Hz視頻數(shù)據(jù)的吞吐。

6.通過(guò)2路SFP/SFP+光傳輸接口進(jìn)行分布式視頻處理平臺(tái)間的高清視頻數(shù)據(jù)傳輸,最高數(shù)據(jù)速率理論可達(dá)10Gbps/路

本作品可通過(guò)兩路SFP/SFP+光傳輸接口,收發(fā)高清視頻流數(shù)據(jù),兩路光傳輸接口可通過(guò)主從模式同時(shí)工作,最高支持20Gbps的數(shù)據(jù)吞吐。

7.每一塊分布式視頻處理平臺(tái)系統(tǒng)同時(shí)具備4路2K視頻的HDMI輸出接口,能夠?qū)崿F(xiàn)視頻數(shù)據(jù)傳輸?shù)耐瑫r(shí)進(jìn)行本地分割顯示

本作品搭載4片視頻處理芯片ADV7511,可支持1920*1080@60Hz的高清視頻輸出,因此每一塊視頻處理平臺(tái)都擁有一路4k視頻數(shù)據(jù)的分割輸出功能,支持高速轉(zhuǎn)發(fā)的同時(shí),本地顯示視頻數(shù)據(jù)。

系統(tǒng)架構(gòu)

1.系統(tǒng)方案

隨著視頻技術(shù)的不斷革新,為了解決超高分辨率,例如2K、4K、8K、16K甚至更高分辨率的視頻傳輸處理需求,需要硬件上能支持高清視頻輸入輸出,高速大容量數(shù)據(jù)實(shí)時(shí)處理,軟件層面上具備多種算法處理能力,各種數(shù)據(jù)通信交互,且系統(tǒng)要能支持性能拓展,以便使系統(tǒng)兼容處理更大范圍的任務(wù)強(qiáng)度。

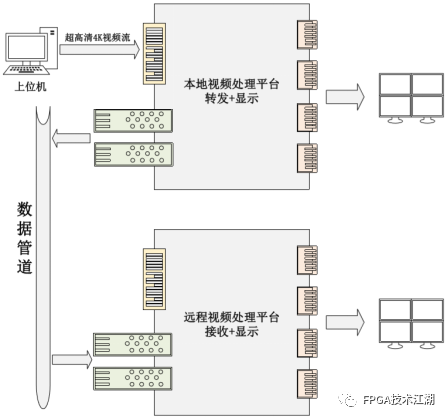

分布式視頻處理平臺(tái)系統(tǒng)主要分為三部分:發(fā)送高清視頻流數(shù)據(jù)的上位機(jī)、2塊及以上的基于FPGA的分布式視頻處理平臺(tái)、作為一組完整4K視頻顯示的4塊2K顯示屏。該系統(tǒng)基本結(jié)構(gòu)如圖2-1所示。本作品為基于FPGA的分布式視頻處理平臺(tái)。主要實(shí)現(xiàn)視頻信號(hào)發(fā)生輸出以及視頻信號(hào)接收這兩個(gè)工作模式。

圖2-1分布式視頻處理平臺(tái)系統(tǒng)

2.硬件方案

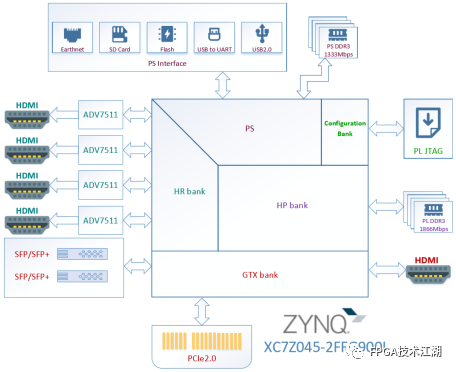

本基于FPGA的分布式視頻處理平臺(tái)需要將高清視頻流通過(guò)PCIE接口以及SFP光傳輸接口進(jìn)行從上位機(jī)到分布式視頻處理平臺(tái)以及分布式視頻處理平臺(tái)之間的高速傳輸。同時(shí)需要4路HDMI輸出接口,在高速傳輸高清視頻流的同時(shí),通過(guò)FPGA超低時(shí)延的并行處理能力,能同步進(jìn)行高清視頻的分布式拼接顯示。為支持以上要求,本作品搭載了Xilinx公司的Zynq-7000 SoC系列Zynq7045芯片作為核心處理器進(jìn)行視頻數(shù)據(jù)的傳輸及實(shí)時(shí)處理。

為完成對(duì)視頻處理過(guò)程的控制,本系統(tǒng)需要利用芯片自帶的雙核Cortex-A9作為系統(tǒng)控制部分,對(duì)視頻處理芯片進(jìn)行寄存器配置,同時(shí)掛載大容量SDRAM,實(shí)現(xiàn)對(duì)大量系統(tǒng)數(shù)據(jù)參數(shù)的存儲(chǔ)。

本作品需要滿足大量視頻數(shù)據(jù)的高速緩存要求。以最高單路4Kx2K分辨率,30Hz刷新率超高清視頻而言為例,單幀無(wú)壓縮視頻數(shù)據(jù)量約為3840x2160x24≈189.84Mbits,每秒需完成緩存的數(shù)據(jù)量約為189.84x30≈5.56Gbits。本系統(tǒng)可支持PCIE 32Gbps帶寬以內(nèi)的超高清視頻輸入,則需要外接大容量高速存儲(chǔ)設(shè)備,實(shí)現(xiàn)對(duì)多路視頻數(shù)據(jù)的緩存。

因此,本系統(tǒng)采用4片共32Gbits高速DDR3存儲(chǔ)顆粒,可滿足實(shí)時(shí)處理視頻流數(shù)據(jù)時(shí)對(duì)緩存空間的需求。本系統(tǒng)中FPGA核心處理器與存儲(chǔ)芯片接口數(shù)據(jù)位寬共64bits,單根數(shù)據(jù)線傳輸速率可達(dá)1866Mbps,可滿足對(duì)多路超高清視頻流數(shù)據(jù)的高速緩存需求。

根據(jù)以上的分析,制定出的本作品硬件設(shè)計(jì)方案如下:

視頻實(shí)時(shí)處理方案:XilinxZynq-7000 SoC系列Zynq7045芯片的FPGA部分作為視頻核心處理器

視頻接收方案:一路PCI Express 8-lane接口

視頻發(fā)送方案:兩路SFP/SFP+光傳輸接口

視頻輸出方案:四路ADV7511視頻處理器,4個(gè)HDMI1.4視頻輸出接口

視頻流緩存方案:32GBitsDDR3存儲(chǔ)顆粒高速緩存

視頻控制方案:Zynq7045芯片的ARM部分,雙核Cortex-A9,2片128MB QSPI Flash和8Gbits SDRAM

系統(tǒng)接口設(shè)計(jì)方案:USB2.0接口、UART、1000M以太網(wǎng)口

圖2-2平臺(tái)結(jié)構(gòu)框圖

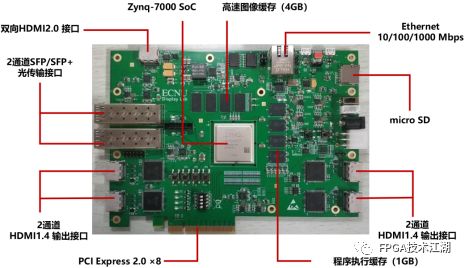

本作品實(shí)際結(jié)構(gòu)圖如圖2-3所示。

圖2-3平臺(tái)實(shí)際結(jié)構(gòu)圖

3.軟件方案

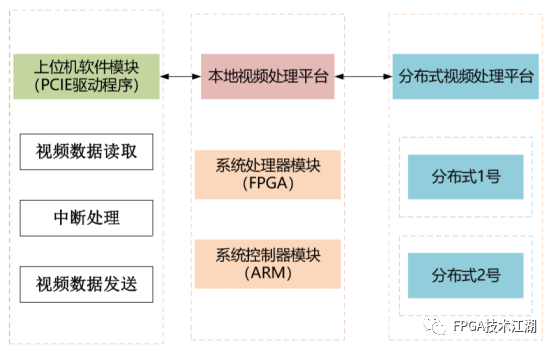

基于FPGA的分布式視頻處理平臺(tái)的軟件整體設(shè)計(jì)如圖2-4所示,其中主要包括三個(gè)模塊:發(fā)送高清視頻流數(shù)據(jù)的上位機(jī)軟件模塊、本地視頻數(shù)據(jù)接收與轉(zhuǎn)發(fā)的視頻處理平臺(tái)模塊、分布式視頻數(shù)據(jù)接收顯示的視頻處理平臺(tái)模塊。

圖2-4系統(tǒng)軟件整體框架圖

其中上位機(jī)PCIE驅(qū)動(dòng)部分,實(shí)現(xiàn)了指定路徑下的視頻流數(shù)據(jù)文件的讀取與發(fā)送,根據(jù)用戶給定的中斷參數(shù),實(shí)現(xiàn)上位機(jī)吞吐速率的控制以及數(shù)據(jù)發(fā)送操作的開(kāi)關(guān)選擇。

本地視頻數(shù)據(jù)接收與轉(zhuǎn)發(fā)的視頻處理平臺(tái)的軟件設(shè)計(jì)較為復(fù)雜,分為PCIE數(shù)據(jù)接收模塊、SFP數(shù)據(jù)轉(zhuǎn)發(fā)模塊、視頻重組分割算法、DDR3高速緩存讀寫控制、視頻數(shù)據(jù)輸出模塊、視頻處理芯片寄存器配置等部分。

分布式視頻數(shù)據(jù)接收顯示的視頻處理平臺(tái)模塊,分為SFP數(shù)據(jù)接收模塊,視頻重組算法、DDR3高速緩存讀寫控制、視頻輸出模塊、視頻處理芯片寄存器配置等部分。

設(shè)計(jì)演示

1.基于FPGA的分布式視頻處理平臺(tái)單板性能測(cè)試

以下給出電源、時(shí)鐘及復(fù)位信號(hào)和DDR3等幾方面測(cè)試過(guò)程及結(jié)果。

1.1電源測(cè)試

電源的穩(wěn)定運(yùn)行是電路系統(tǒng)正常工作的前提條件,因此,在對(duì)電路系統(tǒng)各部分進(jìn)行測(cè)試前,需要先對(duì)系統(tǒng)電源部分測(cè)試,確保電源電壓、紋波等參數(shù)能夠滿足要求。本系統(tǒng)的電源使用了TI公司的TPS53355、TPS62130和TPS51200。

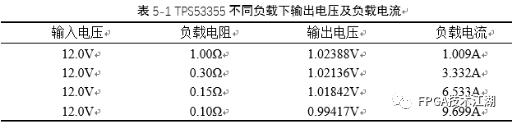

對(duì)TPS53355電源評(píng)估電路進(jìn)行測(cè)試,可得到如表5-1所示的測(cè)量結(jié)果。

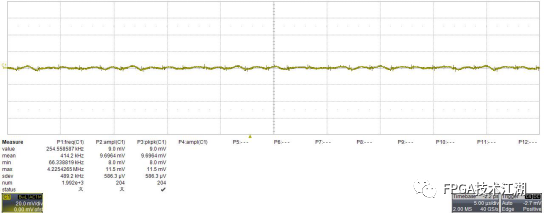

通過(guò)對(duì)電源輸出電壓進(jìn)行分析,可見(jiàn)在較低負(fù)載和較高負(fù)載下都能夠滿足FPGA核心處理器0.97V至1.03V的電壓范圍要求。通過(guò)示波器可以測(cè)得在不同負(fù)載情況下的紋波,其中負(fù)載電流為9.699A時(shí)的紋波測(cè)試結(jié)果如圖5-1所示。

圖5-1 TPS53355負(fù)載電流為9.699A時(shí)的紋波

此時(shí),可觀測(cè)到電源的開(kāi)關(guān)頻率約為500KHz,電源紋波幅度的最小值為8.0mV,最大值為11.5mV,滿足電路系統(tǒng)設(shè)計(jì)要求。

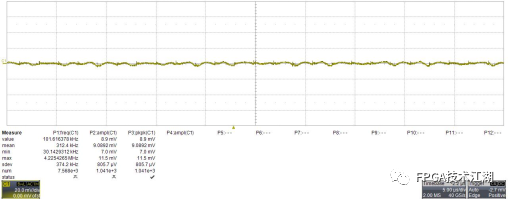

通過(guò)對(duì)實(shí)際電路中1.0V電源進(jìn)行測(cè)試,紋波如圖5-2所示,同樣滿足設(shè)計(jì)要求。

圖5-2 TPS53355在系統(tǒng)工作時(shí)的紋波波形

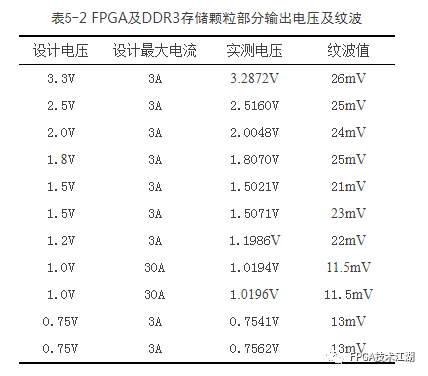

分別對(duì)本系統(tǒng)中其他部分電源電路進(jìn)行測(cè)量,其中FPGA核心處理器及DDR3存儲(chǔ)顆粒部分各電源輸出電壓及紋波如表5-2所示,都能夠滿足設(shè)計(jì)要求。

1.2時(shí)鐘及復(fù)位信號(hào)測(cè)試

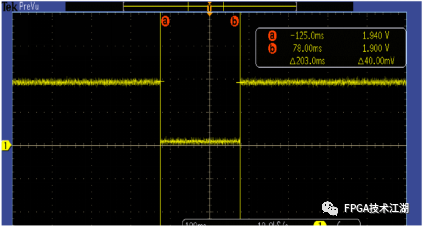

系統(tǒng)的復(fù)位信號(hào)是測(cè)試部分首先考慮的對(duì)象。在本系統(tǒng)中,我們對(duì)于ZYNQ中ARM部分的復(fù)位芯片MAX16025輸出的全局復(fù)位信號(hào)進(jìn)行測(cè)試。如圖5-3所示,當(dāng)按鍵被按下時(shí),全局復(fù)位信號(hào)被置為低電平,且低電平保持203.0ms;當(dāng)按鍵被松開(kāi)時(shí),全局復(fù)位信號(hào)恢復(fù)成高電平。

圖5-3系統(tǒng)全局復(fù)位信號(hào)測(cè)試 其次測(cè)試系統(tǒng)的時(shí)鐘信號(hào)。在整個(gè)系統(tǒng)中,以下三個(gè)時(shí)鐘較為關(guān)鍵。

ZYNQ處理器FPGA部分200MHz差分時(shí)鐘(邏輯觸發(fā)時(shí)鐘);

ZYNQ處理器GTX部分SFP光傳輸接口IP核的156.25MHz差分時(shí)鐘;

ZYNQ 處理器 ARM 部分 33.33333MHz 單端時(shí)鐘。

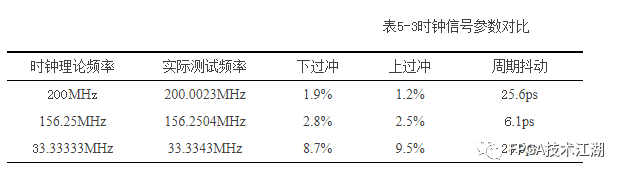

其中,差分時(shí)鐘需要利用差分探頭進(jìn)行測(cè)試。 在測(cè)試時(shí)鐘時(shí),示波器的采樣率被設(shè)置為1GHz,上述三個(gè)時(shí)鐘的時(shí)鐘波形如圖5-4所示。

圖5-4系統(tǒng)時(shí)鐘信號(hào)測(cè)試 三個(gè)關(guān)鍵時(shí)鐘信號(hào)測(cè)量所得參數(shù)如表5-3所示。

由上表可見(jiàn),相對(duì)于33.33333MHz的單端時(shí)鐘,200MHz和156.25MHz的差分時(shí)鐘利用了抑制相互串?dāng)_的性質(zhì),時(shí)間精度較高,并且在信號(hào)的上過(guò)沖、下過(guò)沖和周期抖動(dòng)指標(biāo)上具有優(yōu)勢(shì)。

1.3DDR3眼圖測(cè)試

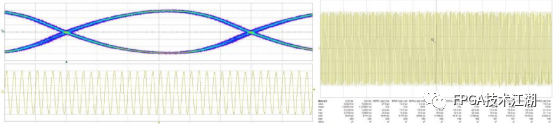

這部分介紹系統(tǒng)ZYNQ中的FPGA部分連接的DDR3的信號(hào)完整性測(cè)試過(guò)程與結(jié)果。DDR3速率為1600Mbps,通過(guò)編寫測(cè)試程序的方式來(lái)實(shí)現(xiàn)持續(xù)對(duì)DDR3進(jìn)行讀寫,以進(jìn)行測(cè)試。示波器測(cè)試800MHz差分時(shí)鐘眼圖,如圖5-5所示

圖5-5DDR3差分時(shí)鐘眼圖測(cè)試

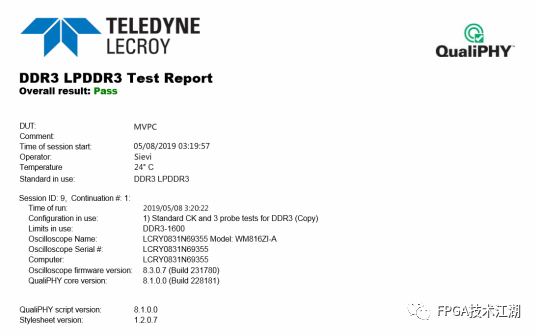

由圖5-5可知示波器讀出該信號(hào)眼高為1.1366V,眼寬為578ps,眼交叉比為50.37%,差分時(shí)鐘設(shè)計(jì)指標(biāo)通過(guò)了LeCroy示波器的QualiPHY對(duì)于1600Mbps的DDR3的標(biāo)準(zhǔn)測(cè)試,因此眼圖各指標(biāo)符合設(shè)計(jì)要求。

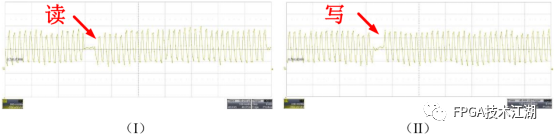

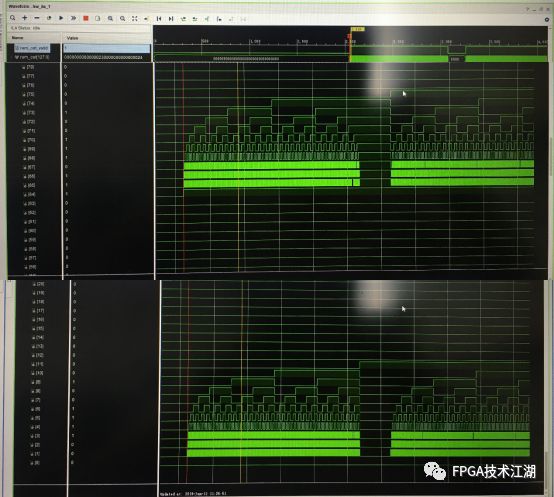

進(jìn)一步利用示波器觀察DDR3時(shí)序:DQS信號(hào)如圖5-6所示:當(dāng)DDR3進(jìn)入讀狀態(tài)時(shí),DQS前導(dǎo)碼先產(chǎn)生負(fù)脈沖。相反,當(dāng)DDR3進(jìn)入寫狀態(tài)時(shí),DQS前導(dǎo)碼先產(chǎn)生正脈沖。

圖5-6DDR3 DQS信號(hào)測(cè)試

示波器自帶的QualiPHY功能能夠?qū)DR3各項(xiàng)性能進(jìn)行測(cè)試,測(cè)試完成后將會(huì)生成一份測(cè)試報(bào)告,如圖5-7所示。在測(cè)試報(bào)告中將詳細(xì)列出各項(xiàng)參數(shù)的測(cè)量值和理論值,并對(duì)是否達(dá)標(biāo)進(jìn)行分析。

圖5-7差分時(shí)鐘線測(cè)試報(bào)告

1.4ADV7511視頻處理器驗(yàn)證

為驗(yàn)證ADV7511視頻處理器芯片部分的電路設(shè)計(jì),編寫測(cè)試代碼以完成驗(yàn)證。在進(jìn)行該部分的測(cè)試過(guò)程中,我們基于ZYNQARM部分編寫IIC配置接口,配置ADV7511寄存器,使能芯片,同時(shí),F(xiàn)PGA部分按照時(shí)序要求編寫測(cè)試圖像,并輸出到ADV7511,最終板級(jí)輸出效果如圖5-8所示。

圖5-8ADV7511測(cè)試圖像圖

由上圖可知,ADV7511寄存器配置正確,芯片正常使能,F(xiàn)PGA時(shí)序發(fā)生正確,能夠正常顯示圖像。

1.5 PCIE系統(tǒng)接口驗(yàn)證

圖5-9上位機(jī)數(shù)據(jù)發(fā)送窗口為驗(yàn)證PCIE系統(tǒng)接口的功能,我們通過(guò)上位機(jī)向系統(tǒng)的PCIE接口發(fā)送數(shù)據(jù)文件,如圖5-9所示。

通過(guò)Vivado的ILA工具采得數(shù)據(jù)傳輸波形,如圖5-10所示。從圖5-10的波形中,對(duì)比上位機(jī)發(fā)送的文件數(shù)據(jù),可知PCIE讀取的數(shù)據(jù)文件正確無(wú)誤。

圖5-10系統(tǒng)PCIE接口數(shù)據(jù)文件抓取波形圖

2.系統(tǒng)聯(lián)調(diào)

整體系統(tǒng)聯(lián)調(diào)效果圖如圖5-11所示:

圖5-11系統(tǒng)整體效果圖

通過(guò)以上的效果可以看出,本作品可以實(shí)現(xiàn)本地視頻處理平臺(tái)PCIE接口從上位機(jī)接收超高清4K視頻流的數(shù)據(jù),并經(jīng)過(guò)SFP/SFP+高速光傳輸接口高速傳送至分布式視頻處理平臺(tái),同時(shí)本地與分布式視頻處理平臺(tái)兼有4K視頻分割顯示的實(shí)時(shí)處理能力。

審核編輯:劉清

-

FPGA

+關(guān)注

關(guān)注

1629文章

21729瀏覽量

602986 -

DDR3

+關(guān)注

關(guān)注

2文章

276瀏覽量

42242 -

PCB設(shè)計(jì)

+關(guān)注

關(guān)注

394文章

4683瀏覽量

85545 -

CORTEX-A9

+關(guān)注

關(guān)注

0文章

38瀏覽量

35231 -

PCIe接口

+關(guān)注

關(guān)注

0文章

120瀏覽量

9702

原文標(biāo)題:基于FPGA的分布式視頻處理平臺(tái)

文章出處:【微信號(hào):HXSLH1010101010,微信公眾號(hào):FPGA技術(shù)江湖】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

分布式軟件系統(tǒng)

《無(wú)線通信FPGA設(shè)計(jì)》分布式FIR的并行改寫

如何利用FPGA設(shè)計(jì)無(wú)線分布式采集系統(tǒng)?

分布式系統(tǒng)的優(yōu)勢(shì)是什么?

分布式KVM坐席拼控系統(tǒng)解決方案

求一種基于FPGA分布式算法的濾波器設(shè)計(jì)的實(shí)現(xiàn)方案

如何高效完成HarmonyOS分布式應(yīng)用測(cè)試?

基于混沌置亂預(yù)處理的分布式視頻編碼

應(yīng)用分布式算法在FPGA平臺(tái)實(shí)現(xiàn)FIR低通濾波器

FIR數(shù)字濾波器分布式算法的原理及FPGA實(shí)現(xiàn)

WMSN的分布式視頻編碼技術(shù)研究

基于FPGA的分布式視頻處理平臺(tái)設(shè)計(jì)方案

基于FPGA的分布式視頻處理平臺(tái)設(shè)計(jì)方案

評(píng)論