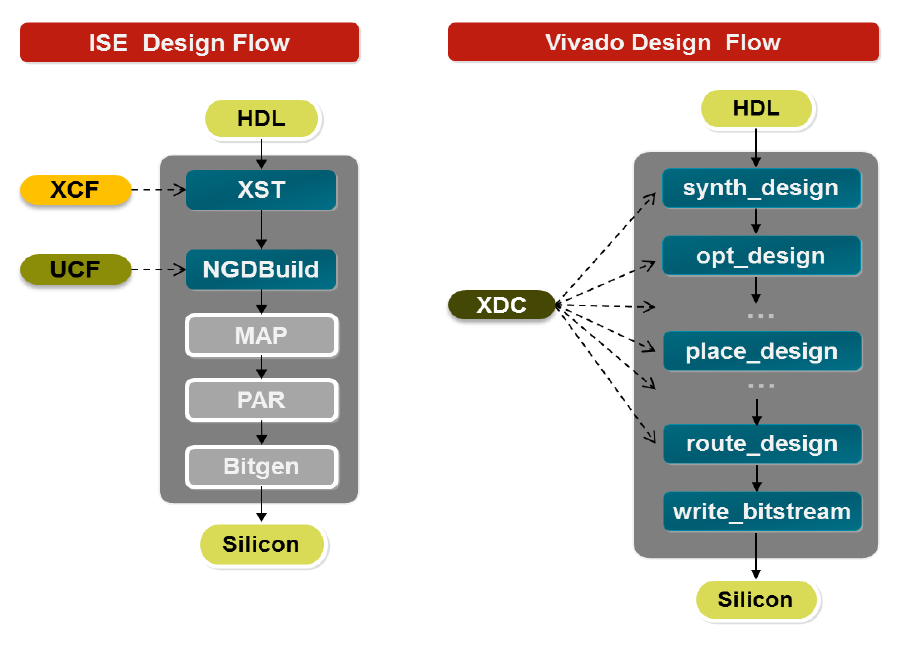

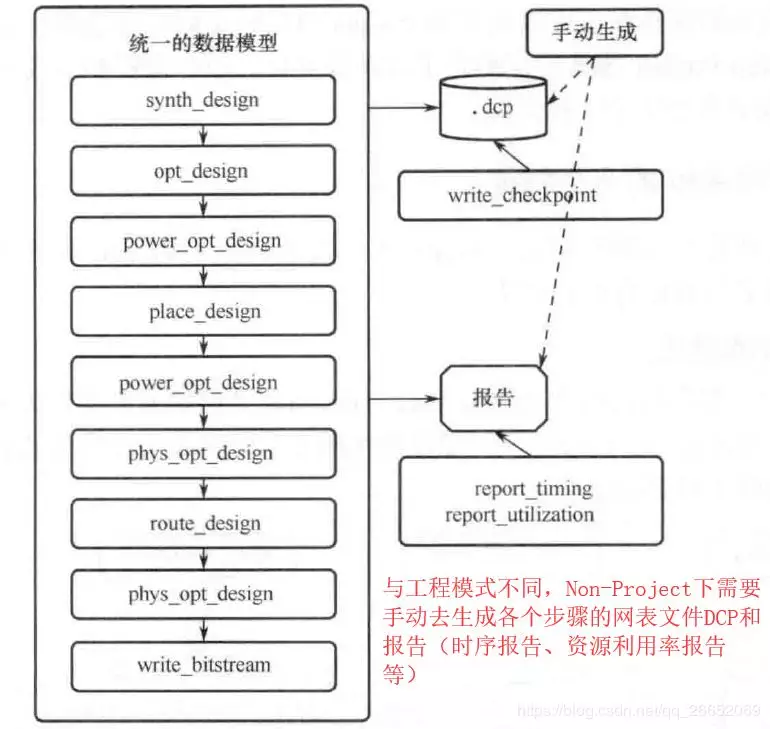

本文介紹了在 AMD VivadoDesign Tool中用工程模式使用 DFX 流程以及需要注意的地方。在使用 DFX 工程模式的過程中要把具體步驟映射到相應的 DFX 非工程模式的步驟,這樣才能更好地理解整個流程的運行邏輯。

1. 創(chuàng)建初始普通工程

DFX 工程模式會將 DFX 的要求自動嵌入到 Vivdao 流程中,后續(xù)用戶可以在 Vivado IDE 中訪問該工程。

所有靜態(tài)邏輯和各個 RM(Reconfigurable Module)的源文件,各個 Configuration 的輸出文件都會都被自動管理,而在 DFX 非工程模式中這個文件都需要用戶自行管理。

DFX 模式中創(chuàng)建工程的流程和普通設計沒有區(qū)別,用戶需要把靜態(tài)部分的源文件和約束文件加入到新建的工程中。

Intitial Configuration 的 RM 所包含的源文件和約束文件可以在此時加入工程,也可以在后續(xù)步驟中加入到當前的工程中。如果此時不加入 Intitial Configuration 的 RM 的相關文件,可以暫時將此 RM 作為黑盒處理。在這里我們一般選擇同時把 Intitial Configuration 的 RM 所包含的源文件和約束文件到加入工程中。

2. 將初始普通工程設置成 DFX 工程

建成初始普通工程后,建議把工程通過以下任一的方法做好備份。

1. File -> Project -> Archive

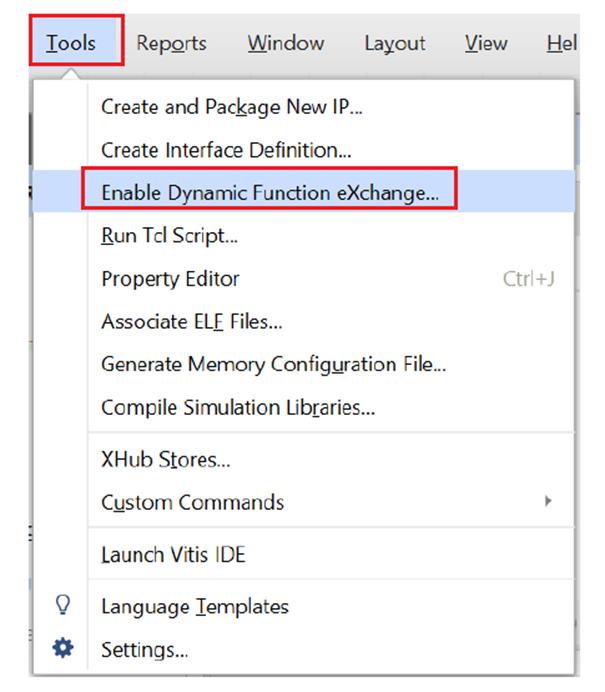

2. 在 TCL CONSOLE 執(zhí)行 "write_project_tcl XX.tcl" 獲得重建工程所需的 TCL 腳本。通過主菜單 Tools -> Enable Dynamic Function eXchange 將初始普通工程設置成 DFX 工程。

注意:這個操作一旦執(zhí)行不可逆轉, 不可撤銷。

3. 創(chuàng)建分區(qū)定義(Create Partition Definition)

這步操作對應非工程模式中創(chuàng)建 RP(Reconfigurable Partitions)的步驟, 對應的模塊的 HD.REGUFIGURABLE 屬性被自動被設置成 True。

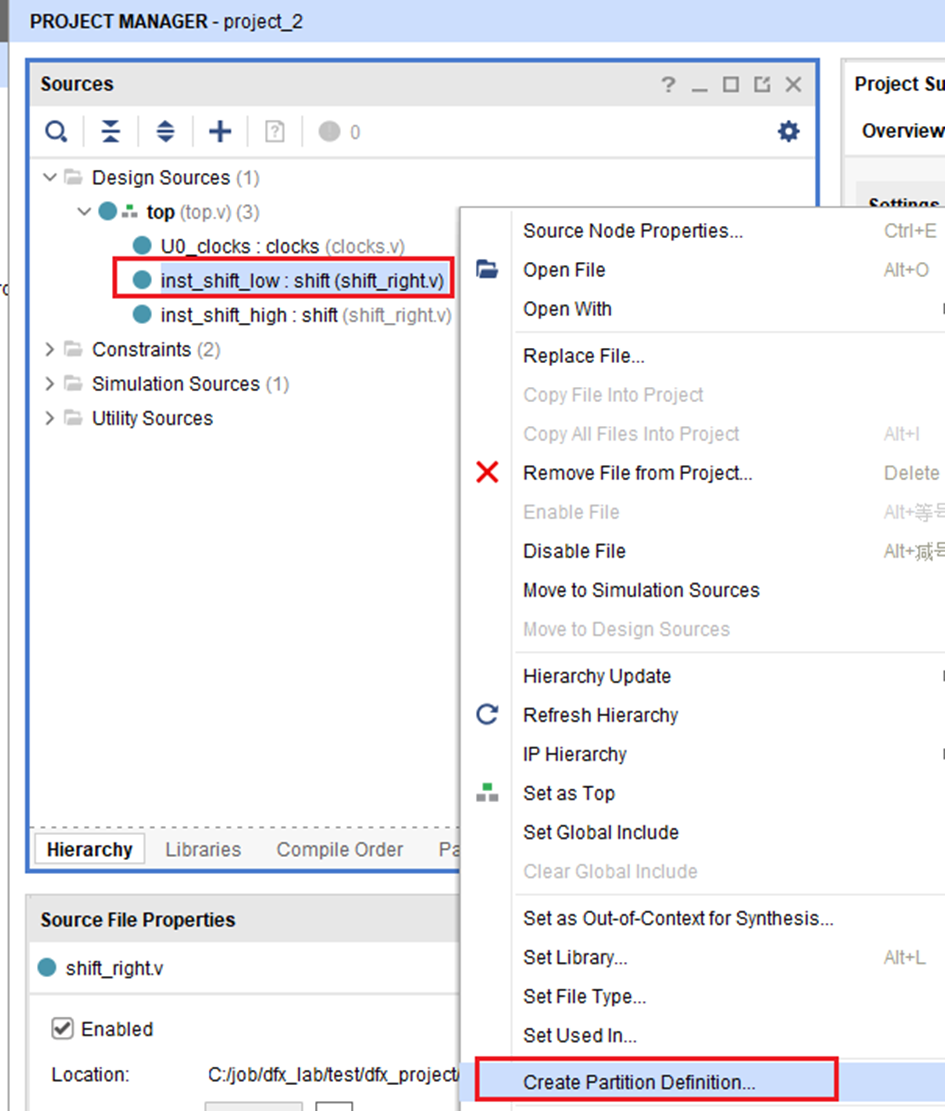

當把普通工程轉成 DFX 工程之后,可以從 RTL Source/Hierarchy 窗口中選擇一個文件(對應的 Instance)作為 RP。

注意:動態(tài)頂層文件不能是 IP,DCP 或者 EDIF。如果暫時沒有動態(tài)部分的邏輯,這里允許選擇黑盒文件。(在后續(xù)的 opt_design 步驟之前,需要用網(wǎng)表或者灰盒填充這個黑盒)。

在這里的例子中,同一個 Module 被例化了兩次,不管是哪一個 Instance 被定義成 Partition, 這兩個 Instance 都會變成 RP。如果實際只需要一個 Module 作 RP,那么需要手動修改其中一個 Module 的名字,使他們相互不同。

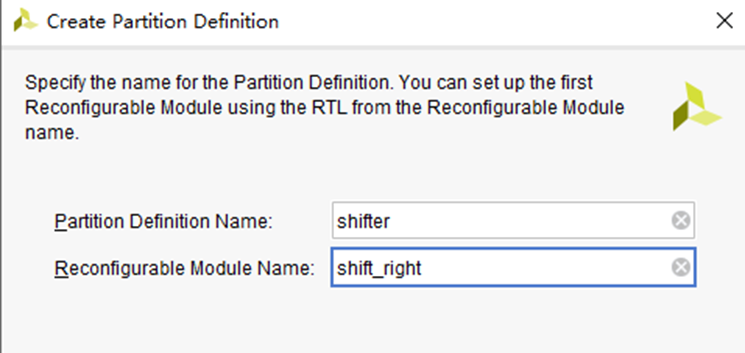

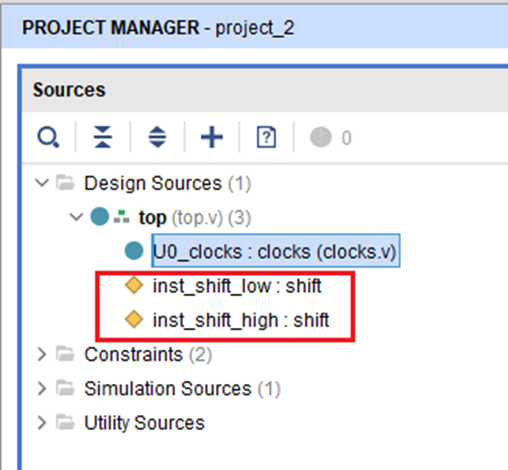

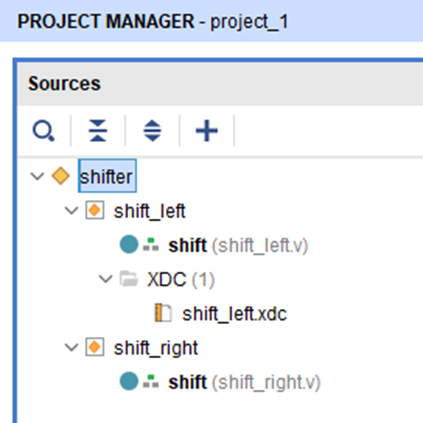

在彈窗"Create Partition Name"中分別給 Partition Definition 和 Reconfiguratble Module 命名后,Source 窗口會相應改變: 黃色菱形代表的模塊即是 Partition Definition。

在非工程模式中靜態(tài)部分和動態(tài)部分是分開綜合再 Link 到一起。在非工程模式中,工具會自動對 RP 模塊進行 OOC 綜合后合并到頂層,和在非工程模式的原理一致。在這里要注意動態(tài)區(qū)邏輯和靜態(tài)區(qū)邏輯的綜合依然是保持相互獨立。

4. 按照 DFX Wizard 的引導完成 DFX 工程的設置

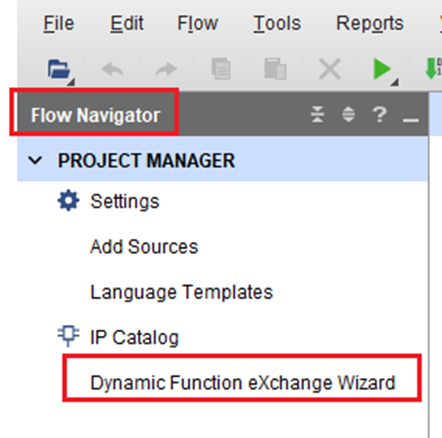

1. 在工具菜單或者 Flow Navigator 中啟動 DFX Wizard。

2. 點擊 Next 進入 Edit Reconfigurable Modules 頁面。

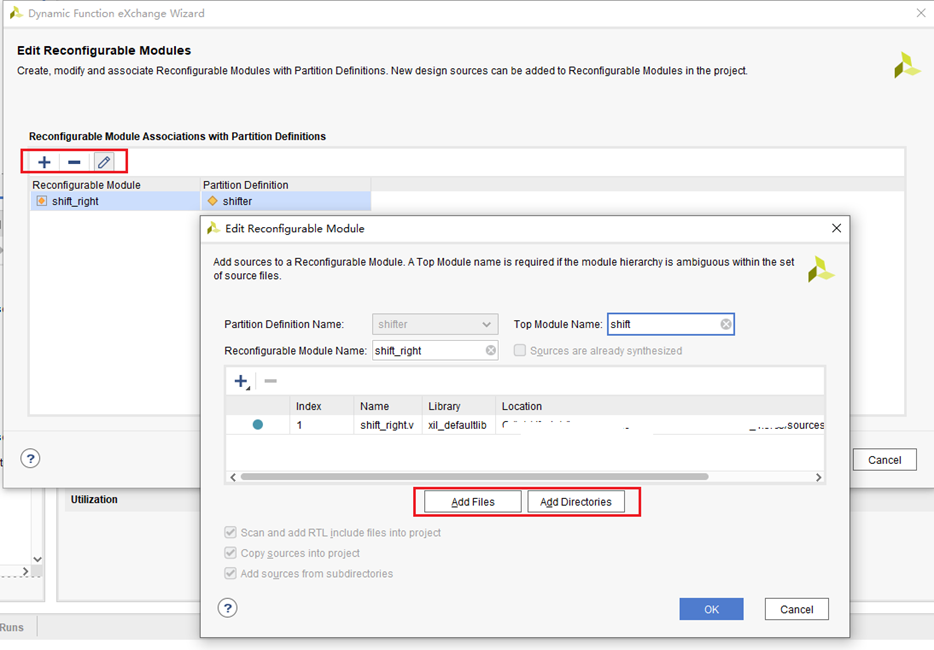

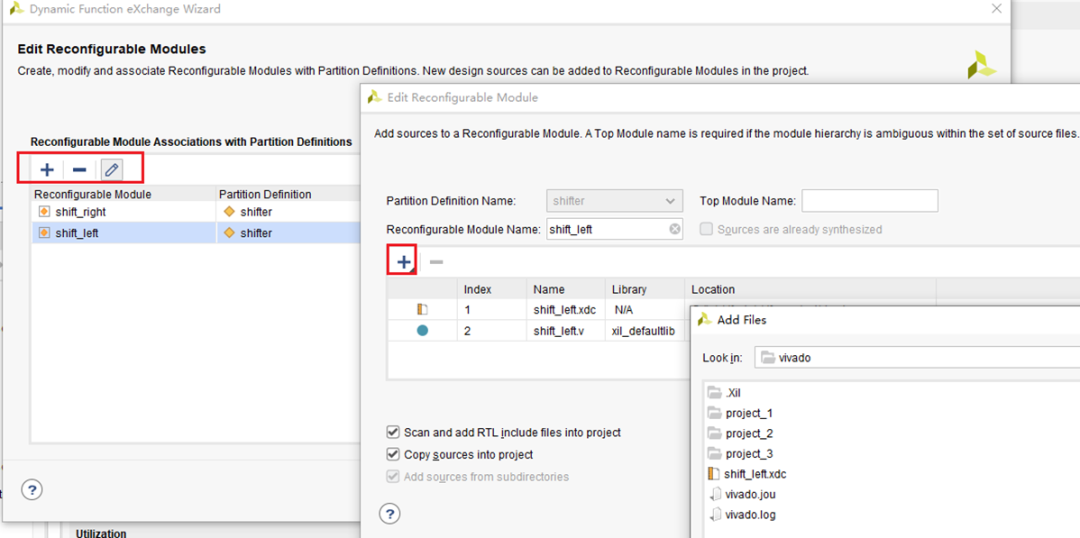

這里可以看到之前加的 RM shift_right 已經(jīng)存在了。藍色的+、-和鉛筆按鈕分別對應增加、刪除和修改 RM 源文件的操作。

3. 點擊+號可以創(chuàng)建一個新的 RM,點擊“Add Files"或者"Add Directories”。

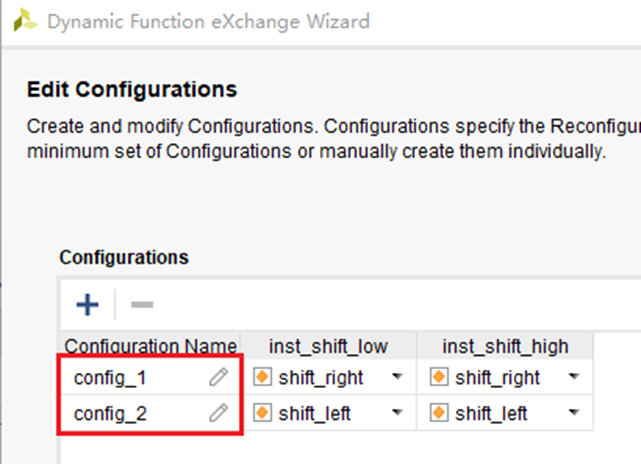

4. 點擊 Next,進入"Edit Configurations"頁面。

點擊+號添加Configuration,也可以直接點擊"automatically create configurations"讓工具自動生成 Configuration。這里我們直接讓工具自動產(chǎn)生 Configuration,然后我們可以按照我們自己的需求在這基礎上進行修改。

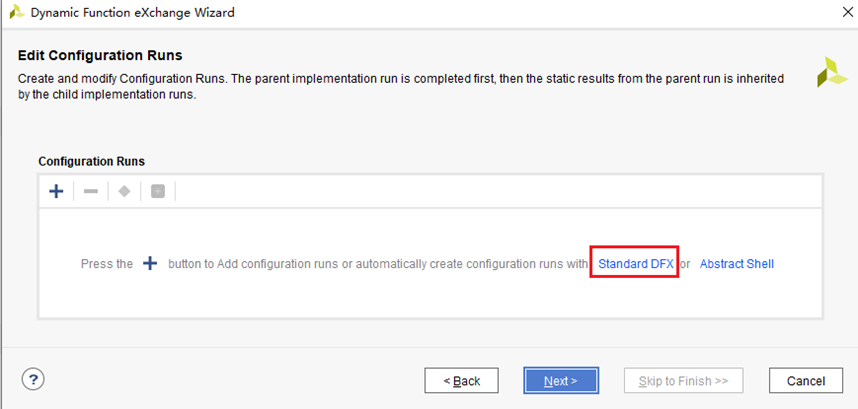

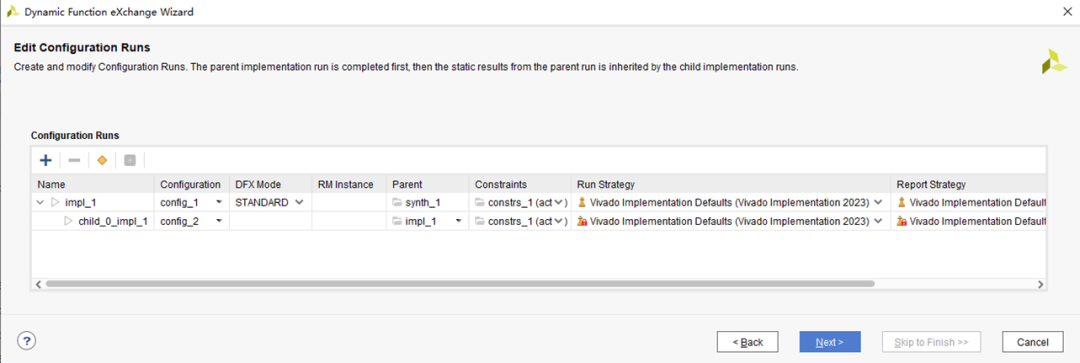

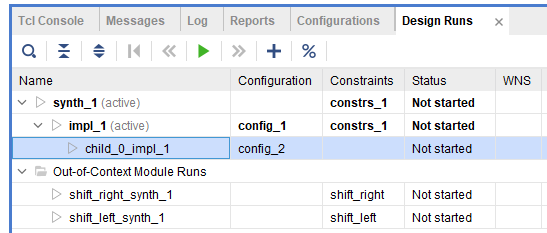

5. 點擊 Next,進入"Edit Configuration Runs" 頁面,把這些 Configuration 和直接的 Run 掛鉤。

和上一個頁面相似,點擊+號可以添加 Runs,這里我們直接點擊"Standard DFX", 工具會自動產(chǎn)生 Configuration Runs。

然后我們可以在這基礎上進行修改, 按需增減 Configuration Runs;同時通過下拉菜單設置每個 Run 的 Run strategy 和 Report Strategy。

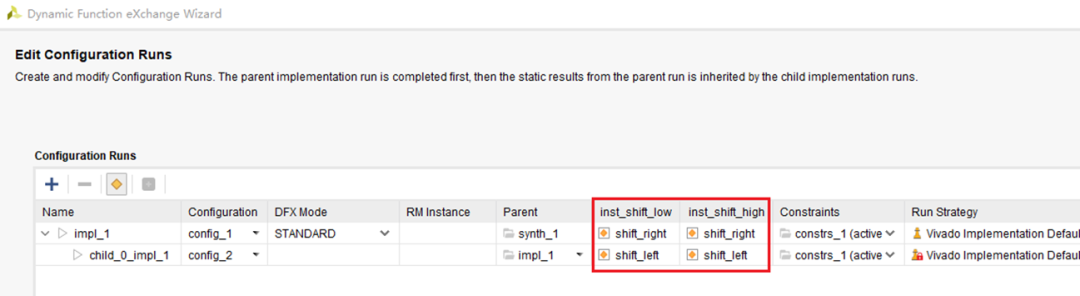

在此頁面上點擊黃色鉆石符號,可以顯示每個 Configuration Run 中的 RP 所包含 RM 的名字。

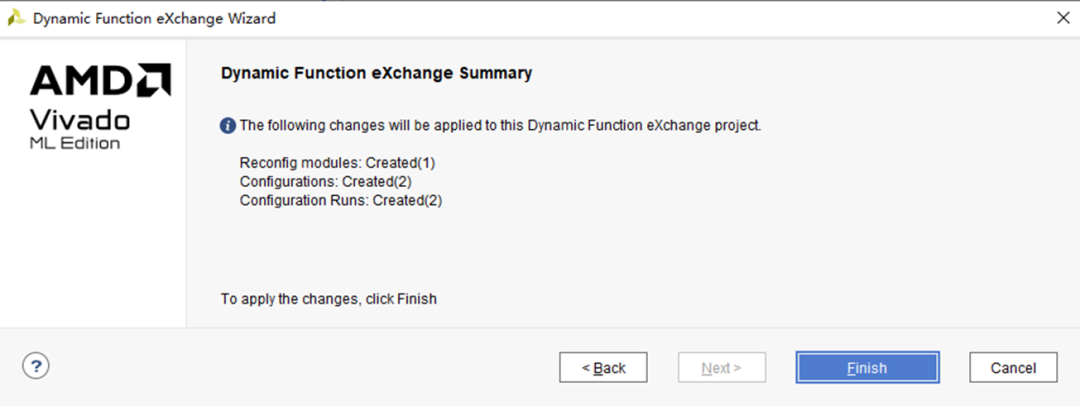

6. 點擊 Next 進入 Summary 頁面。

可以看到當次創(chuàng)建的RM,Configuration 以及 Configuration Runs 的數(shù)目。

點擊“Finish”退出 DFX Wizard。

? ? ?

? ? ?

5. 查看各個 RM 所包含的源文件

在 Source 窗口,Partition Definitions 中依次展開 RP, RM 可以看到每個 RM 中包含的源文件。

6. 在 Deisgn Runs 或者 Flow Naviagator 中啟動 Runs 的運行,直至生成比特流文件

Child Impl run 會使用和其 Parent Impl run 相同的靜態(tài)邏輯。

完成 Implementation 后,工具會自動執(zhí)行 Pr_verify 命令驗證這些 Run 之間邊界邏輯的一致性。

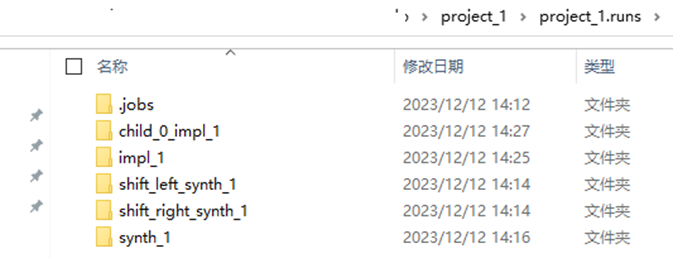

7. 在各個 Run 的目錄下,可以找到各自的 Full bit 和 Partial bit

審核編輯:劉清

-

TCL

+關注

關注

10文章

1722瀏覽量

88566 -

RTL

+關注

關注

1文章

385瀏覽量

59759 -

Vivado

+關注

關注

19文章

812瀏覽量

66470

原文標題:開發(fā)者分享|如何在 AMD Vivado? Design Tool 中用工程模式使用 DFX 流程

文章出處:【微信號:gh_2d1c7e2d540e,微信公眾號:XILINX開發(fā)者社區(qū)】歡迎添加關注!文章轉載請注明出處。

發(fā)布評論請先 登錄

相關推薦

用 TCL 定制 Vivado 設計實現(xiàn)流程

液晶電視工程模式

如何在Vivado中執(zhí)行工程變更命令 (ECO)

如何在Vivado Design Suite 中進行IP加密

用Tcl定制Vivado設計流程詳解

淺析Vivado在非工程模式下的FPGA設計流程

關于Vivado non-project模式

Vivado Design Suite 用戶指南介紹

AMD Vivado Design Suite 2023.2的優(yōu)勢

深入探索Vivado非工程模式FPGA設計流程

AMD Vivado Design Suite 2024.1全新推出

U50的AMD Vivado Design Tool flow設置

如何在AMD Vivado? Design Tool中用工程模式使用DFX流程?

如何在AMD Vivado? Design Tool中用工程模式使用DFX流程?

評論