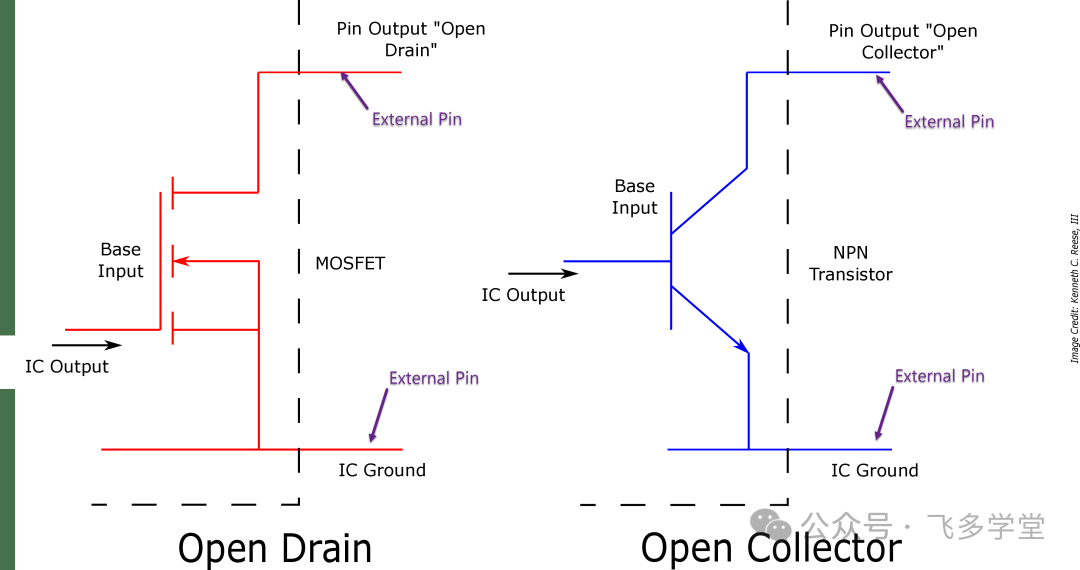

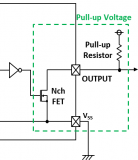

開漏(open-drain)或開集電極(open-collector)輸出引腳由單個晶體管驅動,將引腳拉到只有一個電壓(通常是接地)。當輸出設備關閉時,引腳被懸空(開啟,或高阻態)。

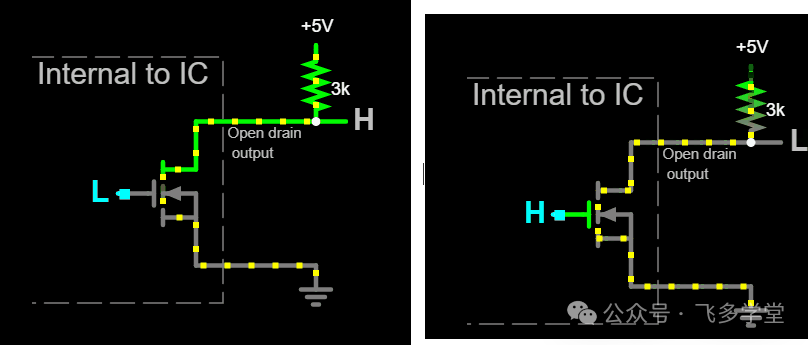

一個常見的例子是n溝道晶體管,當晶體管導通時,將信號拉向地,或者當晶體管關斷時,將信號保持開路。

開漏指的是在場效應晶體管技術中實現的這種電路,因為晶體管的漏極端口連接到輸出端;開集指的是雙極晶體管的集電極連接到輸出。

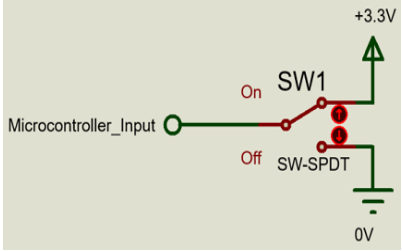

當晶體管關斷時,信號可以被另一個設備驅動,或者可以通過電阻上拉或下拉。電阻可防止未定義的漂浮狀態(高阻態)。

什么是開集輸出

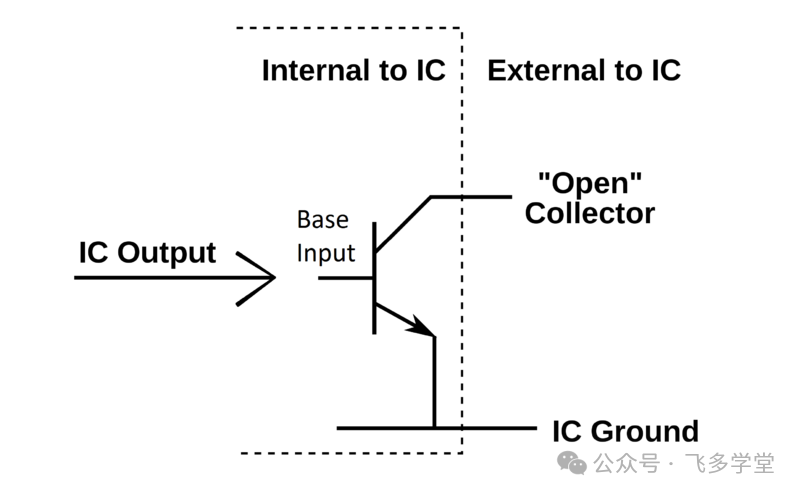

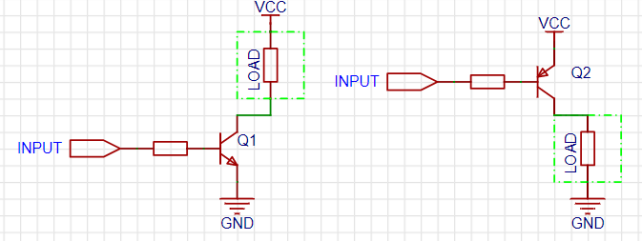

Open collector(開集)是一種電路輸出結構,它允許多個輸出設備共享一個電路線。在Open collector電路中,輸出器件可以將輸出線拉低(接地),但不能將其拉高。因此,當輸出器件拉低時,輸出線將被拉低,而當輸出器件不拉低時,輸出線將由上拉電阻上拉到高電平。這種結構通常用于數字電路和總線系統中。

集電極開路輸出通過內部雙極結型晶體管 (BJT) 的基極處理 IC 的輸出,該晶體管的集電極暴露為外部輸出引腳。

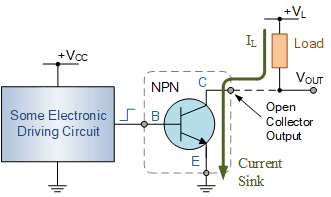

對于 NPN 開路集電極輸出,NPN 晶體管的發射極在內部接地, 因此 NPN 開路集電極在內部形成短路(技術上低阻抗或“低 Z”)連接到晶體管導通時的低電壓(可能接地),或晶體管關閉時的開路(技術上高阻抗或“hi-Z”)。輸出通常連接到外部上拉電阻,當晶體管關閉時,該電阻將輸出電壓拉至電阻的電源電壓。

對于NPN開漏輸出,NPN晶體管的發射極內部連接到地,因此當晶體管開啟時,NPN開漏內部形成短路(技術上是低阻抗或“低-Z”)連接到低電壓(可能是地線),或者當晶體管關閉時形成開路(技術上是高阻抗或“高-Z”)。輸出通常連接到外部上拉電阻,當晶體管關閉時,上拉電阻將輸出電壓拉到電阻的供電電壓。

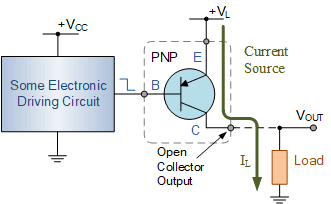

對于 PNP 集電極開路輸出,PNP 晶體管的發射極在內部連接到正電壓軌,因此集電極在晶體管導通時輸出高電壓,在晶體管截止時輸出高阻態。這有時稱為“集電極開路,驅動高”。

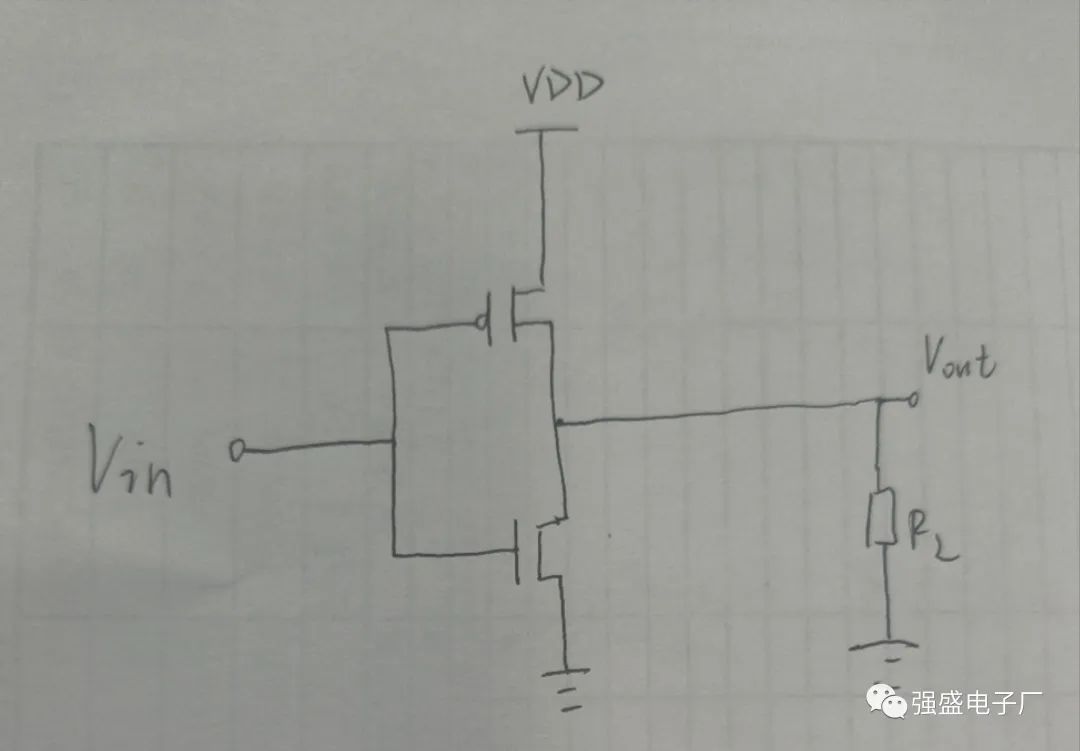

什么是開漏輸出

開漏輸出(Open drain)是一種電路設計中常見的輸出模式,它允許多個設備共享同一輸出線。在這種模式下,輸出端口可以被拉低以接地,但不能被拉高。這種設計可以用于連接到其他設備的輸入端口,以便它們可以通過外部上拉電阻來拉高輸出端口。

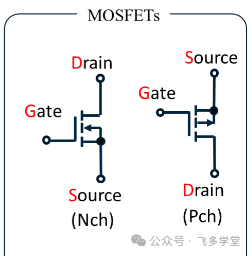

上圖中的 Drain 是漏極,Source 是源極。

開漏輸出使用 MOS 晶體管 (MOSFET) 代替 BJT,并將 MOSFET 的漏極暴露為輸出。

如果沒有外部上拉電阻,當高電壓施加到 MOSFET 柵極時,nMOS 開漏輸出接地,OK 沒問題。但是,當低電壓施加到柵極時呈現高阻抗。由于 MOSFET 不導通,該高阻抗狀態下的電壓將是浮動的(未定義),這就是為什么 nMOS 開漏輸出需要一個連接到正電壓軌的上拉電阻器以產生高輸出電壓。

使用 nMOS 開漏輸出的 MOS 管可能會提供“弱”(高電阻,通常約為 100 kΩ)內部上拉電阻,以將相關引腳連接到器件的正電源,因此它們的輸出電壓不會漂浮。這種弱上拉電阻由于其較低的 而降低了功耗,并且可能避免對外部上拉的需要。外部上拉可能會“更強”(較低的電阻,也許 3 kΩ),以減少信號上升時間(如 I2C)或最大限度地減少噪聲(如系統 RESET 輸入)。

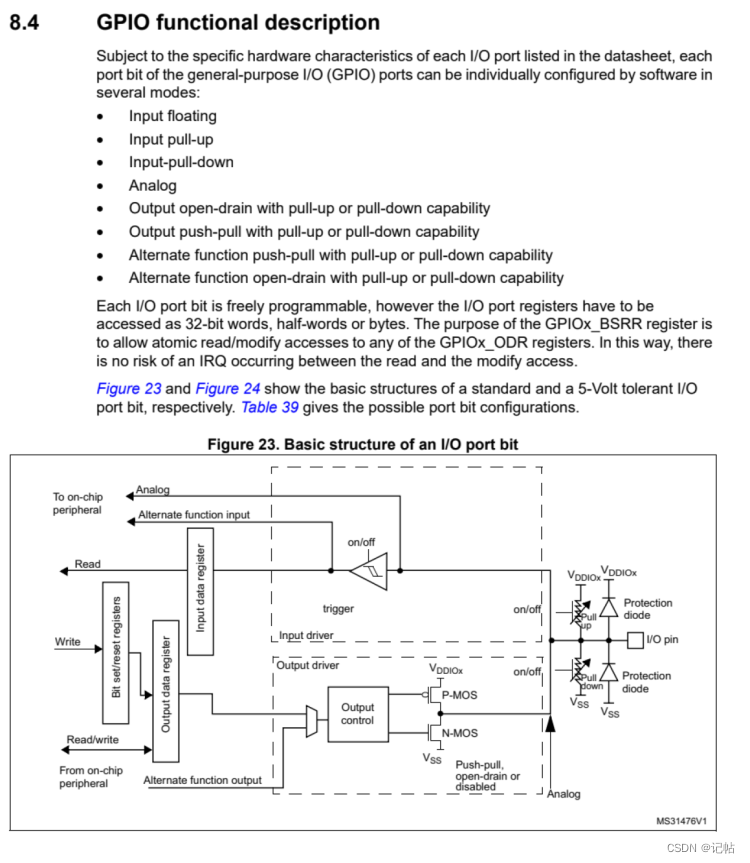

現代微控制器可能允許對特定輸出引腳進行編程,以使用開漏輸出而不是推挽輸出、內部上拉的強度,并允許在不需要時禁用內部上拉。

對于 pMOS 開漏極,當晶體管導通時,輸出連接到正電源軌,而當晶體管關斷時,輸出為高阻抗。這有時稱為“開漏,驅動高”。

應用

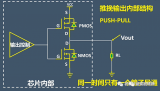

開漏輸出和開集輸出是兩種常用的電路輸出模式,它們的區別在于使用的器件不同,開漏輸出使用MOS管,開集輸出使用三極管。這兩種輸出模式的共同特點是高電平時輸出高阻,需要借助外部上拉電阻才能輸出高電平。這樣可以實現以下幾個方面的應用:

電平轉換:由于輸出電平由上拉電阻連接的電源電平決定,所以可以很方便地實現不同電平之間的轉換,例如從3.3V轉換到5V,或者從5V轉換到12V等。

線與功能:由于多個開漏輸出或開集輸出可以直接連接在一起,形成一個總線,所以可以實現線與功能,即只有當所有信號全部為高電平時,總線為高電平;只要有任意一個或者多個信號為低電平,則總線為低電平。這樣可以實現信號的邏輯運算和同步控制,例如在I2C總線中,就使用了開漏輸出來實現線與功能。

電流放大:由于開漏輸出或開集輸出的輸出電流由上拉電阻的大小決定,所以可以通過調節上拉電阻的阻值來實現電流的放大,例如在LED驅動中,就可以使用開漏輸出或開集輸出來提供較大的電流。

當然,開漏輸出和開集輸出也有一些缺點,例如:

輸出速度慢:由于輸出高電平時需要通過上拉電阻充電,而上拉電阻的阻值不能太小,否則會造成過大的功耗,所以輸出高電平的速度會受到限制,不能達到很高的頻率。

功耗大:由于輸出低電平時需要通過上拉電阻放電,而上拉電阻的阻值不能太大,否則會影響輸出電平的穩定性,所以輸出低電平時會有較大的功耗,不能實現低功耗的設計。

審核編輯:劉清

-

上拉電阻

+關注

關注

5文章

359瀏覽量

30607 -

MOS管

+關注

關注

108文章

2410瀏覽量

66759 -

晶體管

+關注

關注

77文章

9682瀏覽量

138080 -

電源電壓

+關注

關注

2文章

989瀏覽量

23969 -

開漏輸出

+關注

關注

0文章

34瀏覽量

7319

原文標題:開漏輸出和開集輸出的原理、特點和應用

文章出處:【微信號:mcu168,微信公眾號:硬件攻城獅】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

GPIO推挽輸出和開漏輸出模式區別詳解

一文詳解開漏輸出和開集輸出的原理、特點和應用

一文詳解開漏輸出和開集輸出的原理、特點和應用

評論