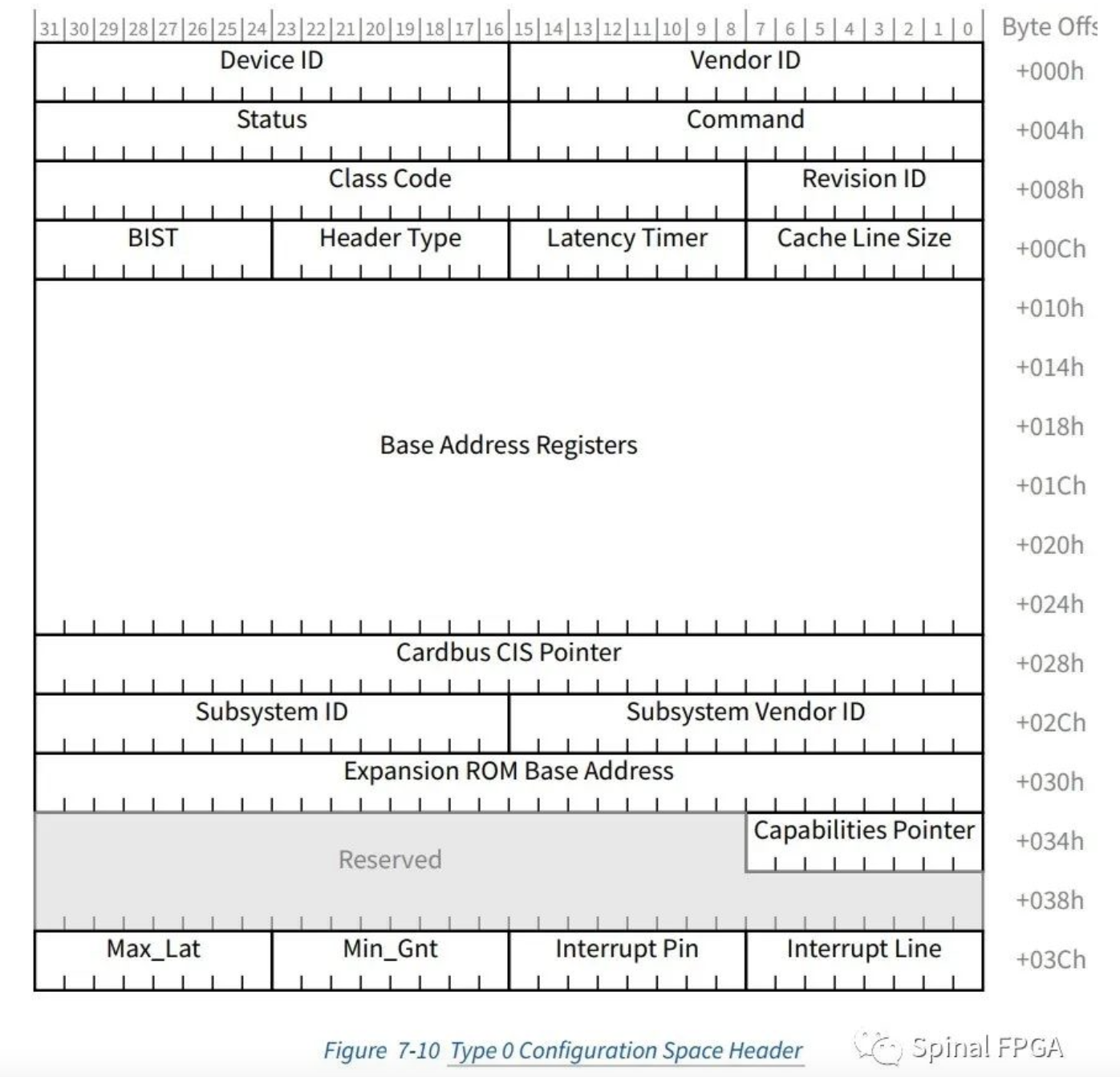

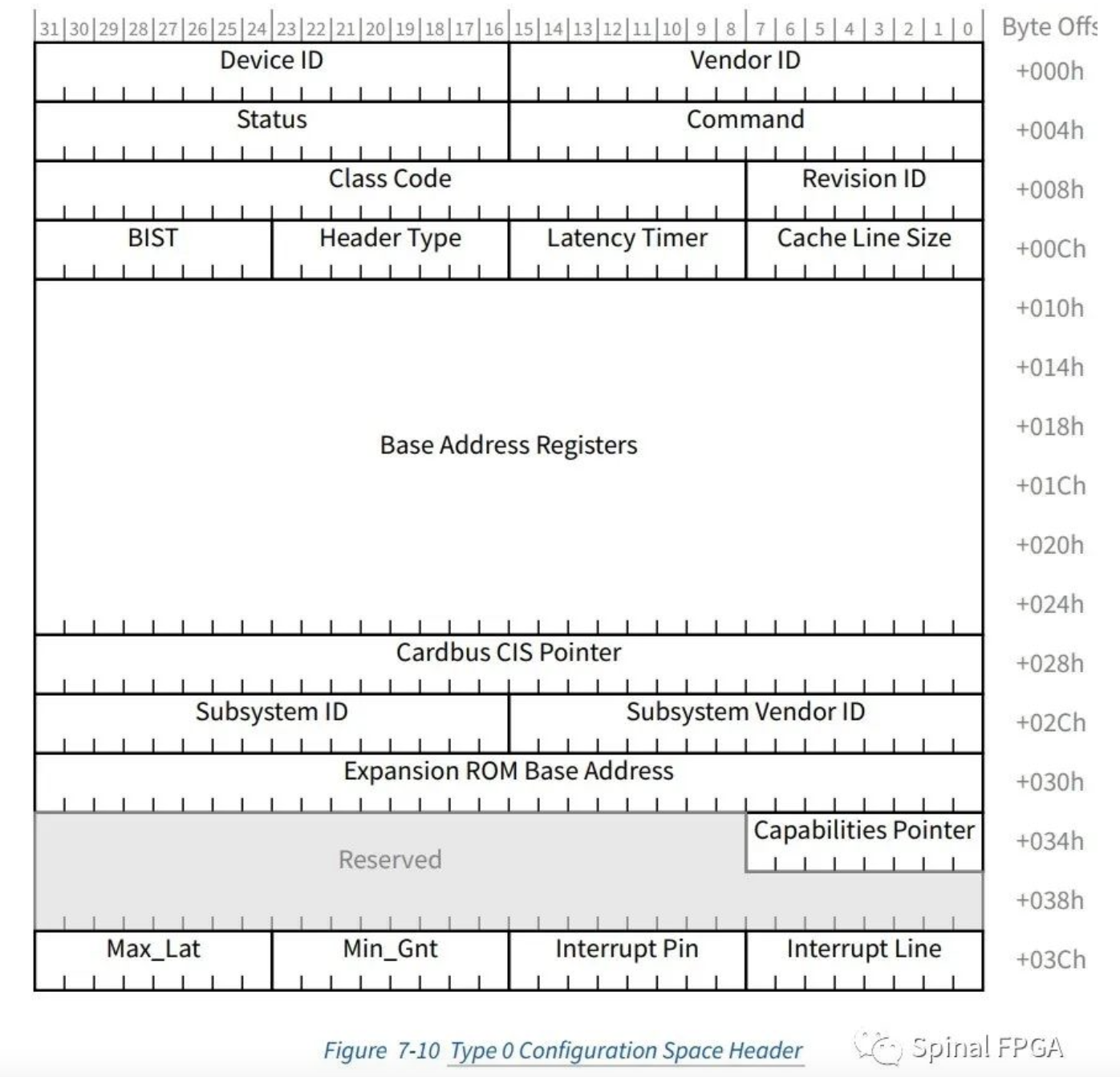

PCIE是一種高速串行總線接口標準,用于連接計算機內部的各種外設和組件。在PCIe架構中,BAR(Base Address Register)空間是用于映射I/O端口或內存地址空間的一組寄存器。

BAR空間是通過PCIe配置空間進行分配和管理的。每個PCIe設備都具有其自己的配置空間,其中包含了一組BAR寄存器。這些寄存器用于告知操作系統和其他設備該設備所需的資源,例如內存地址范圍或I/O端口地址范圍。

在PCIe設備的BAR寄存器中,可以配置為I/O BAR或者內存BAR。I/O BAR用于映射設備的I/O端口,而內存BAR用于映射設備的內存地址。每個BAR寄存器都包含一個基地址和一些控制位,用于指定地址范圍和訪問權限。

操作系統在初始化PCIe設備時,會讀取BAR寄存器的值,并將相應的資源映射到系統地址空間中,以便應用程序可以通過訪問這些地址來與設備進行通信。BAR空間的大小取決于每個BAR寄存器的配置,通常情況下,每個BAR寄存器的大小為32位或64位。

需要注意的是,BAR空間的大小可能會受到一些限制,例如操作系統或主板的限制。因此,在進行PCIe設備設計和驅動程序開發時,需要遵循相關的規范和要求,以確保BAR空間分配的合理性和可用性。

總結起來,PCIe的BAR空間是用于映射設備的I/O端口或內存地址空間的一組寄存器,通過配置寄存器的值,可以告知操作系統和其他設備該設備所需的資源。操作系統會將BAR空間映射到系統地址空間中,以便應用程序可以與設備進行通信。

審核編輯:劉清

聲明:本文內容及配圖由入駐作者撰寫或者入駐合作網站授權轉載。文章觀點僅代表作者本人,不代表電子發燒友網立場。文章及其配圖僅供工程師學習之用,如有內容侵權或者其他違規問題,請聯系本站處理。

舉報投訴

原文標題:pcie的BAR空間的介紹

文章出處:【微信號:gh_9d70b445f494,微信公眾號:FPGA設計論壇】歡迎添加關注!文章轉載請注明出處。

相關推薦

我使用windriver開發了pcie的驅動,可以通過windriver看到分配的bao0和bar1空間,其地址范圍對應的是DDR3的空間,此時出現問題:可以通過windriver對

發表于 03-28 16:06

:

?????????????? 1.如何將DM8168 PCIe寄存器(地址是0x51000000)映射到它的內核空間,這樣我就可以在內核空間通過訪問其對應的虛擬地址查看PCIe寄存

發表于 05-28 01:52

\drv\exampleProjects\PCIE_exampleProject 里面的例子

這個工程可以成功跑起來,并且在PC端通過用WinDriver可以看到設備,但是目前有一個關于例程中BAR配置

發表于 06-19 00:50

設備。現在有幾個問題想要搞明白:

1.pdk的PCIE例程中配置了bar1基地址為0x70000000,我通過WinDriver查看bar1基地址也是0x70000000,然后用WinDriver在

發表于 06-19 04:33

link 完成后, 在本地PCIE config空間映射的 EP端的config空間,

后續初始化EP端Bar base地址的時候,就是操作?gpPCIE_remote_EP_reg

發表于 06-21 18:49

it to the?internal bus side.”

1.這段話的大概意思是說PCIe接收數據包是有條件的,只有數據包中的PCIe地址在BAR配置的地址范圍內時,PCIe模塊才

發表于 06-21 18:17

各位大家好,我正在嘗試使用我在Xilinx論壇下載的SP605連接套件參考設計,我閱讀了用戶指南:我了解了如何通過BAR0和BAR1訪問(讀/寫)寄存器,但我不明白如何通過PCIe(當然還有DMA

發表于 07-09 08:40

嗨,我正在使用AXI-PCIe橋接IP與我的邏輯進行通信。我的poroject要求有128K內存。我不知道如何配置AXI BAR地址來擴展內存。我閱讀了IP文檔,但沒有任何意義。目前我能夠從具有32K PCIe

發表于 06-19 10:14

板卡集成了16M*32Bit的SDRAM, 可通過BAR3空間+頁地址訪問。BAR3空間在本協議中規定為1M*32Bit的空間。所有的SDR

發表于 05-14 16:23

| 一、貴司3588J開發板,4x PCIe插槽插入我司的PCIe采集卡,無法進行大容量64MB的高端 BAR Memory地址空間分配問題:1、lspci、lspci -vvv 及相

發表于 10-20 14:56

0x18900000-0x1890ffff pref][5.246523] pci 0000:01:00.0:BAR 0:[mem size 0x400000000 64bit pref]沒有空間[5.254191

發表于 04-11 06:30

可以表明主機與FPGA硬核能夠鏈接成功,link_up后主機內核程序可以讀到PCIE的配置空間信息,進而給FPGA的PCIE分配PCIE總線域空間

發表于 11-17 14:35

PCIe接口相對來講還是打交道比較多的接口。無論是Intel還是Xilinx的IP也都接觸到過。

![的頭像]() 發表于

發表于 06-05 10:47

?6608次閱讀

最近在研究cocotbext-pcie的實現,對于學習PCIe還是挺有幫助的,陸陸續續做個總結,有時間也會在SpinalHDL下實現類似的方針功能。

![的頭像]() 發表于

發表于 07-03 17:47

?4100次閱讀

CPU 發起的,訪問PCIe設備配置空間的數據流。這種數據流主要是BIOS/Linux PCIe driver 對設備進行初始化、資源分配時,讀寫配置空間的。包括

![的頭像]() 發表于

發表于 09-15 09:39

?1700次閱讀

PCIE的BAR空間介紹

PCIE的BAR空間介紹

評論