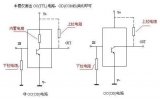

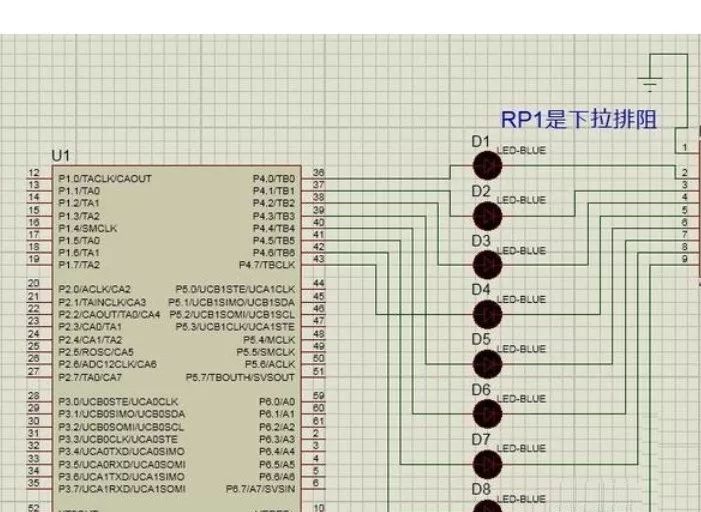

下拉電阻是一種常見的電子元件,用于在沒有輸入或輸入為高阻抗狀態時,將電路節點固定在低邏輯電平(通常是地或負電源)。其主要作用包括:

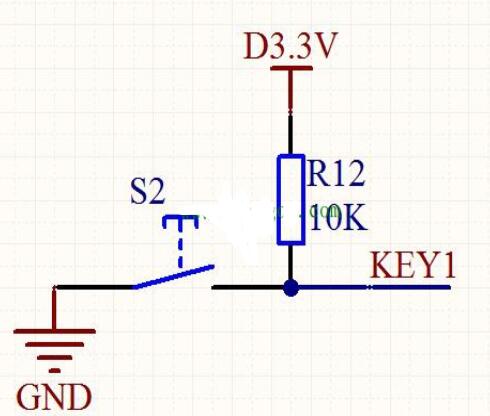

確保默認邏輯電平:下拉電阻可以保證即使沒有信號輸入或微控制器引腳配置為高阻態時,相關節點仍然能保持一個確定的低邏輯電平。這對于確保邏輯電路的默認行為特別重要。

防止輸入引腳懸空:當微控制器或其他數字設備的引腳沒有驅動時,這些引腳可能會處于高阻態,也稱為“懸空”。下拉電阻可以避免這種情況,防止因外部干擾而導致的不確定行為。

抗干擾能力提升:由于電磁干擾或者線路上的噪聲可能導致信號異常,下拉電阻可以將錯誤的高電平拉回至低電平,從而減少誤觸發的可能性。

增強系統穩定性:在數字電路中,下拉電阻通過提供明確的低電平狀態,有助于提高整個系統的穩定性和可靠性。

實現特定的邏輯功能:在某些情況下,下拉電阻可以用來實現特定的邏輯設計,例如,將多個開關并聯使用時,通過下拉電阻可以實現“有任何一個開關閉合,輸出即為低”這樣的邏輯功能。

節省能源:當下拉電阻用于CMOS輸入時,由于CMOS輸入的高阻抗特性,下拉電阻實際上消耗的功率非常小,有利于降低能耗。

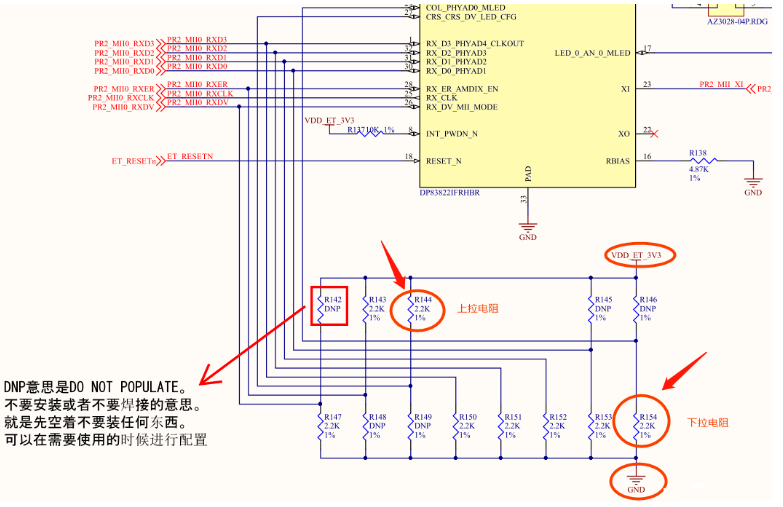

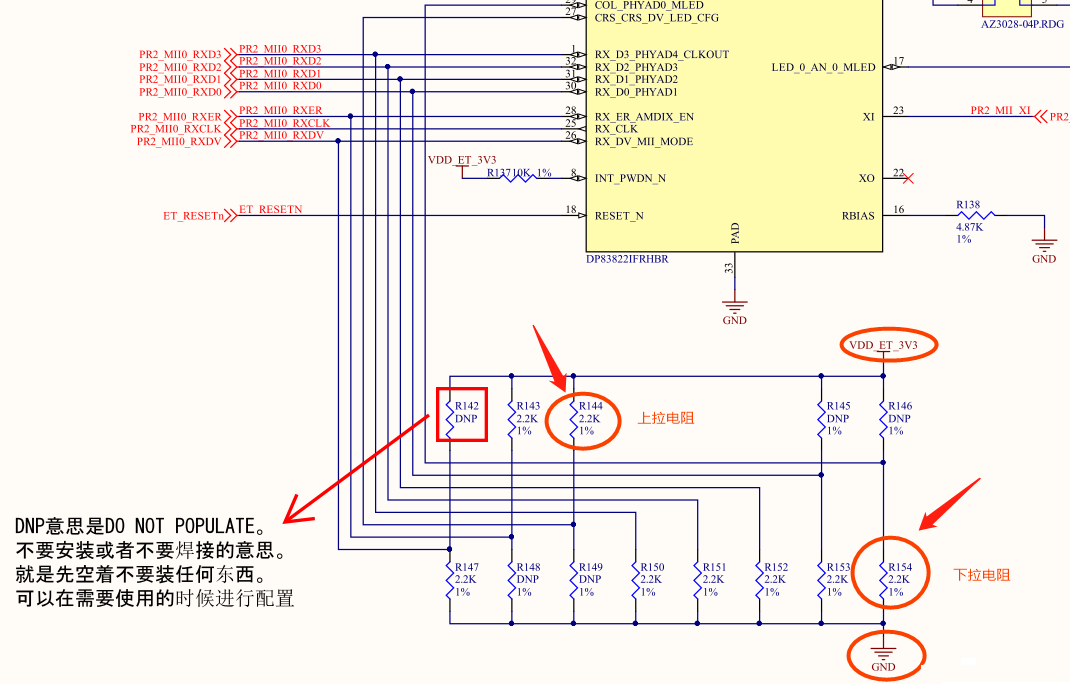

改善總線行為:在數據總線上,下拉電阻可以與上拉電阻一起使用來改善信號質量和總線的穩定性。例如,在I2C總線上,既需要上拉電阻也需要下拉電阻來穩定總線狀態。

實現電源順序控制:在一些需要按特定順序加電的系統中,下拉電阻可以保證某些線路在未達到特定條件前保持低電平,從而控制電源開啟的順序。

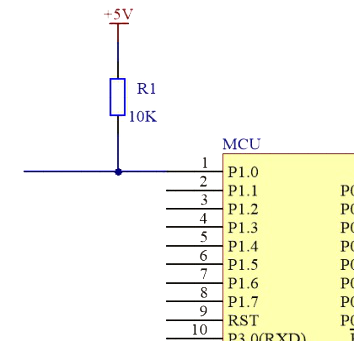

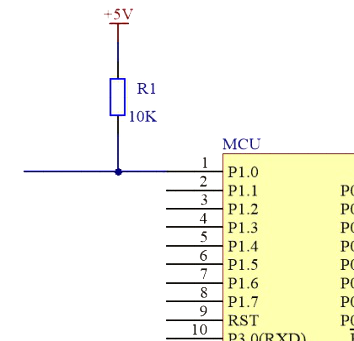

輔助設備復位:下拉電阻通常用在微處理器的復位引腳上,配合上拉電阻使用,以確保微處理器能夠可靠地從復位狀態進入正常工作狀態。

調試和測試:在開發和測試階段,下拉電阻可用于將引腳固定在已知狀態,以便更容易地進行調試和驗證電路的行為。

下拉電阻是電子電路設計中不可或缺的組件之一,它有助于提高電路的魯棒性、穩定性和可靠性。無論是作為默認邏輯電平的保證,還是作為抗干擾措施,或是在復雜的電源管理和邏輯設計中,下拉電阻都扮演著重要的角色。

-

下拉電阻

+關注

關注

4文章

147瀏覽量

20525 -

控制器

+關注

關注

112文章

16332瀏覽量

177806 -

電阻器

+關注

關注

21文章

3779瀏覽量

62114

發布評論請先 登錄

相關推薦

上拉電阻和下拉電阻作用、區別和應用

什么是上拉電阻,什么是下拉電阻?它們的作用是什么?

下拉電阻的作用有哪些

下拉電阻的作用有哪些

評論