00引言

近幾十年來,半導體技術的飛速發展為信息技術革命提供了強大的技術支撐,在此期間指導半導體器件研發及其產業化發展的國際半導體技術發展路線圖發揮了重要作用。國際半導體技術發展路線圖不斷得到滾動修訂,是國際半導體工業界廣泛認同的對未來半導體技術發展的最佳預測。2016年,國際半導體技術發展路線圖被修訂為國際器件與系統路線圖,這一調整充分反映出基于摩爾定律的單純器件技術發展遇到瓶頸,器件與系統的聯動發展已成為半導體技術發展的主題。針對這一發展趨勢,美國在上世紀九十年代就成立了微系統技術辦公室(MTO),其重點工作就是推進半導體器件與系統的融合發展,滿足系統應用對器件技術不斷增長的需求。本文圍繞后摩爾時代半導體微波器件技術的發展,介紹了開發的基于外延層轉移的晶體管級異質集成技術,并結合南京電子器件研究所(NEDI)的工作,展示了該技術在典型微波功率器件和電路工藝中的應用。

01后摩爾時代半導體微波器件技術的主要發展趨勢

后摩爾時代半導體技術的發展主要有延續摩爾和超越摩爾兩條路徑。延續摩爾就是通過尋找新的物理機理、發現新的材料、設計新的器件結構,將器件的工藝能力推向更高的節點,滿足電路芯片更高性能和更高集成度等發展需求。如采用碳納米管研制的晶體管[1],由于材料性能優勢,相比于同樣柵長的SiCMOS可實現更高的速度和更低的功耗,有望通過新的半導體材料提升器件的工藝節點。超越摩爾則是在摩爾定律充分發展的基礎上通過異類集成實現電路性能和功能的提升。異類集成的方法很多,在Si集成電路領域,更多的是通過晶圓級封裝(WLP)的三維堆疊來實現,目前已有標準工藝,并實現了量產。這種三維集成不僅僅是同類功能電路晶圓的堆疊提升集成度,同時也可以是不同功能電路晶圓的堆疊,實現電路功能的增加,甚至構成片上系統(SOC),這一技術將成為后摩爾時代Si集成電路工藝技術發展的主流。

半導體微波器件是半導體器件大家族中的重要一員,后摩爾時代半導體微波器件的發展也同樣存在SiCMOS遇到的瓶頸。不同于Si元素半導體,作為半導體微波器件發展主體的GaAs、InP、GaN等化合物半導體材料有非常豐富的異質結,異質結的采用可顯著提升器件的頻率、功率、線性等微波性能,大大拓展各種半導體襯底材料的應用空間。盡管如此,由于晶格失配、熱失配以及外延生長工藝等因素的影響,高性能化合物半導體異質結的形成也受到種種限制,阻礙了單一化合物半導體器件微波性能的進一步提升。

類似于Si集成電路,后摩爾時代半導體微波器件技術也將沿著延續摩爾和超越摩爾兩條路徑發展。一方面將繼續通過新型半導體材料[2]、新型異質結[3]、新的器件結構[4]提升器件的微波性能,另一方面則通過異類集成實現電路性能和功能的提升。 在異類集成方面,美國國防高級研究計劃局(DAR-PA)近十多年來持續支持了“硅上化合物半導體材料(COSMOS,2008年)”、“多樣化可用異類集成技術(DAHI,2012年)”和“通用異類集成和IP復用策略(CHIPS,2017年)”等多個重大項目[5-7]的研究,突破了異類集成關鍵技術,建立了異類集成標準工藝平臺[8],為產品開發奠定了技術基礎。歐盟也于2015年啟動INSIGHT項目,旨在研發與Si CMOS相兼容的III-V族材料生產工藝以及在Si器件上的異類集成技術,面向超大功率、超寬帶的微波毫米波應用,在實現高集成度和低功耗的同時,提升電路的工作帶寬、輸出功率和效率等微波性能。

半導體微波器件的異類集成又有兩種不同技術發展方向,一種是類似于Si電路的圓片到圓片(Wafer to wafer)或芯片到晶圓(Die to wafer)的三維堆疊集成技術,另一種則是更充分體現半導體微波器件特點的晶體管級異質集成技術。為區分兩類不同集成技術,前一種多稱為三維異構集成,后一種則稱為異質集成。這兩種不同技術發展方向其技術特點有明顯區別,前一類針對芯片間的集成,后一類則深入到不同材料、不同結構晶體管的集成。下面將重點介紹半導體微波器件異類集成技術中晶體管級異質集成技術的發展情況以及南京電子器件研究所在此技術方向的研究進展。

02基于外延層轉移的晶體管級異質集成微波器件技術

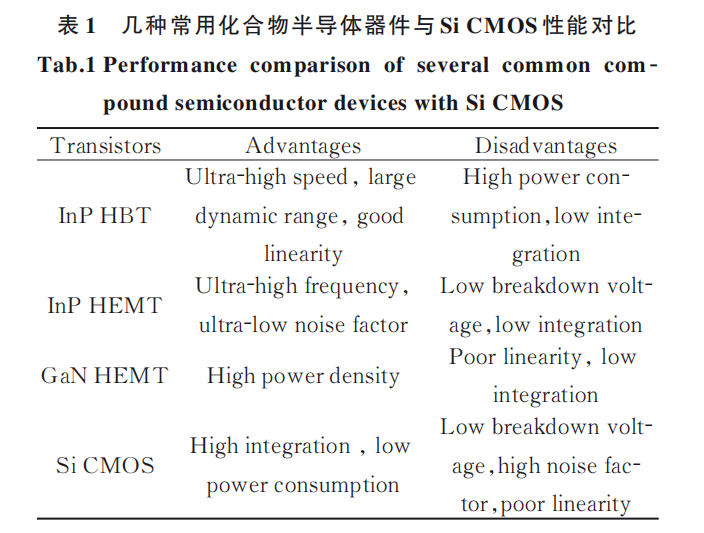

化合物半導體微波器件的典型特點是不同結型器件性能差異明顯,表1給出了幾種常用的化合物半導體微波器件與Si CMOS性能對比,另外化合物半導體還擁有GaAs PIN二極管、GaAs超突變結變容管等多種功能器件,晶體管級異質集成就是根據微波性能和功能需要,選擇性能最合適的半導體器件集成到某一特定半導體襯底上,化合物半導體襯底本身由于其導熱等性能差異,也是可選的集成對象,從而獲得單一器件技術難以實現的器件或電路性能,擺脫在各類器件技術間權衡取舍的困境。不同于芯片到晶圓以及圓片到圓片的三維異構集成,晶體管級異質集成針對單個晶體管,集成精度達到微米級。

晶體管級異質集成技術其工藝途徑主要有外延生長和外延層轉移兩種,外延生長異質集成典型的應用范例如微波接收系統所用的限幅低噪聲放大器電路、光通信系統中應用的光探測器與跨阻放大器單片集成的光電集成電路(OEIC)等。外延生長異質集成技術涉及到多種結構異質結的依次生長、不同結型晶體管的制作,其工藝難度顯而易見。不同結型器件工藝的兼容性問題還會影響器件性能,特別是芯片生產成本會明顯增加。外延層轉移晶體管級異質集成技術,是將完成主要正面工藝的外延層通過剝離轉移并鍵合到另外一個也已完成主要正面工藝的晶圓上,最后互連起來完成整個電路的加工。外延層轉移集成工藝可有效規避外延生長集成工藝存在的弊端,實現高性能、高集成目標。化合物半導體微波器件有GaAs pHEMT、GaN HEMT等平面結構器件與InP HBT、GaAs PIN等縱向結構器件兩大類。平面結構器件其微波性能與外延層下高阻襯底的厚度密切相關,因此需開發介質鍵合工藝來保證器件的微波性能不受影響。基于InP HBT、GaAs PIN等縱向結構器件的微波電路,為減小電路損耗,有源器件均采用準平面結構制作在半絕緣襯底上。針對縱向結構器件的晶體管級異質集成,則完全可以恢復其縱向特征,通過金屬鍵合到半絕緣襯底上,進一步提升器件的微波性能。介質鍵合和金屬鍵合的工藝溫度都不高,均屬于低溫鍵合。

近年來在各國多個重點計劃的推動下,國際上晶體管級異質集成技術的研究也異彩紛呈。2017年德國FBH研究所采用外延層剝離轉移介質鍵合工藝,研制出InP HBT與Si CMOS異質集成的328 GHz頻率源,該芯片集成了SiGe VCO和InP放大器及倍頻器,功耗和輸出功率優于SiGe工藝電路[9]。2019年美國Teledyne公司報道了基于外延層轉移工藝的W波段相控陣收發芯片[10],該芯片由0.25μm InP HBT與0.13μm Si CMOS異質集成而成,芯片集成了移相器、放大器和低噪放等多個功能。該芯片在90GHz飽和輸出功率16dBm,同時直流功耗僅為885mW。其直流功耗、發射增益、噪聲特別是輸出功率等性能,均不同程度優于SiGe BiCMOS工藝芯片。近十多年來NEDI在國內率先開展了外延層轉移異質集成技術研究,2015年實現了GaAs pHEMT與Si CMOS異質集成數控開關芯片之后,2017年實現了InP HBT與SiCMOS異質集成量化降速芯片[11],該電路工作速率13GHz,對低頻和高頻數據信號降速比達到1∶16,功耗小于1.2W,相較采用InP HBT工藝芯片功耗降低40%,相較采用40nm Si CMOS工藝芯片靈敏度和動態范圍分別改善15dB和20dB。下面將給出NEDI在這一技術方向研究的新進展,并系統介紹介質鍵合和金屬鍵合兩套外延層轉移異質集成工藝在典型微波器件和電路工藝中的應用。

2.1介質鍵合晶體管級異質集成工藝

基于SiC襯底的GaNHEMT微波功率器件是近二十多年發展起來的新一代半導體微波器件技術,充分體現材料性能優勢的GaN微波功率器件和電路產品已在電子信息裝備和移動通信基站等領域得到規模應用。目前工程應用的GaN HEMT其輸出功率密度普遍低于10W/mm,而GaN HEMT已驗證的最高輸出功率密度可達到41.4W/mm[4],GaN微波功率器件性能還有巨大提升空間。散熱是制約GaN HEMT輸出功率密度提升的瓶頸,異質集成金剛石GaN微波功率器件是解決這一瓶頸問題的有效途徑[12],基于介質鍵合的金剛石GaN HEMT是外延層轉移晶體管級異質集成技術的一個典型應用。

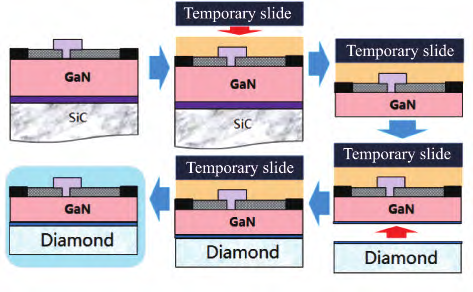

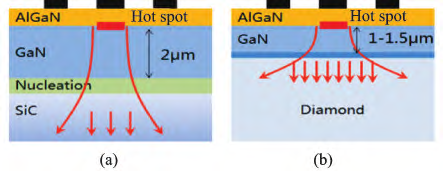

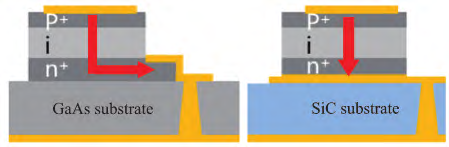

介質鍵合金剛石GaN HEMT具體工藝過程示意圖如圖1所示。先完成GaN器件工藝,然后去除SiC襯底并鍵合到高導熱多晶金剛石上。該工藝在低溫條件下完成,緩解了GaN與金剛石存在的嚴重熱失配;先器件后鍵合,可充分發揮SiC襯底GaN HEMT工藝成熟以及金剛石導熱襯底單獨制備所帶來的各自性能優勢。當然該工藝也存在鍵合界面空洞率及界面熱阻控制等工藝難題,需要重點攻克。在金剛石GaN HEMT研制方面,NEDI開展了多年研究,近年來突破了金剛石襯底GaN微波功率器件內部熱傳輸機制、GaN外延層表面納米級拋光以及金剛石襯底與GaN外延層低溫鍵合等關鍵技術,目前已實現的界面熱阻優于40m^2K/GW,這一結果距離國外報道的介質鍵合最好水平還有提升空間[13]。圖2是完成工藝的金剛石GaN HEMT與現有SiC襯底GaN HEMT結構示意圖。

圖 1 金剛石 GaN HEMT 異質集成器件工藝流程示意圖

圖 2 (a) SiC 襯 底 GaN HEMT 與 (b) 金 剛 石 襯 底 GaNHEMT 結構示意圖

基于該工藝研制出典型柵寬金剛石GaN HEMT,8×50μm柵寬、20μm柵間距的0.25μm柵長的GaN HEMT,在10GHz負載牽引,80V工作下,輸出功率密度15.36W/mm,功率增益14.95dB,功率附加效率(PAE)55.3%。

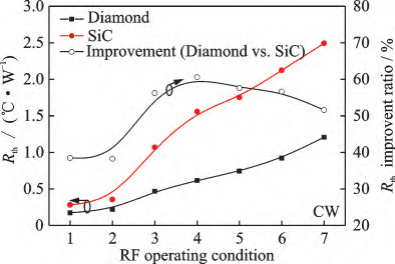

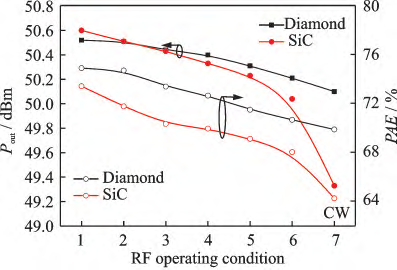

基于該工藝研制出22.4mm柵寬管芯,管芯柵柵間距為53μm,單指柵寬為350μm,芯片尺寸4.25mm×1.00mm,兩種器件的裝配和電路匹配一致,射頻工作條件從窄脈寬到連續波(CW),脈寬/占空比分別為50μs/10%、100μs/10%、1ms/10%、3ms/10%、3ms/30%、5ms/50%以及CW共7種條件,工作頻率1.5GHz,工作電壓28V,輸入功率40dBm。圖3給出了金剛石襯底GaN HEMT與SiC襯底GaN HEMT兩種工藝22.4mm柵寬器件在不同工作狀態下熱阻變化情況,可以看出兩種工藝器件熱阻(Rth)從窄脈寬到連續波均增大7~9倍。但相對于SiC襯底GaN HEMT器件,金剛石GaN HEMT熱阻明顯改善,在器件工作脈寬超過1ms的高熱耗下工作時,熱阻下降幅度超過50%,驗證了金剛石襯底GaN HEMT熱阻改善效果。

圖3兩種工藝22.4 mm柵寬器件在不同工作狀態下熱阻變化情況 圖4給出了兩種器件在上述的窄脈寬到連續波不同工作條件下輸出功率和功率附加效率的對比(輸入功率均為40dBm),可以看出金剛石襯底GaN HEMT器件輸出功率(Pout)、PAE分別下降0.42dB和5.0個百分點,對應SiC襯底GaN HEMT器件Pout、PAE分別下降1.27dB、9.2個百分點,連續波工作條件下金剛石襯底GaN HEMT器件Pout、PAE相當于SiC襯底GaN HEMT器件分別改善0.77dB和5.6個百分點,這一結果也進一步展示了金剛石GaN HEMT的散熱效果。

單位毫米柵寬器件輸出功率密度是表征器件性能水平的關鍵指標,不僅決定器件和電路的輸出功率能力,同時還對器件和電路的工作帶寬、效率等性能有重要影響。更大的輸出功率、更高的工作頻率、更高的效率是固態微波功率器件技術不懈努力的目標。金剛石GaN異質集成可有效改善現有SiC襯底GaN HEMT的散熱問題,結合GaN HEMT的AlGaN/GaN異質結材料生長、管芯結構設計及關鍵工藝的優化,提高GaN HEMT高壓工作的可靠性,可推進GaN HEMT器件向更高輸出功率密度的技術發展,為超大功率器件以及更高性能電路的實現提供工藝保證。另外熱管理技術也是固態微波功率器件研究永恒的主題,金剛石GaN異質集成將為長脈寬、高占空比、連續波、大功率等高熱耗應用電子信息系統的散熱和可靠性提升提供強有力的技術支撐。

圖 4 兩種工藝 22.4 mm 柵寬器件在不同工作狀態下輸出功率和效率變化情況

介質鍵合晶體管級異質集成技術在射頻多功能電路的研制中有多種應用,典型的如GaAs低噪聲pHEMT與GaN HEMT功率放大電路單片集成實現的射頻前端電路,可充分發揮GaAs低噪聲pHEMT低噪聲、低功耗以及GaNHEMT高功率各自性能優勢,解決單一GaN HEMT工藝前端電路存在的功耗大等難題。

2.2金屬鍵合晶體管級異質集成工藝

限幅器是射頻前端電路的一個重要功能電路,耐功率能力、限幅電平以及插入損耗是限幅器相互制約的關鍵性能指標。高耐功率能力要求PIN管芯具有較小的導通電阻,這需要增大結面積實現,結面積增大將引入較大的結電容,導致限幅電平和插入損耗增加,同時還將影響電路的工作帶寬。系統應用的限幅器多為單片形式,目前的限幅器電路主要采用GaAs襯底的GaAs PIN通過準平面結構實現。基于GaAs PIN與高導熱的SiC襯底金屬鍵合的異質集成限幅器,可恢復GaAs PIN的縱向結構,同時利用SiC的高導熱性,提高現有GaAs PIN限幅器性能水平。

GaAs PIN與SiC的異質集成工藝與金剛石GaN HEMT基本一致,主要不同點在于鍵合前GaAs PIN需完成陰極歐姆接觸工藝,SiC襯底上需制備好金屬電極,GaAs PIN與SiC襯底通過金屬直接鍵合,兩者的套刻誤差可控制在1μm以內。圖5為常規GaAs襯底PIN與異質集成SiC襯底GaAsPIN結構示意圖。

圖 5 常規GaAs襯底PIN與異質集成SiC襯底GaAs PIN結構示意圖

針對研制的兩種PIN建立了器件模型,表2給出了兩種不同結構PIN的導通電阻、結電容以及兩者乘積的比較,兩種管芯的陽極尺寸一致,可以看出異質集成器件導通電阻明顯降低,結電容也有一定程度下降,這均為限幅器插損、限幅電平、耐功率能力等性能提升奠定了基礎。

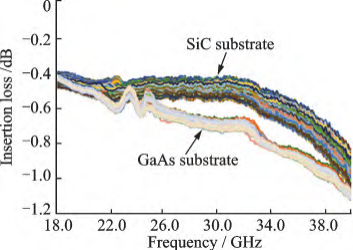

對采用該工藝研制的18~40GHz限幅電路進行了微波性能測試。圖6給出了兩種工藝電路插入損耗測試結果的分布情況,可以看出與常規GaAs襯底GaAs PIN限幅電路相比,GaAs PIN與SiC襯底異質集成電路損耗小約0.2dB。限幅電平和耐功率能力測試結果表明兩種電路限幅電平基本一致,異質集成工藝電路耐功率能力提高3dB以上。

圖 6 兩種工藝 18~40 GHz 限幅器電路插入損耗在片測試結果比較

金屬鍵合晶體管級異質集成技術在射頻多功能電路的研制中有多種應用,典型的如限幅低噪聲放大器電路,相對于通過外延依次生長低噪聲pHEMT和PIN兩種異質結材料實現的限幅低噪聲放大電路,采用金屬鍵合異質集成技術,GaAsPIN可采用MOCVD技術生長,外延片成本可降低,細線條的GaAs pHEMT單獨加工,工藝成品率可提高,在實現限幅器性能提升的同時可有效降低芯片生產成本。另外在SiC襯底GaN上采用金屬鍵合集成GaAs PIN和采用介質鍵合集成GaAs pHEMT,可實現高性能的射頻前端電路,凸顯晶體管異質集成技術在多功能電路研制方面的技術優勢。

03結論

后摩爾時代單一半導體微波器件技術的發展受到限制,通過不同技術途徑異類集成各具特色的半導體器件及半導體襯底實現器件或電路性能與功能提升成為后摩爾時代半導體微波器件技術發展的主流。介紹了基于外延層轉移工藝的晶體管級異質集成技術,展示了開發的分別適用于平面和縱向兩類不同結構器件的介質鍵合和金屬鍵合兩套工藝,采用這兩套工藝分別研制出金剛石襯底GaN HEMT微波功率器件和SiC襯底GaAs PIN限幅器電路。測試結果表明,與常規的SiC襯底GaN HEMT相比,金剛石GaN HEMT器件散熱特性明顯改善,高熱耗工作下器件熱阻減小超過50%,器件連續波工作輸出功率和功率附加效率分別提高0.77dB和5.6個百分點。與常規的GaAs襯底GaAs PIN限幅器相比,研制的18~40GHz SiC襯底GaAs PIN限幅器電路限幅電平基本一致、插入損耗改善約0.2dB、耐功率能力提高3dB以上,研制結果顯示出外延層轉移晶體管級異質集成技術廣闊的應用前景。

04文章信息 文章題目:晶體管級異質集成技術及其典型應用 作者與單位:陳堂勝1,2,戴家赟1,2,吳立樞1,2,孔月嬋1,2,周書同1,2,齊志央1,鐘世昌1,2,凌志健1 1 南京電子器件研究所,南京;2 固態微波器件與電路全國重點實驗室,南京; 審核編輯:黃飛

-

集成電路

+關注

關注

5400文章

11689瀏覽量

364529 -

二極管

+關注

關注

148文章

9852瀏覽量

168327 -

晶體管

+關注

關注

77文章

9829瀏覽量

139396 -

功率器件

+關注

關注

42文章

1830瀏覽量

90961 -

GaN

+關注

關注

19文章

2051瀏覽量

74951

原文標題:晶體管級異質集成技術及其典型應用

文章出處:【微信號:DT-Semiconductor,微信公眾號:DT半導體】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

在特殊類型晶體管的時候如何分析?

晶體管參數測量技術報告

概述晶體管

什么是GaN透明晶體管?

什么是晶體管 晶體管的分類及主要參數

什么是達林頓晶體管?

氮化鎵功率晶體管與Si SJMOS和SiC MOS晶體管對分分析哪個好?

不同類型的晶體管及其功能

大功率晶體管驅動電路的設計及其應用

晶體管級異質集成技術及其實用案例分析

晶體管級異質集成技術及其實用案例分析

評論