“GaAs邏輯電路仿真不收斂怎么辦?”

使用GaAs工藝設(shè)計過邏輯電路的人大概率都遇到過各種各樣奇奇怪怪的收斂性問題,比如一個+5V供電的電路竟然出現(xiàn)了幾十上百伏的節(jié)點電壓;又比如一個反相器Transient仿真總是提示Timestep too small。

01

一些典型的不收斂示例

(1)DC仿真時出現(xiàn)明顯異常的電壓或者電流,作者之前在WIN的諸多工藝上都遇到過節(jié)點電壓超出電源電壓的情況,比如+5V供電,輸出電壓達到了幾十上百伏。

臨時又找不到合適的配圖了……

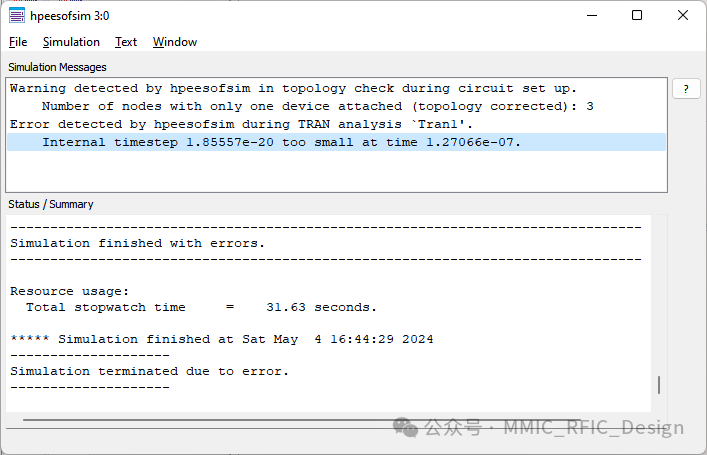

(2)Transient仿真時提示“Internal timestep too small”,如下圖所示:

02

不收斂原因分析

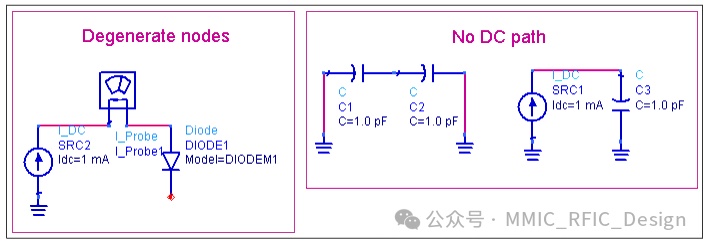

(1)最常見的原因還是在人,例如懸空的節(jié)點可能被仿真器自動移除,或者你的電路根本沒有直流回路,DC仿真自然無法收斂:

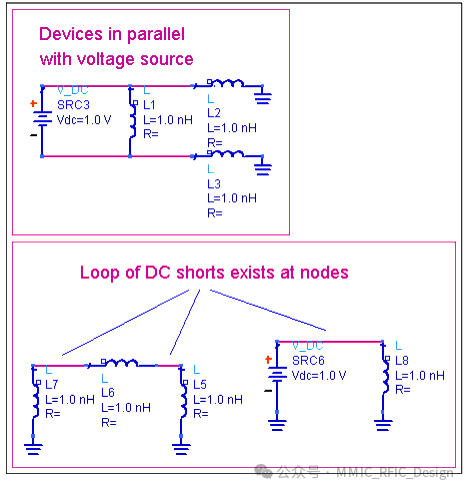

再比如電壓源不能與理想電感并聯(lián):

還有一些不可能成立(無解)的電路:電壓源不能并聯(lián)、電流源不能串聯(lián)。

或者設(shè)計的參數(shù)不合理,工作電壓超出了模型的有效范圍。

(2)第二常見的原因在于模型,GaAs pHEMT工藝的PDK大多是代工廠與Keysight合作開發(fā)的,至少是依賴了Keysight的技術(shù)支持,pHEMT器件模型大概率是ADS的EEHEMT模型,而模型參數(shù)又是針對RF電路優(yōu)化的,用來進行S參數(shù)或者HB仿真的收斂性沒問題,反而DC或Transient仿真時收斂性就表現(xiàn)很差。又比如說一些晶體管模型針對放大器應(yīng)用做了優(yōu)化,在合理的偏置點下仿真精度較高,但在接近夾斷的甚至低于夾斷電壓的柵壓偏置下仿真精度較差。

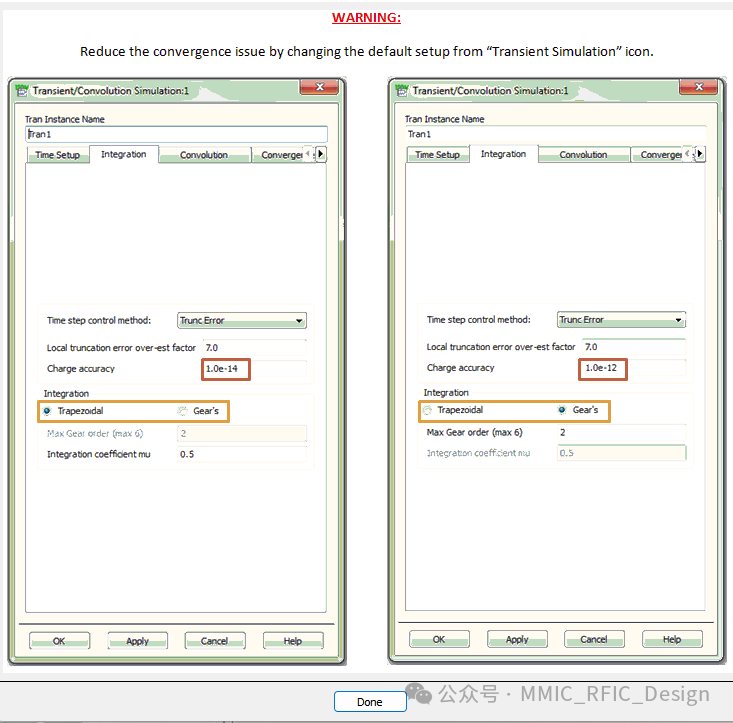

(3)仿真器參數(shù)設(shè)置不合理,通常是仿真精度要求太高,誤差太大時就容易出現(xiàn)不收斂的情況。

前面所述的EEHEMT模型并不局限于哪一家代工廠,很多家工廠的PDK都有類似的問題,尤其是在進行Transient仿真時,需要對電壓或者電流的時域波形進行數(shù)值積分運算,而數(shù)值積分極容易因誤差太大而導(dǎo)致不收斂。作為典型的GaAs代工廠代表,WIN給出的Transient收斂性改善建議是把積分算法由默認(rèn)的Trapezoidal(梯形法)改為Gear's(預(yù)測校正法),同時把電荷精度由默認(rèn)值1.0e-14改為1.0e-12。

ADS的help文檔中有一段話是這樣寫的:

Like SPICE, this simulator uses the trapezoidal integration method described by the following equation as the default method for calculating derivatives at each time step t in the simulation. 【公式1】 For most circuits, this method will succeed. For those that do not, the simulator also supports Gear's backward difference method: 【公式2】 In this equation, the index k is called the order of the integration. For most circuits, Gear's method is no more accurate than the default trapezoidal integration technique. However, if a circuit analysis fails to converge, Gear's method may succeed where trapezoidal integration fails. In particular, oscillator circuits and any circuit that is characterized by stiff state equations may benefit from Gear's method. For a discussion of Gear's method and stiff state equations, refer to Chua and Lin, Computer-Aided Analysis of Electronic Circuits: Algorithms and Computation Techniques, Prentice-Hall, 1975.

【公式1】

【公式2】

最后一段的大意是:對大多數(shù)電路而言,Gear's積分法并不比默認(rèn)的Trapezoidal 積分法精度更高,但是如果一個電路用Trapezoidal積分法仿真不收斂,那么改用Gear's積分法也許能收斂。特別地,對于振蕩電路以及類似具有剛態(tài)方程的電路時采用Gear's積分法可能會更有利。

然而上述設(shè)置僅僅是對Transient仿真的收斂性有一定改善,并不能保證仿真一定能收斂。

03

個人方法

對于一些簡單的GaAs邏輯電路(例如基礎(chǔ)門電路,或者3-8譯碼器規(guī)模以下的組合邏輯),通過減小仿真步長、更換積分方法、修改仿真精度等方法基本上都可以解決。但是功能稍微更復(fù)雜的觸發(fā)器、鎖存器等很大可能還是不能收斂,例如幅相控制多功能芯片里需要用到的串并轉(zhuǎn)換電路,其邏輯門的規(guī)模可能達到500左右的量級,要想跑通Transient仿真是非常困難的。

根據(jù)作者的經(jīng)驗,Cadence的Transient仿真器性能比ADS好很多,同樣的電路用ADS仿真不收斂,改用Cadence就可能收斂;也可能是雖然用ADS仿真能收斂但是非常慢,而用Cadence仿真的速度就能快上幾十倍。奈何絕大部分GaAs工藝的PDK的仿真模型僅支持ADS,Cadence版的PDK通常只支持LVS/DRC而沒有電路仿真模型。

基于上述現(xiàn)實痛點,作者只能另辟蹊徑。通過觀察,作者發(fā)現(xiàn),絕大部分仿真不收斂都發(fā)生在數(shù)據(jù)或始終跳變的時刻,這正是電路中的電壓或者電流波形急劇變化的時候,極可能進入器件模型的不連續(xù)區(qū)間。是否可以自己建立一個簡化的模型,僅模擬晶體管開關(guān)的結(jié)果,而去不關(guān)心晶體管開關(guān)切換這一瞬時的精確波形,從而改善仿真的收斂性?

答案是肯定的,我用Verilog-A描述了一個簡單的pHEMT模型,只包含三個特性:導(dǎo)通閾值、柵極的寄生肖特基二極管、導(dǎo)通電阻。有了這三個基本的要素,就可以模擬晶體管的開關(guān)特性和柵極漏電。而且為了確保電壓、電流變化的連續(xù)性,我只用最基本的連續(xù)函數(shù)去描述其IV曲線。

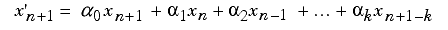

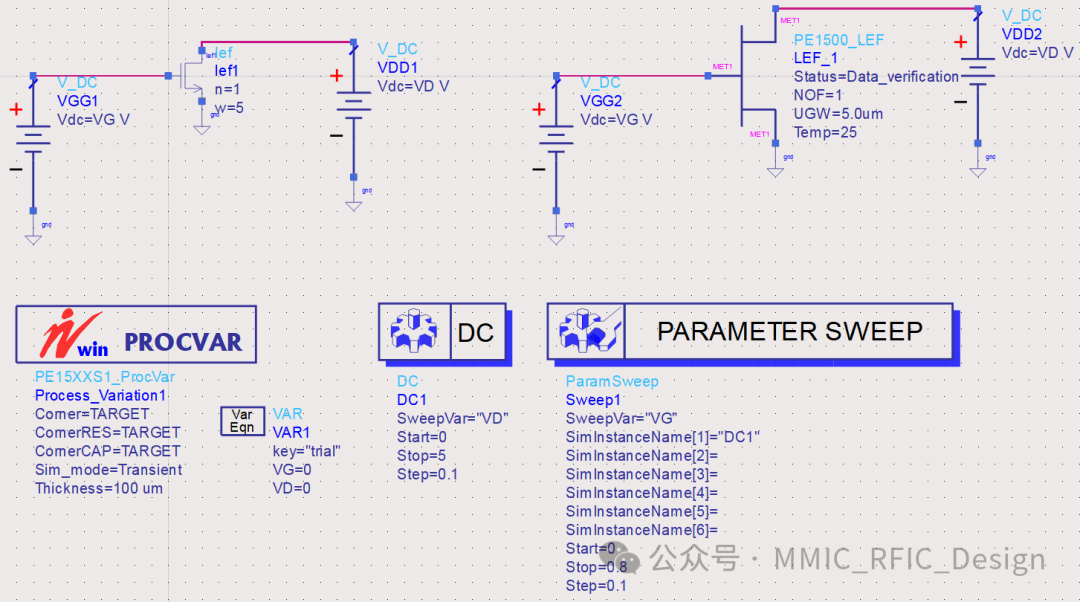

而且,由于上述晶體管模型過于簡陋,它甚至完全不能很好地擬合PDK模型的DCIV:

(上圖左側(cè)是自定義簡化模型,右側(cè)是PDK模型)

(上側(cè)兩幅圖是自定義簡化模型的DCIV曲線,下側(cè)兩幅圖是PDK模型的DCIV曲線)

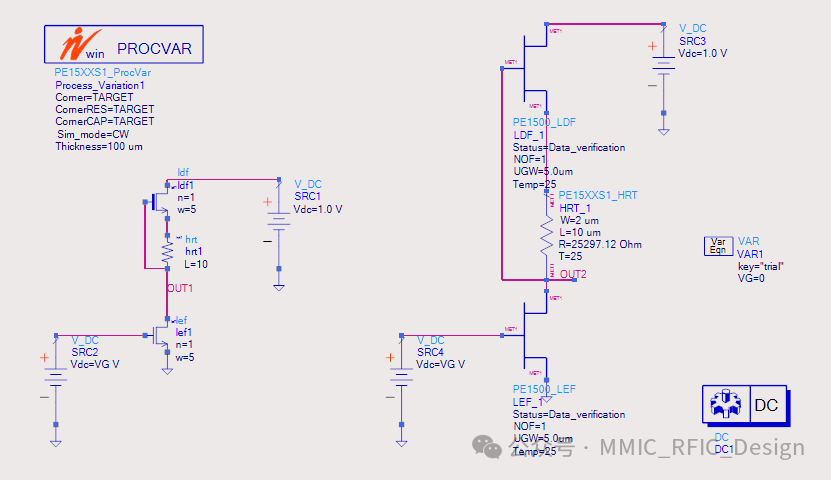

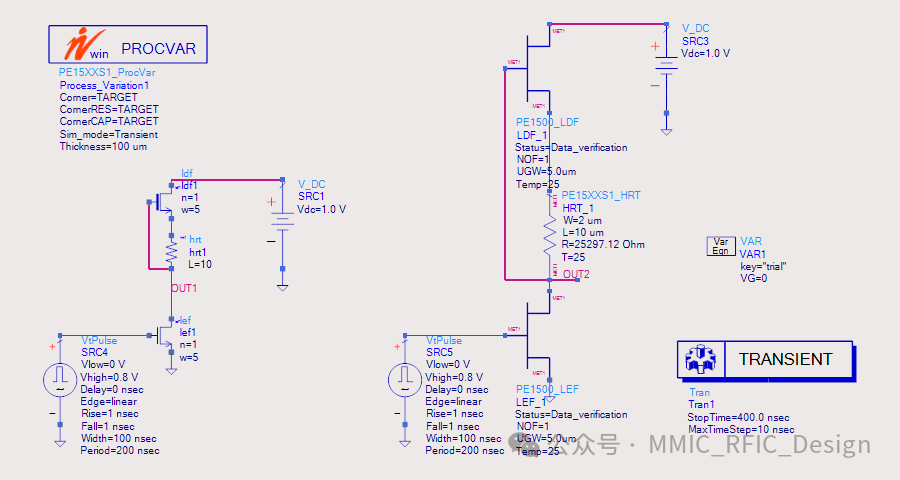

但是,前面說過了,我并不關(guān)心它自身有多精準(zhǔn),我更關(guān)心作為邏輯門時它能否較好地模擬其開關(guān)跳變的結(jié)果。因此上述自定義晶體管模型的參數(shù)我并不是用原始PDK晶體管模型的DCIV曲線去擬合的,而是讓它在一個完整的門電路中、在一個特定的偏置條件下去擬合PDK模型結(jié)果,例如下面這個最基礎(chǔ)的非門(反相器):

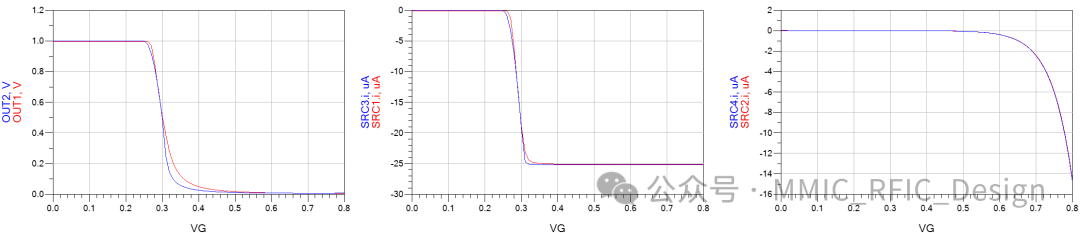

上面是DC仿真結(jié)果,下面是Transient仿真結(jié)果。可以看到自定義模型能夠較為精確地模擬非門的輸入邏輯閾值、輸出電壓、柵極電流、漏極電流。

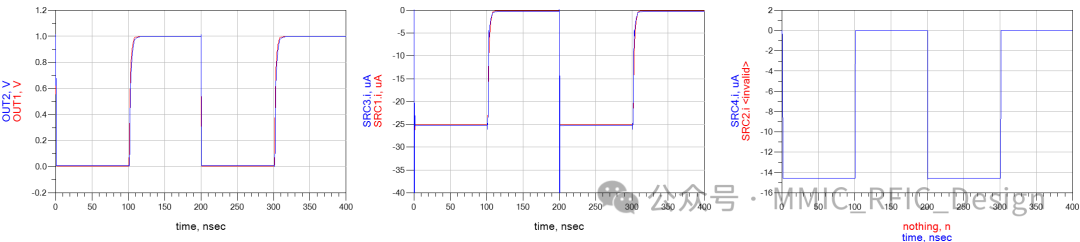

從Transient仿真結(jié)果可以清楚地看到自定義模型能夠很好的擬合PDK模型在非門中的瞬態(tài)波形,正如前文所述,波形跳變的邊沿被刻意平滑掉了,沒有顯著的尖峰,但是電壓電流平穩(wěn)后的波形都能完美重合。

基于類似的思想,我把電阻、電容、二極管、D-mode邏輯管和E-mode邏輯管的模型都做了簡化并與原PDK模型進行擬合。這樣,諸如串并轉(zhuǎn)換這類對于GaAs來說算是較大規(guī)模的邏輯電路仿真也幾乎再也沒有遇到過不收斂的問題。

所以總結(jié)一下,對于比較復(fù)雜的GaAs邏輯電路,我的設(shè)計思路是:

使用PDK模型設(shè)計每個基本的邏輯門,確保每個基本的邏輯門在所有Corner、-55℃~+125℃溫度下都能夠正常工作,這種規(guī)模的邏輯電路基本上不會有太大的收斂性問題;

開始由基礎(chǔ)的邏輯門構(gòu)建更復(fù)雜的邏輯單元,比如鎖存器、觸發(fā)器,只要沒有收斂性問題就繼續(xù)使用PDK模型進行設(shè)計;

當(dāng)邏輯復(fù)雜度達到一定規(guī)模后開始出現(xiàn)收斂性問題(比如由觸發(fā)器構(gòu)建移位寄存器時大概率就不容易收斂了),這時候更換成自定義模型(只對TARGET Corner@25℃進行參數(shù)擬合),并且對比更換前后的DC仿真狀態(tài)是否一致,主要就是看靜態(tài)電流和靜態(tài)電壓;

使用自定義的模型完成全部邏輯電路的時序功能驗證,最后再更換為PDK模型檢驗一下完整電路的DC靜態(tài)電壓和靜態(tài)電流是否吻合。

上述自定義模型僅在TARGET Corner@25℃進行參數(shù)擬合,僅僅是為了驗證整體邏輯功能的正確性,無法全面反映全部邏輯電路在任意Corner/溫度下的是否都能正常工作。當(dāng)然,硬要針對每一個Corner、每一個溫度極限都去進行參數(shù)擬合,再分別驗證整體邏輯功能此時是否正常也是可以的,但實在是太麻煩了。

基于以上設(shè)計思路,作者已在WIN的PD25XX、PE15XX工藝上完成過多款串并轉(zhuǎn)換與開關(guān)驅(qū)動電路的開發(fā),經(jīng)實測三溫邏輯功能均正常,各項指標(biāo)符合預(yù)期。

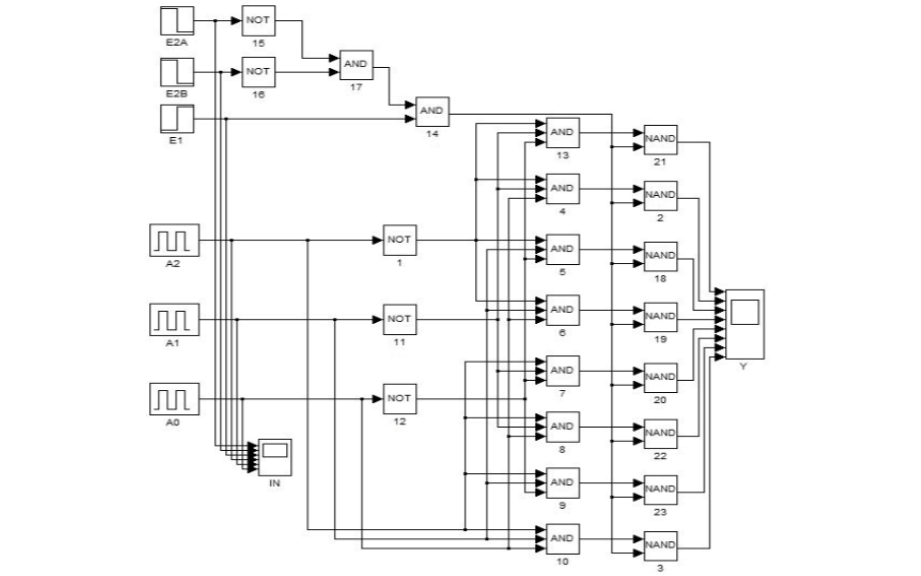

下面給出一個串并轉(zhuǎn)換電路的仿真示例:

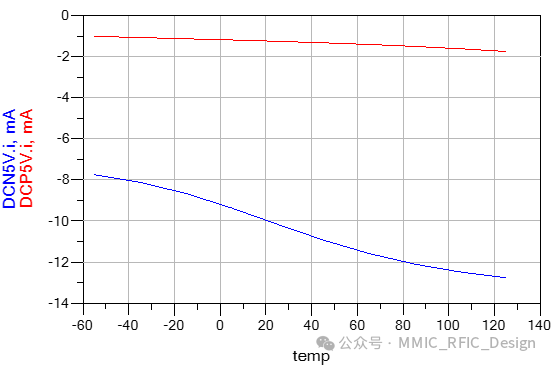

使用原始PDK模型仿真的工作電流隨溫度變化的曲線是:

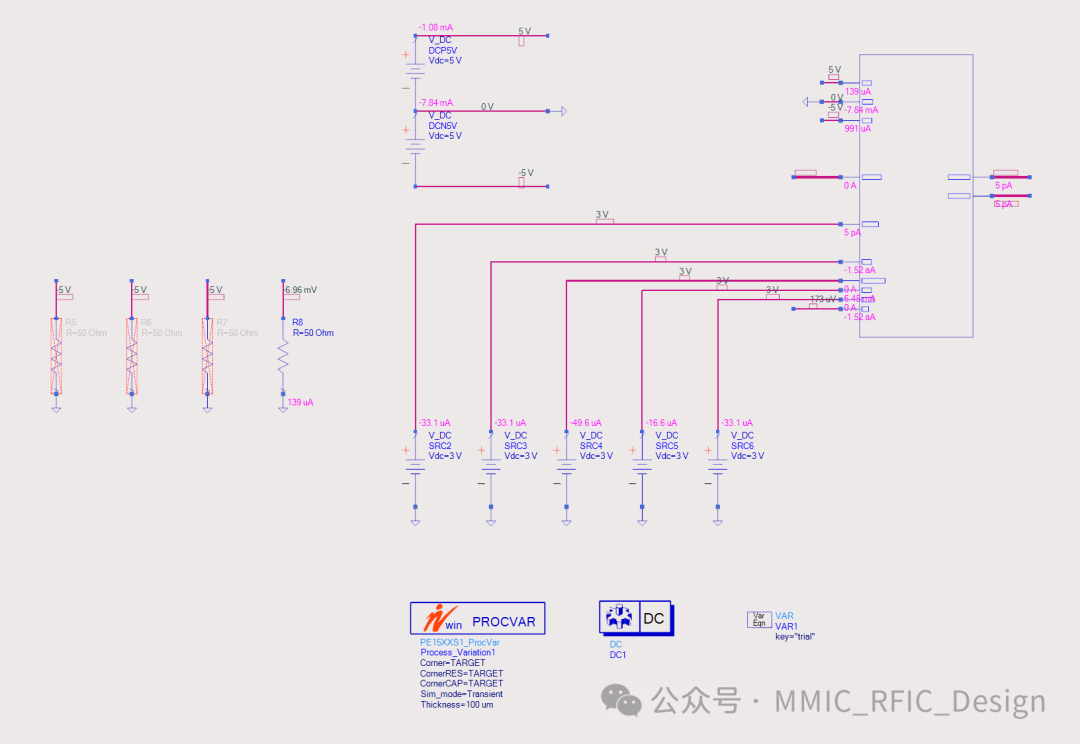

而更換為自定義簡化模型前后,在TARGET@25℃這一個點處,DC仿真得到的靜態(tài)電流對比為:

?WIN

?+5V電流:1.31mA

?-5V電流:10.2mA

?自定義簡化模型

?+5V電流:1.31mA ?-5V電流:10.3mA

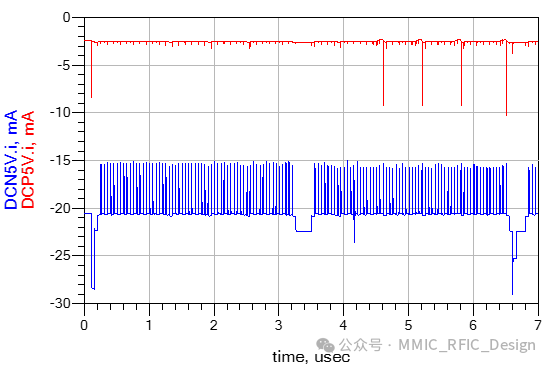

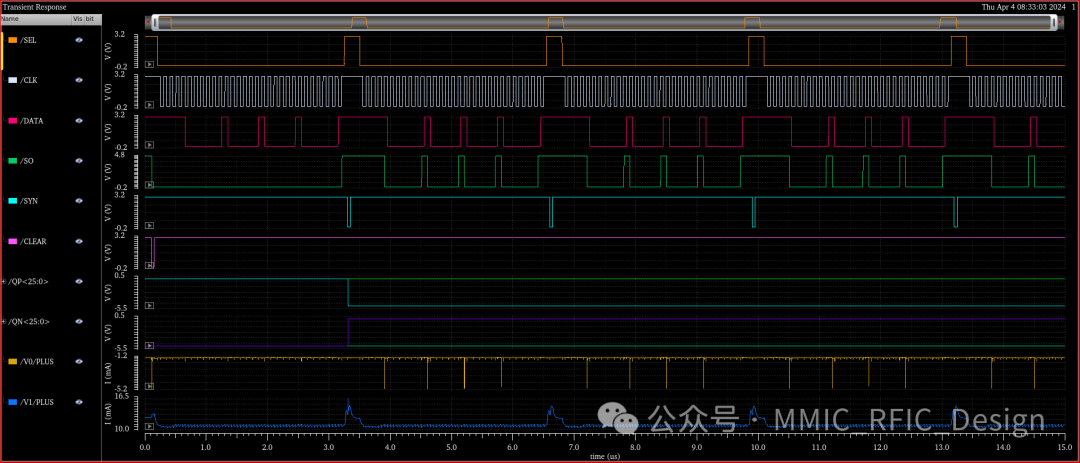

使用PDK模型Transient仿真無法收斂,使用自定義模型Transient仿真的+5V和-5V電源瞬態(tài)電流波形:

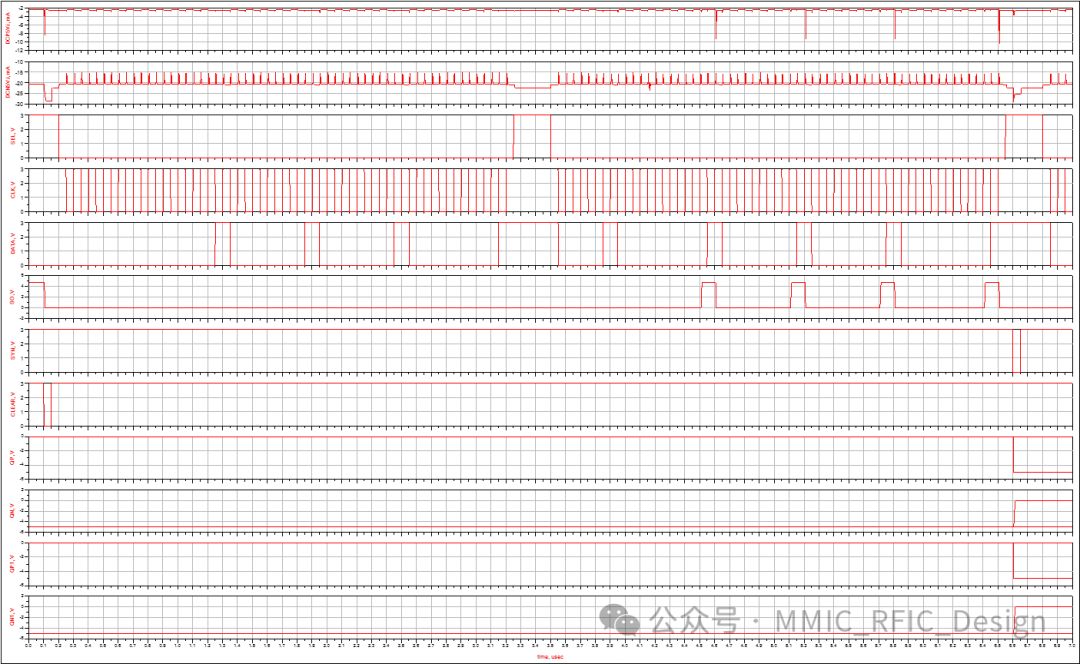

完整串并轉(zhuǎn)換邏輯電路整體的仿真波形:

最后,使用自定義Verilog-A模型的另一個好處是,Cadence環(huán)境下也能進行設(shè)計和仿真了。

至于仿真速度上,同樣的Verilog-A自定義模型,同一臺電腦、同一個CentOS系統(tǒng)環(huán)境:在ADS下根據(jù)激勵條件不同,Transient仿真大概需要40min~80min不等;在Cadence下根據(jù)激勵條件不同,Transient仿真大概需要30s~60s不等。這兩者在速度上的天壤之別讀者自行體會吧!

審核編輯:劉清

-

邏輯電路

+關(guān)注

關(guān)注

13文章

494瀏覽量

42609 -

反相器

+關(guān)注

關(guān)注

6文章

311瀏覽量

43289 -

仿真器

+關(guān)注

關(guān)注

14文章

1017瀏覽量

83721 -

電源電壓

+關(guān)注

關(guān)注

2文章

989瀏覽量

23969 -

ADS仿真

+關(guān)注

關(guān)注

0文章

71瀏覽量

10434 -

GaAs

+關(guān)注

關(guān)注

2文章

510瀏覽量

22982

原文標(biāo)題:經(jīng)驗分享——GaAs邏輯電路ADS仿真不收斂怎么辦?

文章出處:【微信號:芯片設(shè)計之路,微信公眾號:芯片設(shè)計之路】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

相關(guān)推薦

求大佬幫忙解答使用tl494設(shè)計的開關(guān)型電源設(shè)計輸出結(jié)果不收斂的問題

搭了一個臨界模式的PFC電路,但是仿真顯示不收斂,是哪里的問題?

請問ada4938仿真不收斂是否是我的電路圖連接的問題

multisim仿真錯誤不收斂

為什么s參數(shù)不收斂?有哪些方式導(dǎo)入s參數(shù)使得其仿真能夠收斂?

Multisim的時序邏輯電路設(shè)計仿真

組合邏輯電路和時序邏輯電路比較_組合邏輯電路和時序邏輯電路有什么區(qū)別

使用Matlab實現(xiàn)組合邏輯電路的設(shè)計與仿真

Abaqus橡膠仿真不收斂問題的排查方法

MATLAB的數(shù)字邏輯電路Simulink仿真

Simulink數(shù)字邏輯電路的仿真

GaAs邏輯電路ADS仿真不收斂怎么辦?

GaAs邏輯電路ADS仿真不收斂怎么辦?

評論