最近要寫一個協議,所以再復習一次SPI。(存草稿太久了,再不發就忘了)

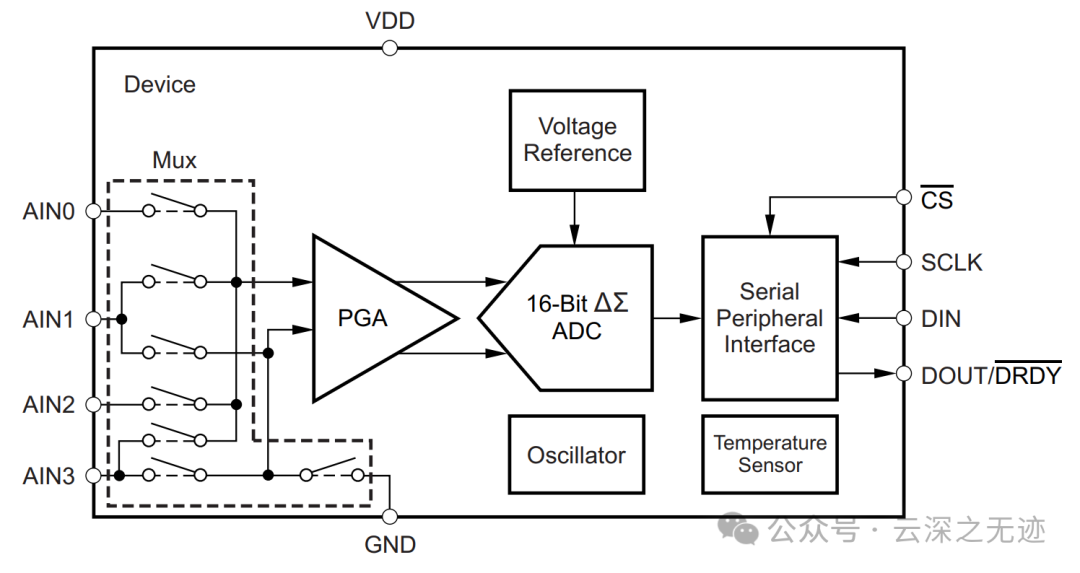

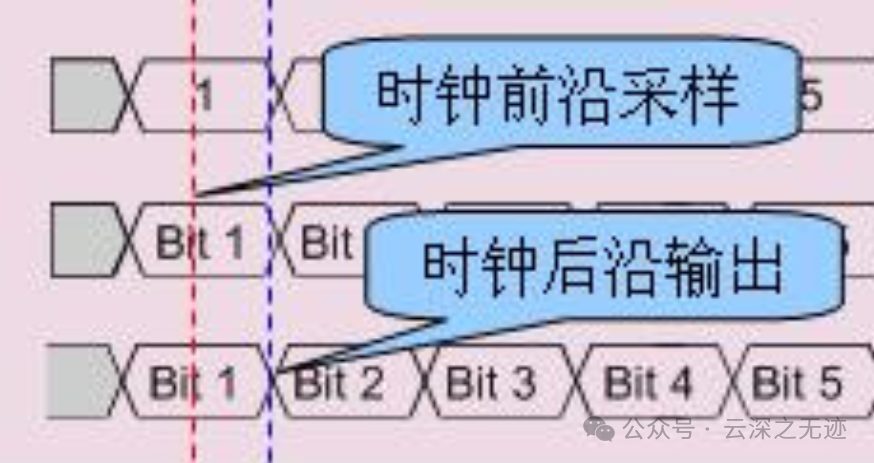

一開始先分析了SPI的協議特點,使用ADS1118這個器件作為承載物進行分析,后面用邏輯分析儀從位到字節進行解碼,最后使用TI給的demo移植到STM32平臺。

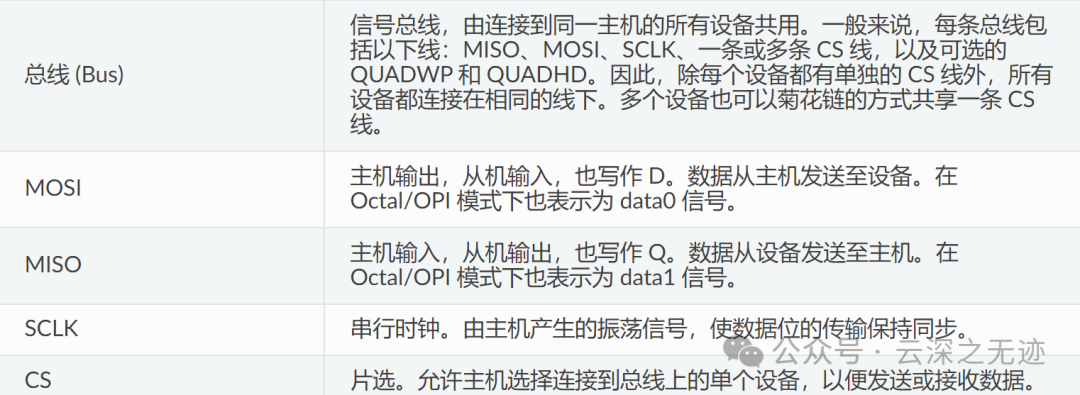

SPI是一個環形總線結構,由ss(cs)、sck、sdi、sdo構成,其時序其實很簡單,主要是在sck的控制下,兩個雙向移位寄存器進行數據交換。

上升沿發送、下降沿接收、高位先發送。

上升沿到來的時候,sdo上的電平將被發送到從設備的寄存器中。

下降沿到來的時候,sdi上的電平將被接收到主設備的寄存器中。 各家的名字可能不一樣,反正你就看傳輸方向就行。

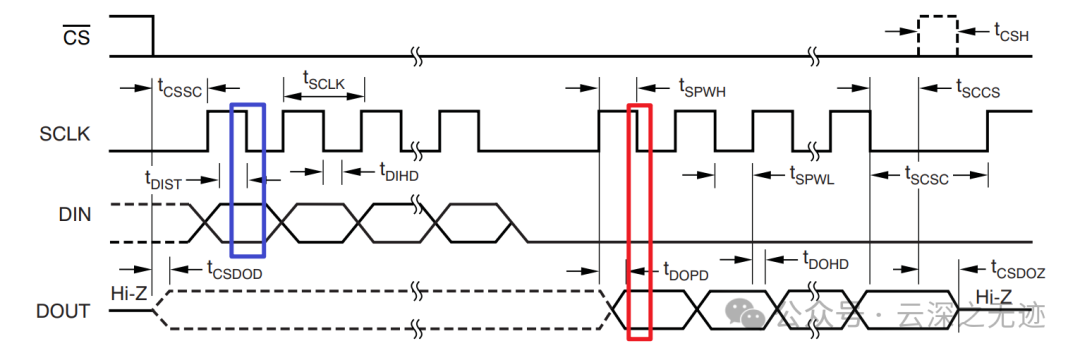

這個是時序圖,因為是雙向的傳輸,在主機發給從機這段時間,從機也是發數據的,但是相當于亂發無意義的:

另外:密封的菱形部分,注意要密封,表示數據有效,Valid Data這個詞也顯示了這點。

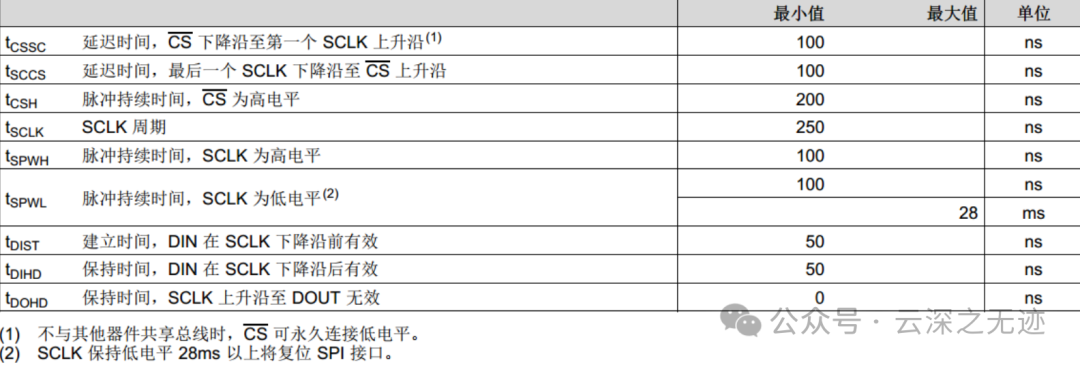

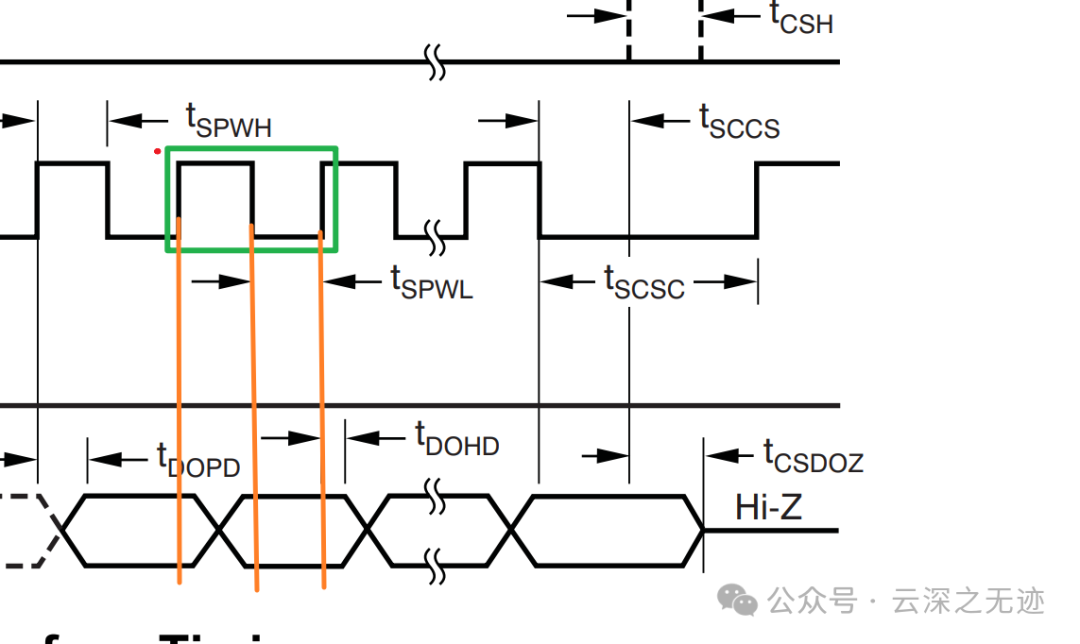

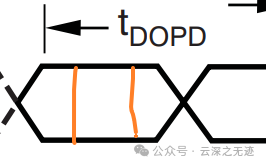

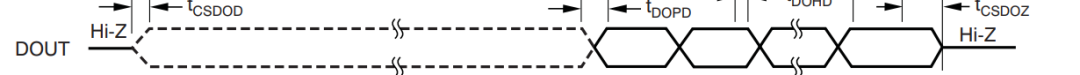

關于時間的標注,這也是個十分重要的信息,這些時間的標注表明了某些狀態所要維持的最短或最長時間。

因為器件的工作速度也是有限的,一般都跟不上主控芯片的速度,所以它們直接之間要有時序配合。

外部12MHz晶振,指令周期就是一個時鐘周期為(1/12MHz)us,所以至少確定了它執行一條指令的時間是us級別的。我們看到,以上給的時間參數全部是ns級別的,所以即便我們在程序里不加延時程序

10的-3次方

時序時間

專有的時鐘引腳上面是有施密特輸入的

這個名字好,DIN,然后數據鎖存在下降沿上:

GPIO開啟了引腳的弱上拉電阻:

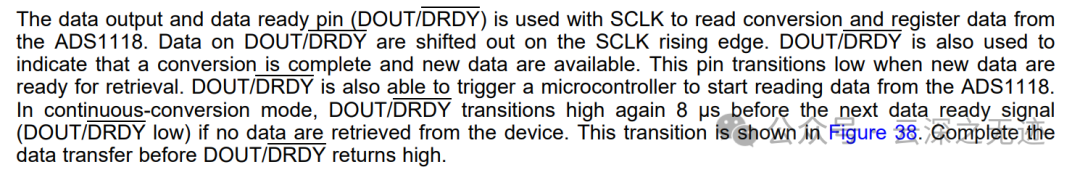

上升沿移出,下降沿準備:

這個是輸出的一個時鐘周期

這個樣子的意思是,數據有高有低,靠后的線是數據輸出,前面是數據準備。或者是被鎖定

不確定是不是所有的這樣。和上面的分析差不多

看一個連續輸出

在時序上面

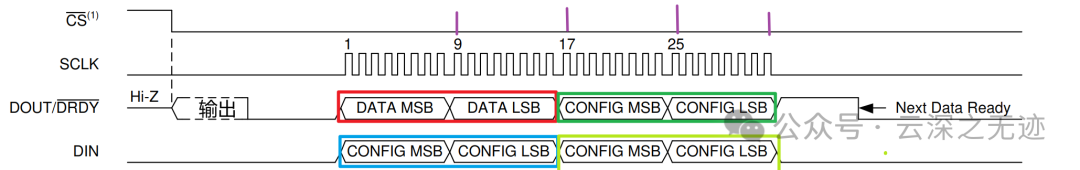

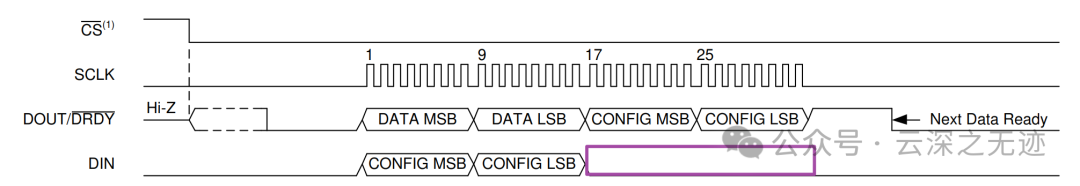

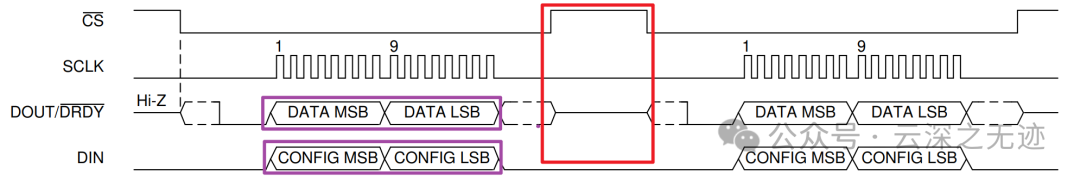

給MCU的數據中,一個大的時鐘周期由32個小周期組成,兩個字節來說明轉換的結果,也就是本身的數據,MSB在前。后面兩個是寄存器的回讀,這里我理解是把輸出的控制命令又回流一次。

2^16,兩個16位

DIN是MCU給器件的信息,MSB+LSB發一次,剩下二分之一如果你不變化,就可以讓這個DIN的引腳在后一個周期里面一直低或者高都可以。

你看嘛,就是這樣

還有16為輸出模式,可以交替的拉低CS來輸出

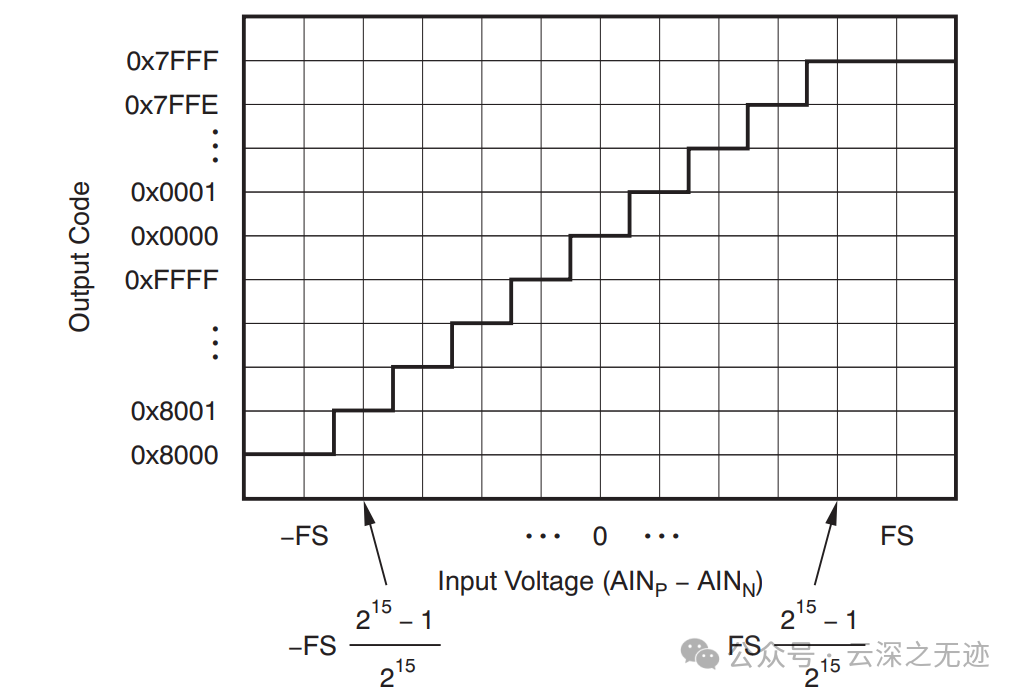

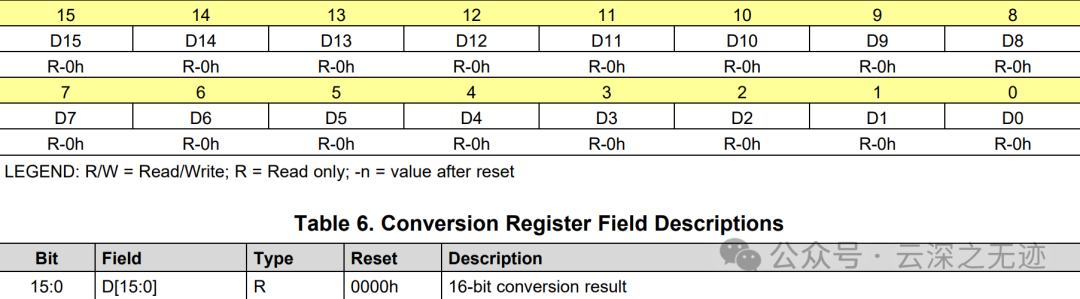

這個是輸出16位值的寄存器的樣子,0~15,上面每一位都是一個0或者1,一次16位。

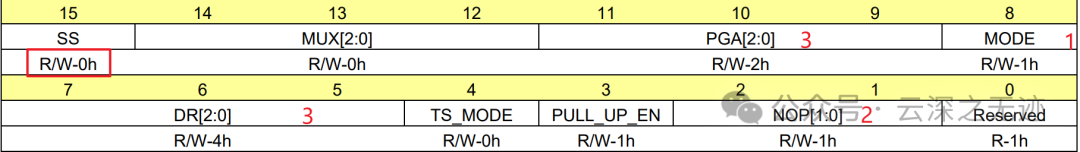

這個是配置的寄存器,從0開始寫,一直配好到15,組成一個16位的序列,發送。

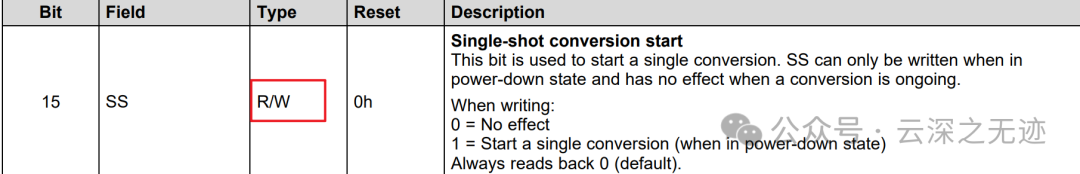

數據手冊里面的寫法是倒著來,先15,說這個寄存器的位置在15,名字叫SS,可以讀可以寫,重啟之后是0h,描述是斷電的時候設置一次,在轉換過程中換不了。

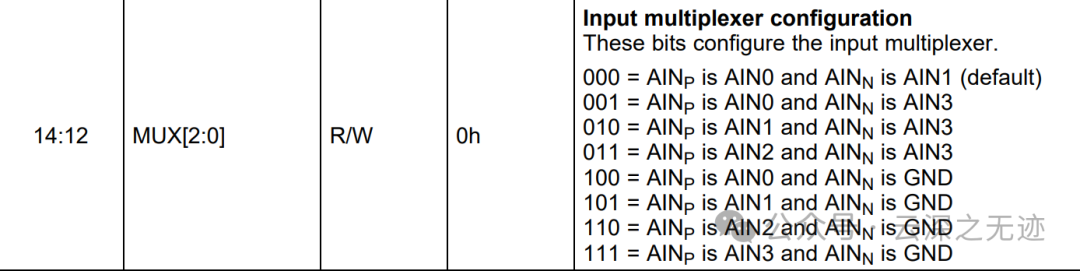

這個是3位,8種情況,對應個個采集方式:

如果對地的話,那就是差分

增益放大器:

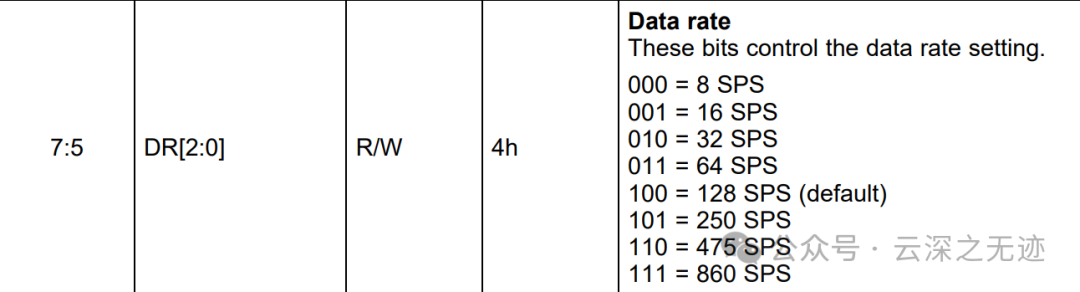

速率:

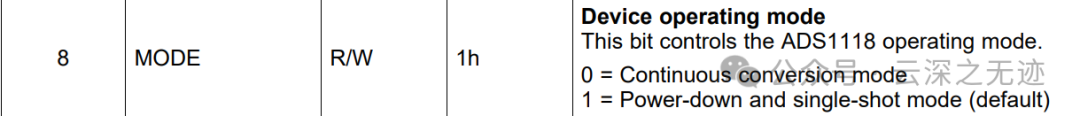

連續還是單發:

默認是單發

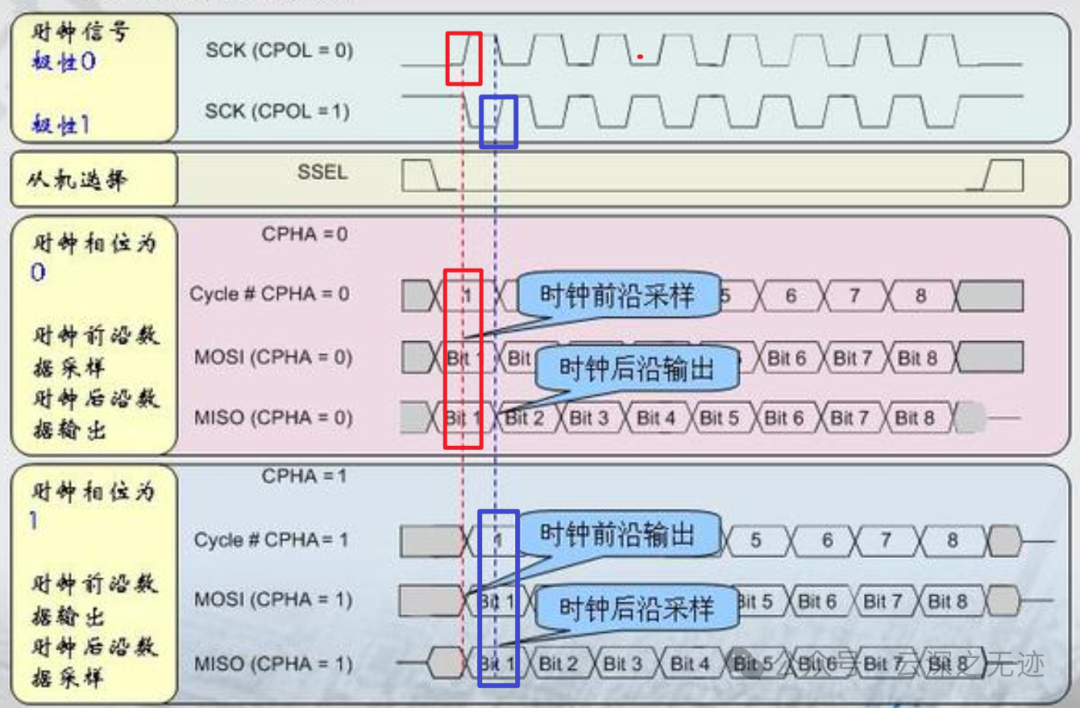

找了找就這個圖出現的次數最多。

OK

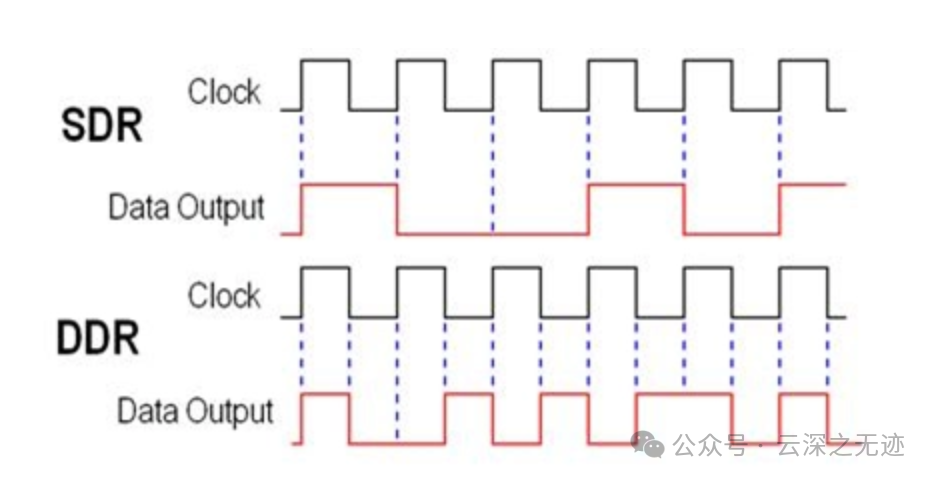

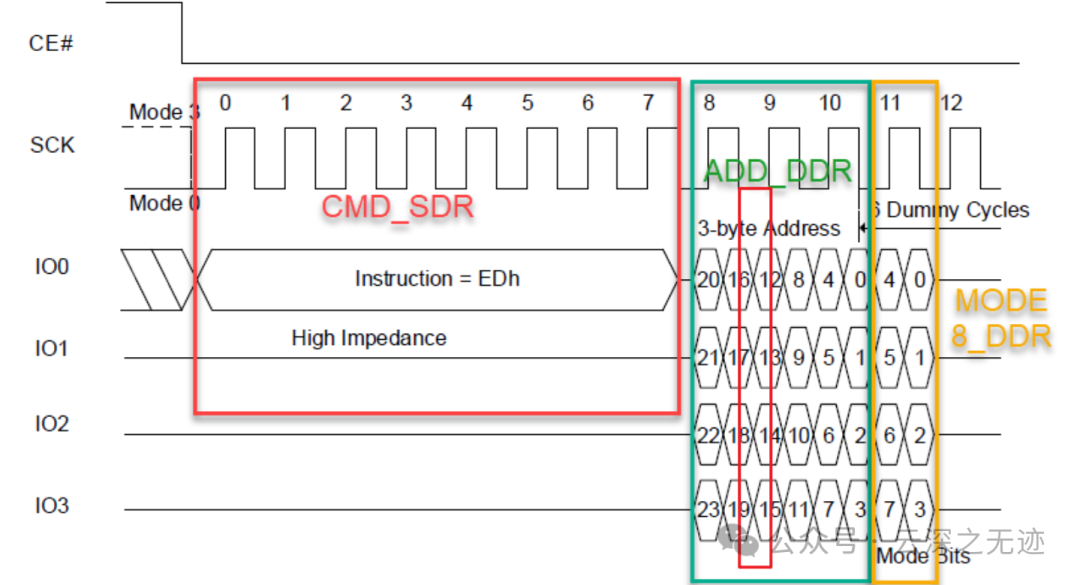

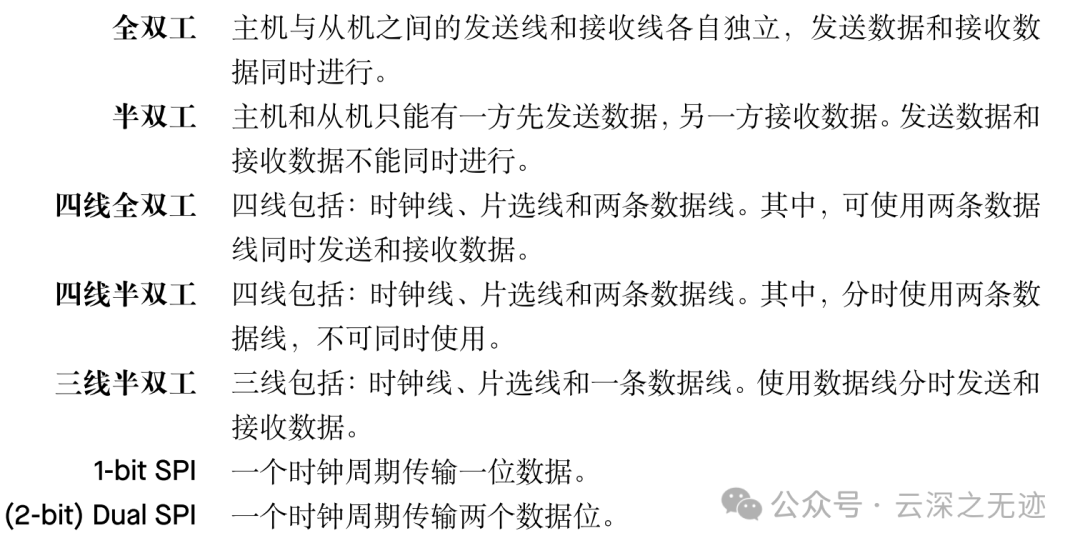

擴展SPI還增加了SDR(Single Data Rate)和DDR(Double Data Rate)兩種模式。在標準SPI 協議的SDR 模式下,只在SCK 的單邊沿進行數據傳輸,即一個SCK 時鐘只傳輸一位數據;而在DDR 模式下,會在SCK 的上升沿和下降沿都進行數據傳輸,即一個SCK 時鐘能傳輸兩位數據,傳輸速率提高一倍。

就是這樣

沒問題,可以看到時序圖內在CLK的上下沿,數據線上的電平確實是穩定的,可以讀取。

1. 2-bit Dual SPI模式

2-bit Dual SPI模式,也稱為Dual SPI模式,是標準SPI的一個變體,它使用兩條數據線(通常是MOSI和MISO)同時傳輸數據。在此模式下,數據在時鐘信號的上升沿和下降沿同時被發送和接收,使得數據吞吐量相比單線SPI翻倍。

它只是針對SPI Flash而言,不是針對所有SPI外設。對于SPI Flash,全雙工并不常用,因此擴展了mosi和miso的用法,讓它們工作在半雙工,用以加倍數據傳輸。也 就是對于Dual SPI Flash,可以發送一個命令字節進入dual mode,這樣mosi變成SIO0(serial io 0),mosi變成SIO1(serial io 1),這樣一個時鐘周期內就能傳輸2個bit數據,加倍了數據傳輸。

數據線:使用MOSI和MISO同時傳輸數據。

數據速率:相比于標準SPI,數據傳輸速率翻倍,因為它同時使用兩條線傳輸數據。

使用場景:適用于需要比標準SPI更高數據傳輸率但又不需要四線Quad SPI的場景。

2. DDR SPI模式

DDR SPI(雙數據率SPI)模式在每個時鐘周期的上升沿和下降沿都進行數據傳輸。這意味著在每個時鐘脈沖上,都可以發送或接收數據,從而有效地加倍了數據傳輸速率。這種模式通常用于高速數據采集系統中。

數據線:通常使用一條或多條數據線,但每個時鐘周期傳輸兩次數據。

數據速率:數據速率是標準SPI的兩倍,因為它在時鐘的上升沿和下降沿都傳輸數據。

使用場景:適合高性能需求的應用,如高速數據采集或高分辨率視頻傳輸。

區別 數據傳輸方式:Dual SPI利用兩條數據線在時鐘的每個邊沿傳輸數據;而DDR SPI可能只使用一條數據線,但在每個時鐘的上升沿和下降沿都傳輸數據。

復雜性:DDR SPI通常在實現上更復雜,因為它要求在時鐘的每個邊緣精確控制數據的采樣和輸出,這對時鐘同步提出了更高的要求。

效率:盡管兩者都提高了數據傳輸速率,但在具體實現和系統兼容性方面,它們各有優勢和局限。

如果你的設計對時鐘同步的要求極高,可能會更傾向于使用Dual SPI而不是DDR SPI,因為后者需要更精確的控制和可能導致的時鐘偏差問題。

相反,如果需要極高的數據傳輸效率,DDR SPI可能是更好的選擇。

HI-Z是什么?

補充:

Hi-Z是數字電路常見術語,指的是電路的一種輸出狀態,既不是高電平也不是低電平,如果高阻態再輸入下一級電路的話,對下級電路無任何影響,和沒接一樣,如果用萬用表測的話有可能是高電平也有可能是低電平,隨它后面接的東西定。高阻態: 高阻態的實質電路分析時高阻態可做開路理解。

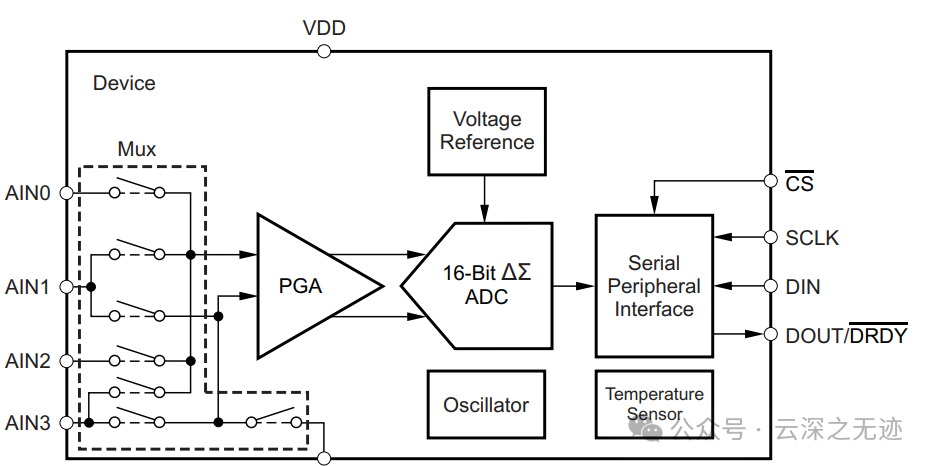

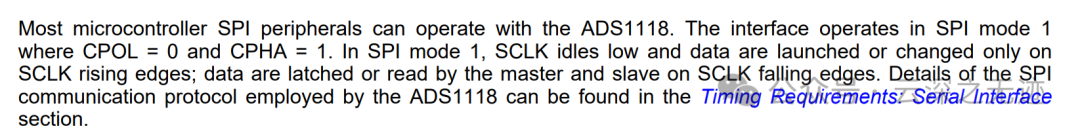

模式1:

上升沿改變,下降沿讀取。

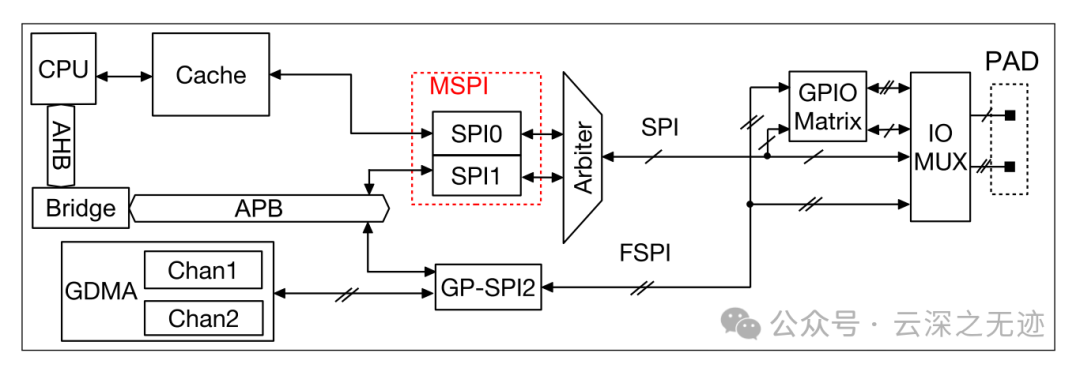

手邊還有一個ESP32-C3的單片機,這個是它的數據手冊,有三個SPI,或者是一個SPI配六個CS線。

外部焊盤,通過MUX,多路轉換到接口上面,可以走DMA或者Cache到CPU,等等,之后再說。

這個就更專業啦

SPI 主機驅動允許總線上連接多個設備(共享單個 ESP32-C3 SPI 外設)。每個設備僅由一個任務訪問時,驅動程序線程安全。反之,若多個任務嘗試訪問同一 SPI 設備,則驅動程序非線程安全。

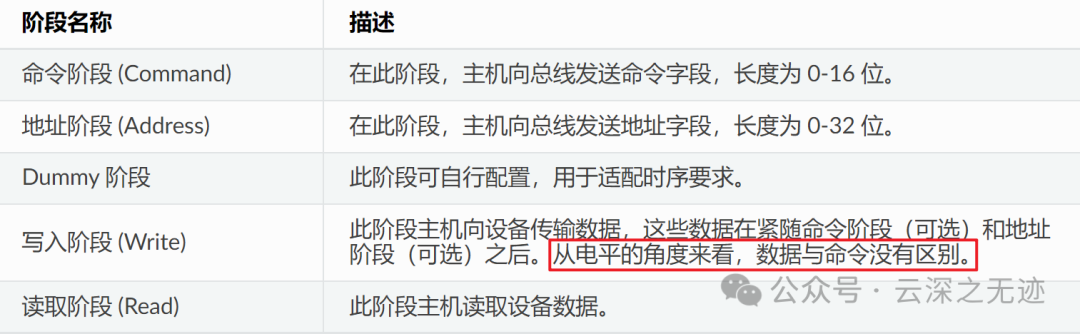

所有的SPI協議都可以分成這樣的步驟。

當傳輸事務數據等于或小于 32 位時,為數據分配一個緩沖區將是次優的選擇。

SPI 主機逐字節地將數據讀入和寫入內存。默認情況下,數據優先以最高有效位 (MSB) 發送,極少數情況下會優先使用最低有效位 (LSB)。如果需要發送一個小于 8 位的值,這些位應以 MSB 優先的方式寫入內存。

例如,如果需要發送 0b00010,則應將其寫成 uint8_t 變量,讀取長度設置為 5 位。此時,設備仍然會收到 8 位數據,并另有 3 個“隨機”位,所以讀取過程必須準確。

傳輸速度主要有以下三個限制因素:

傳輸事務間隔時間

SPI 時鐘頻率

緩存缺失的 SPI 函數,包括回調

影響大傳輸事務傳輸速度的主要參數是時鐘頻率。而多個小傳輸事務的傳輸速度主要由傳輸事務間隔時長決定。

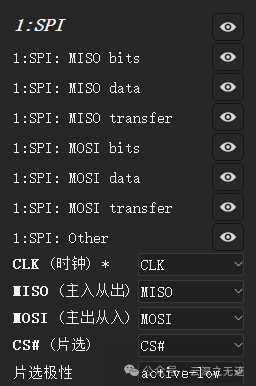

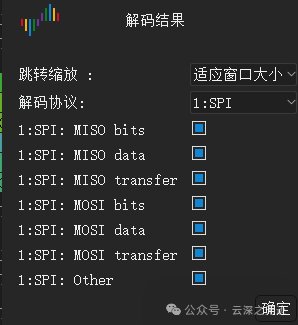

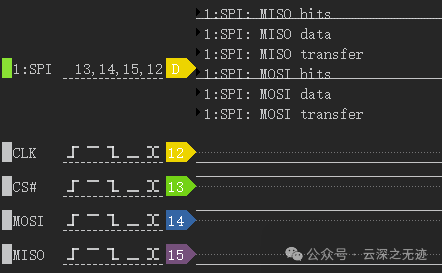

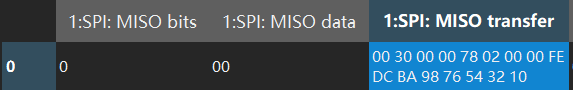

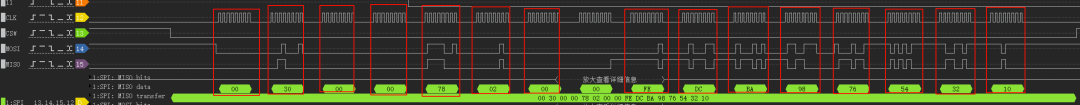

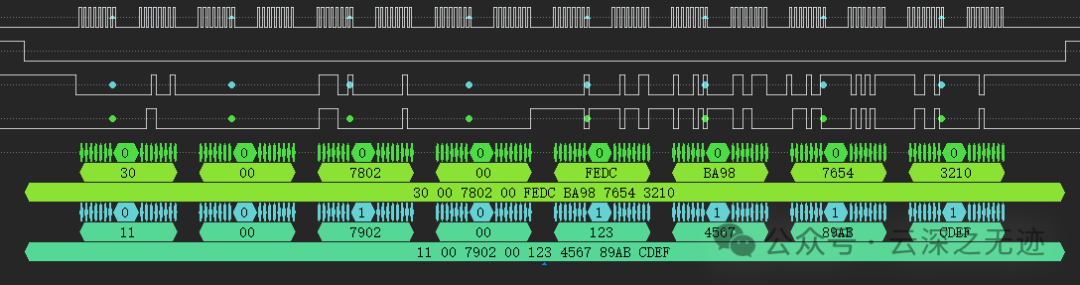

在捕捉的時候可以對 SPI 進行詳細設置

三個解碼層級的設置

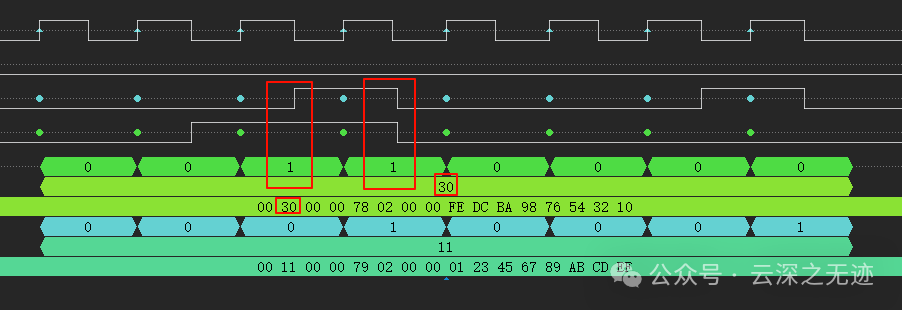

這里的解碼有幾個層級,首先是bit級別,就是0,1,接著是轉換,就是0,1拼成別的進制數據。還有就是轉換成數據。

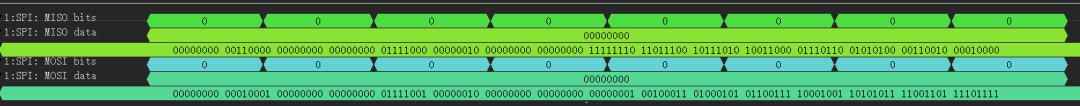

全是0

16進制的我喜歡使用

可以看到是一個不斷分組,組裝的過程

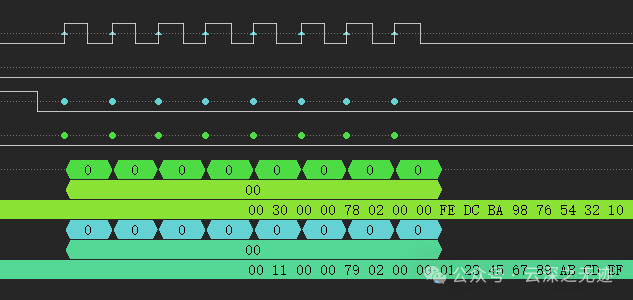

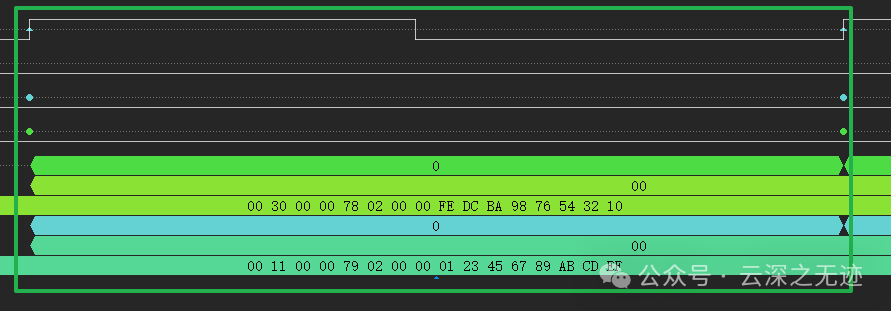

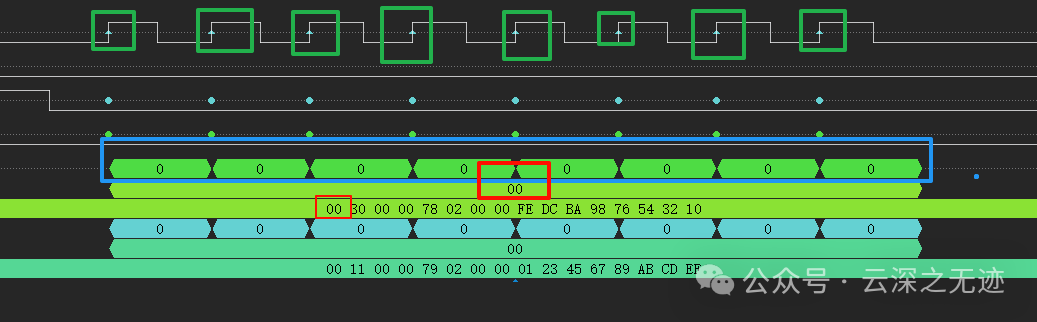

先看一個時鐘的變化

有八個上升沿,也就是8個0,也就是下面的00.是轉換的層級,8個字節是一位-00.

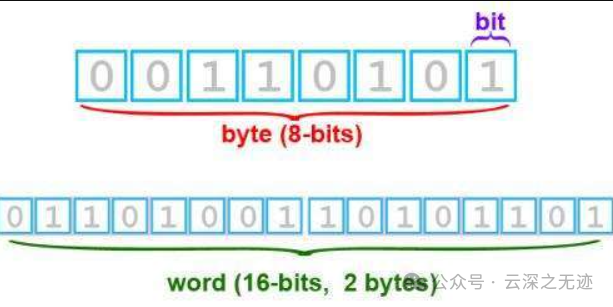

下面就是兩個字節變成了一word-16bit

第二個字節

大概就是這樣的解碼啦

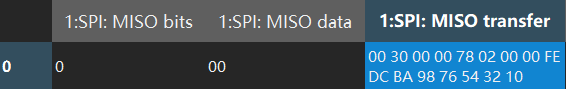

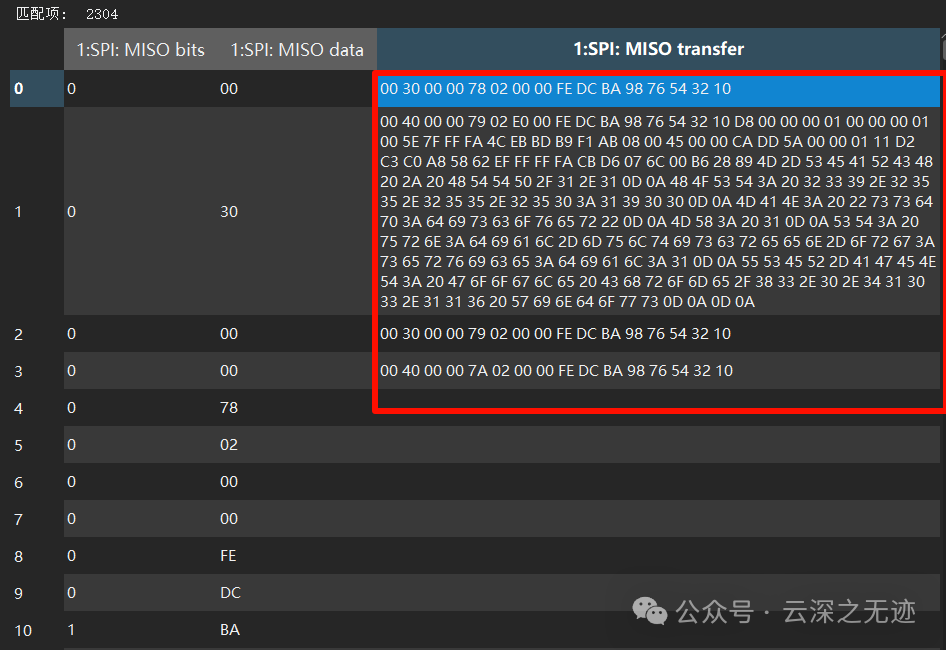

這就是解碼出來的第一個數據

前面是bit位,下一個是字節位,下一個是word位

按照16字節來解碼

因為可以自由的傳輸任意的字節數據,也可以在這里自己定義這個事情

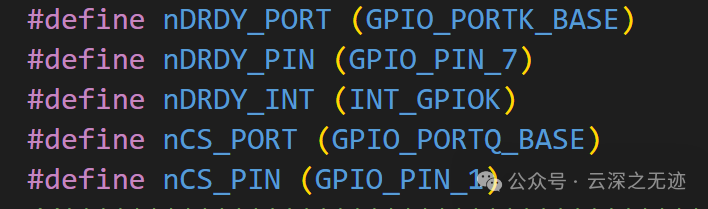

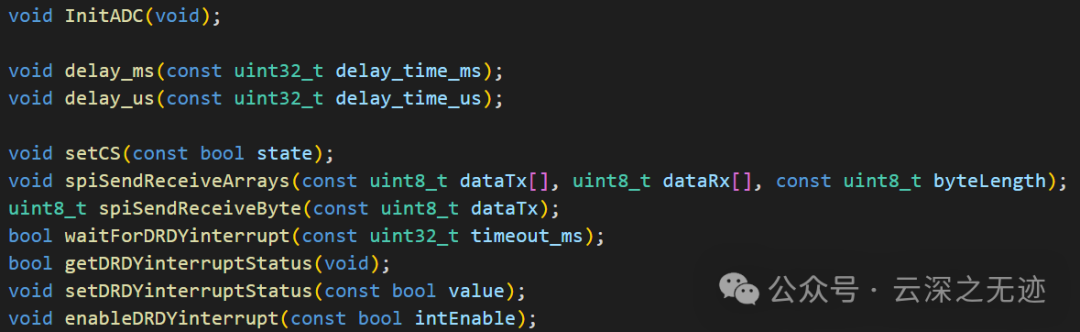

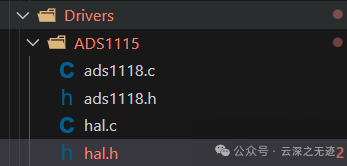

這里就開始移植,看這個TI的意思是隨便整,推薦自己實現SPI的接口:

下載最后一個

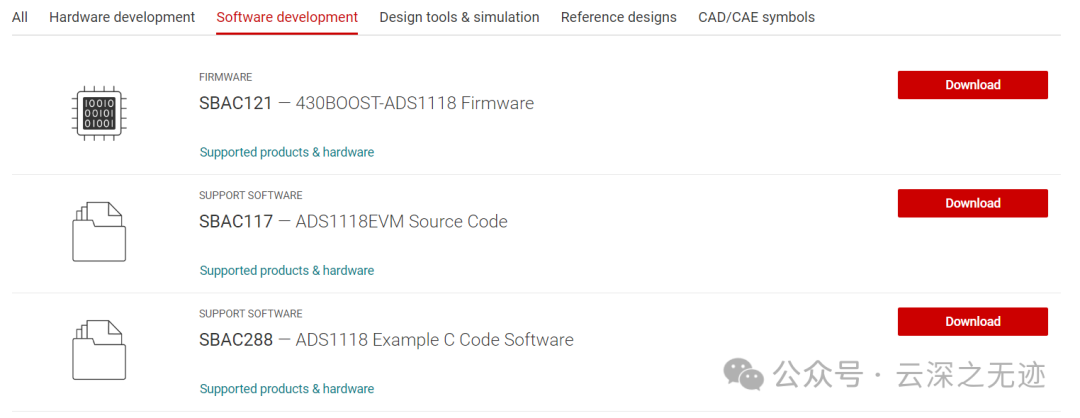

這里先說一下頭文件如何加

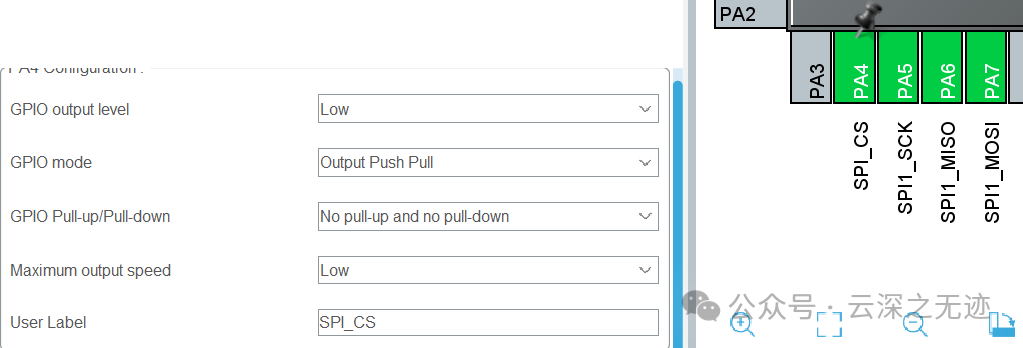

我們的工作是要在代碼里面實現STM32的SPI接口移植,然后在線測量所有的參數來更加詳細的學習SPI。

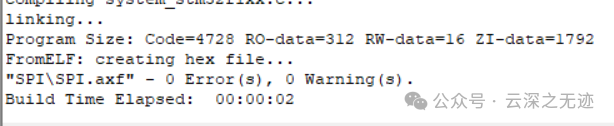

先看懂給的代碼,明白要干啥:

這些是TI的庫

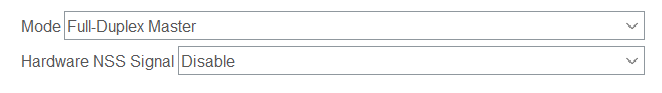

NSS管腳及我們熟知的片選信號,作為主設備NSS管腳為高電平,從設備NSS管腳為低電平。

當NSS管腳為低電平時,該spi設備被選中,可以和主設備進行通信。在stm32中,每個spi控制器的NSS信號引腳都具有兩種功能,即輸入和輸出。所謂的輸入就是NSS管腳的信號給自己。所謂的輸出就是將NSS的信號送出去,給從機。

對于NSS的輸入,又分為軟件輸入和硬件輸入。

軟件輸入: NSS分為內部管腳和外部管腳,通過設置spi_cr1寄存器的ssm位和ssi位都為1可以設置NSS管腳為軟件輸入模式且內部管腳提供的電平為高電平,其中SSM位為使能軟件輸入位。SSI位為設置內部管腳電平位。同理通過設置SSM和SSI位1和0則此時的NSS管腳為軟件輸入模式但內部管腳提供的電平為0。若從設備是一個其他的帶有spi接口的芯片,并不能選擇NSS管腳的方式,則可以有兩種辦法,一種是將NSS管腳直接接低電平。另一種就是通過主設備的任何一個gpio口去輸出低電平選中從設備。

硬件輸入: 主機接高電平,從機接低電平。

這樣

cs 自己換普通gpio,好像是自動的引腳有些問題

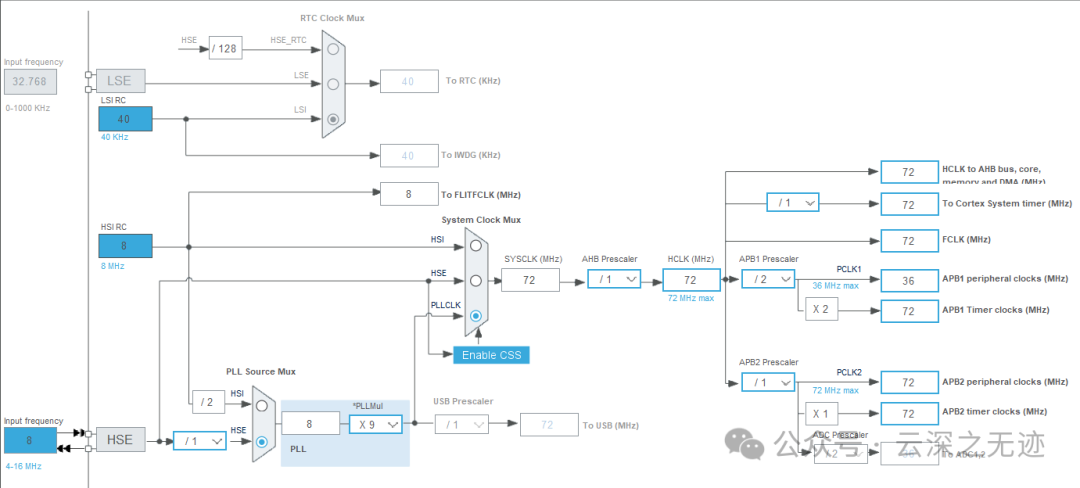

外部晶振為8MHz

1選擇外部時鐘HSE 8MHz

2PLL鎖相環倍頻9倍

3系統時鐘來源選擇為PLL

4設置APB1分頻器為 /2

5使能CSS監視時鐘

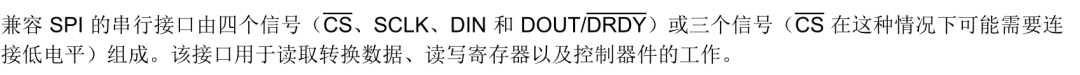

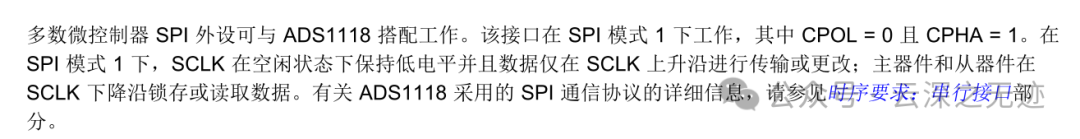

后來我找到了中文的數據手冊

這個地方 4 種模式選擇

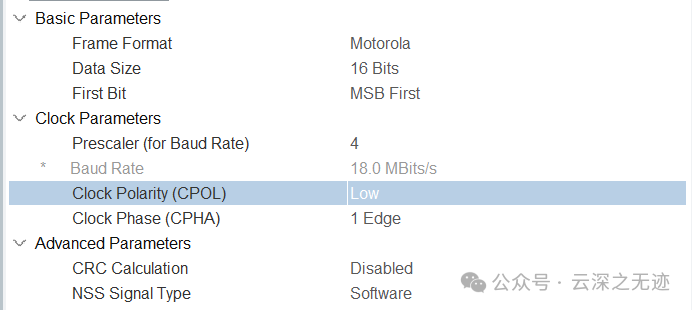

打開窗口

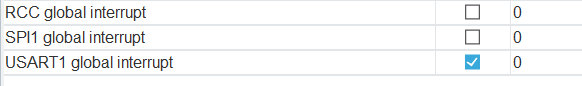

打開中斷

編譯 Ok

這個是TI硬件層的所有東西,一會兒就重寫

ti 的板子我用的少

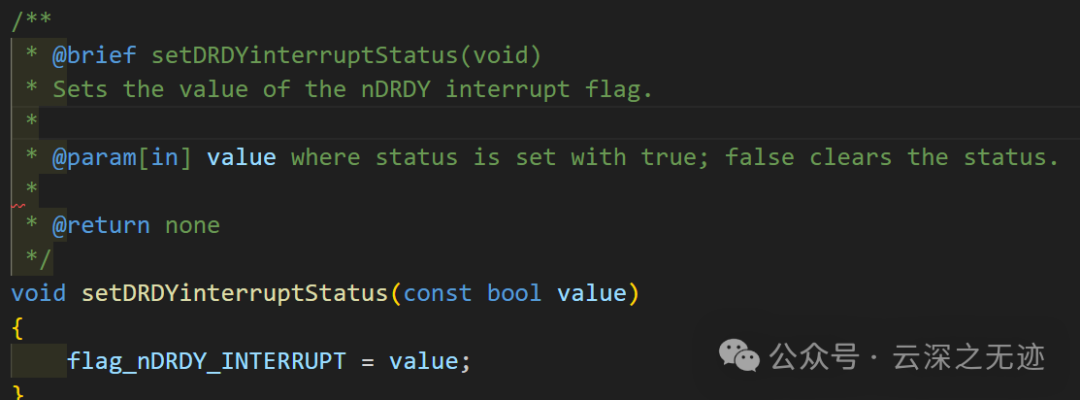

中斷狀態

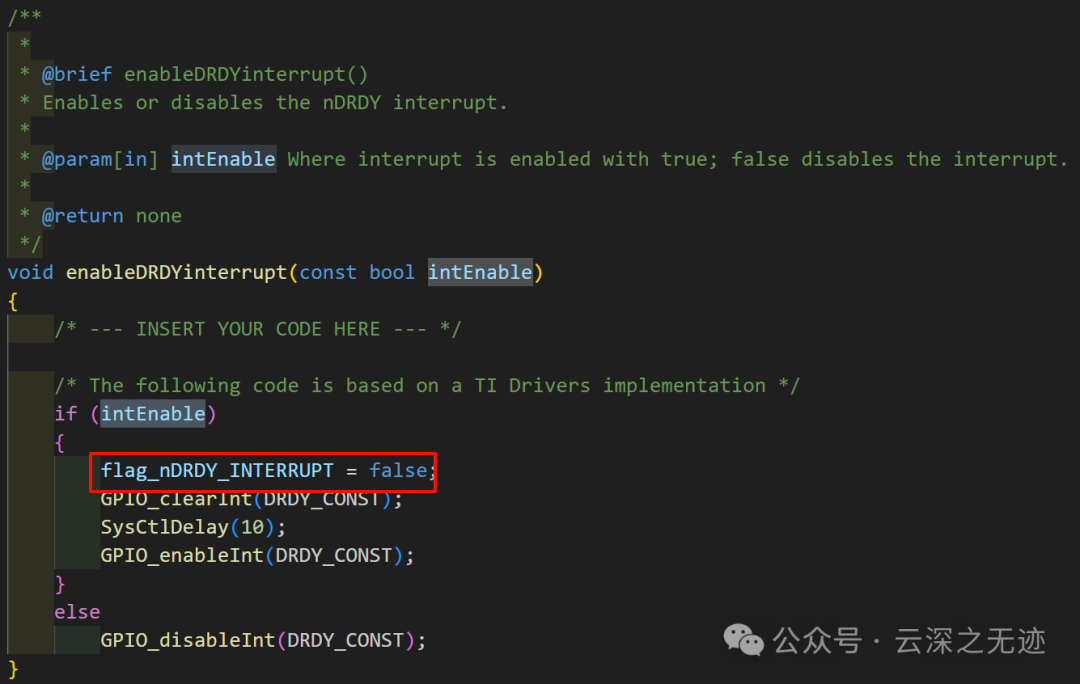

開啟中斷

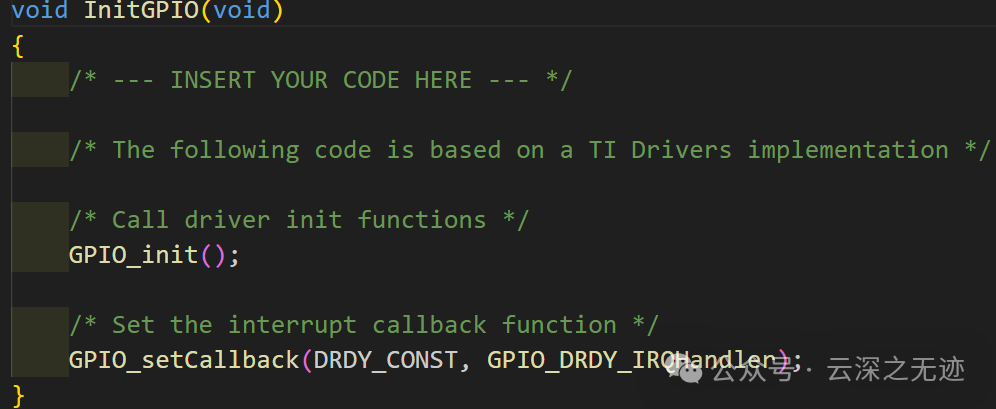

開啟中斷引腳

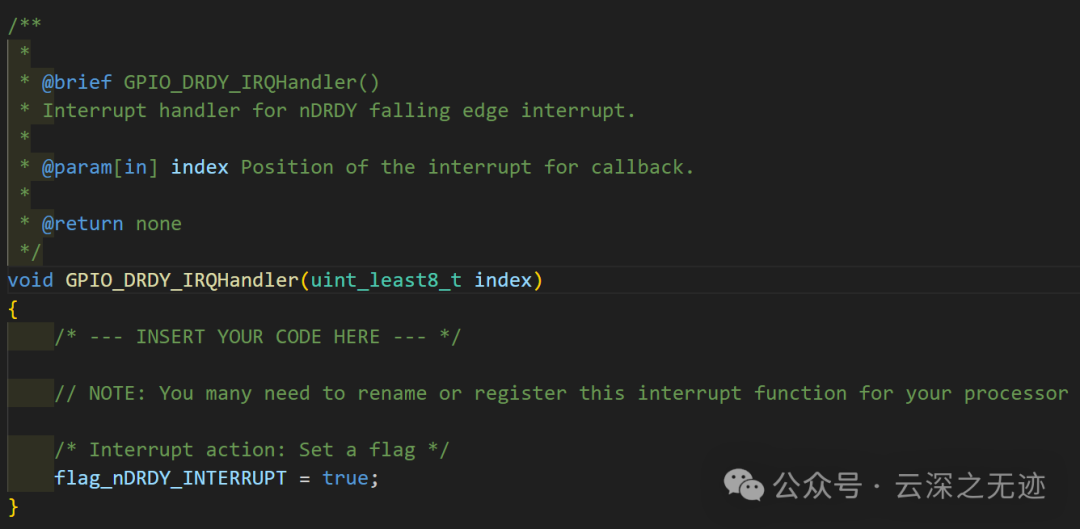

下降邊沿觸發中斷

這個有用

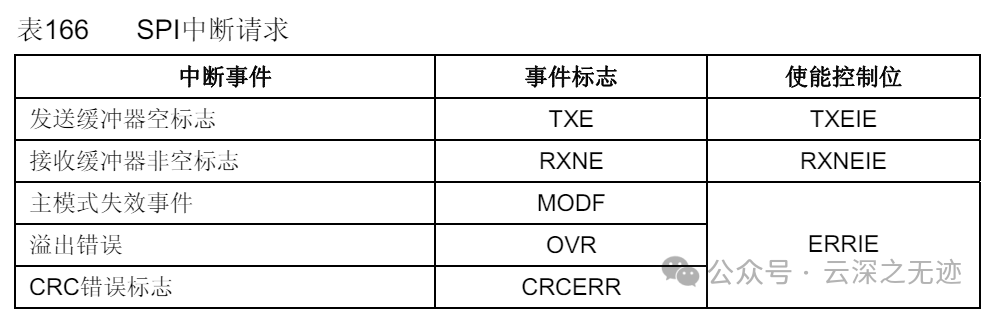

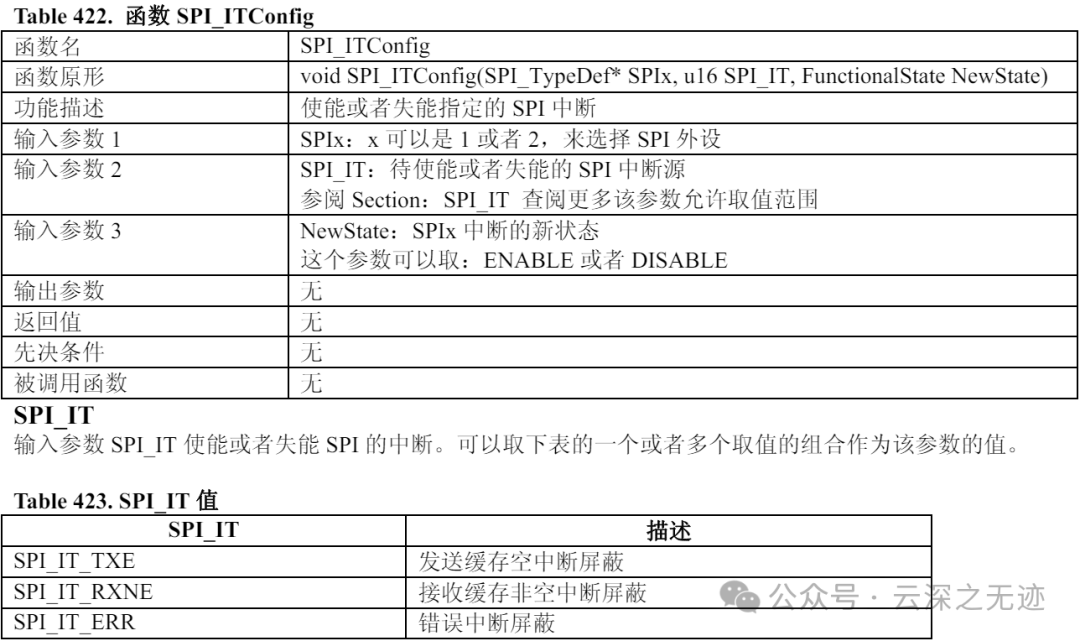

因為STM32的SPI中斷和TI的中斷對不上,下面就看HAL的API:

SPI的中斷有這些

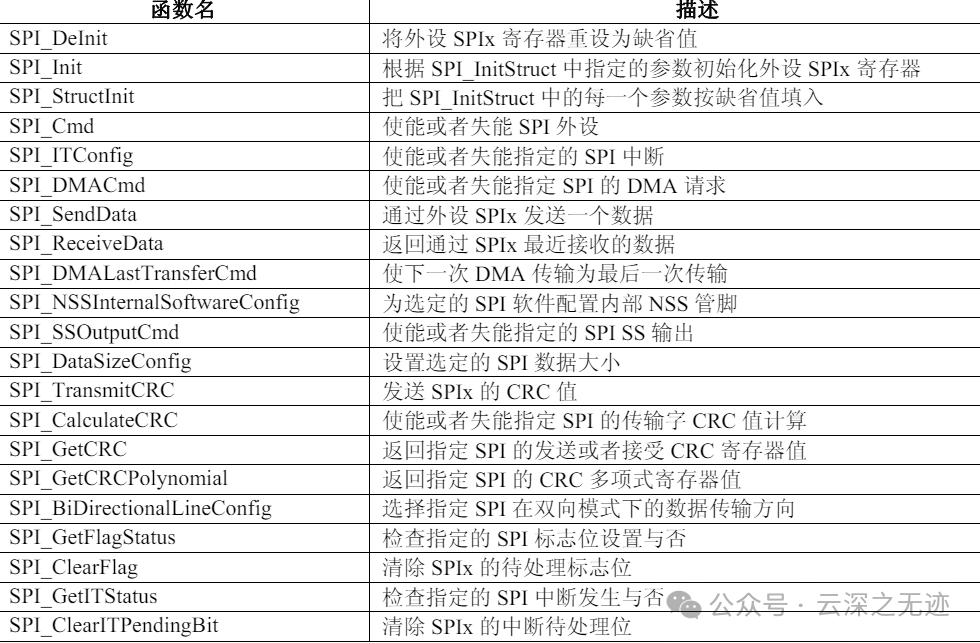

所有的函數

中斷

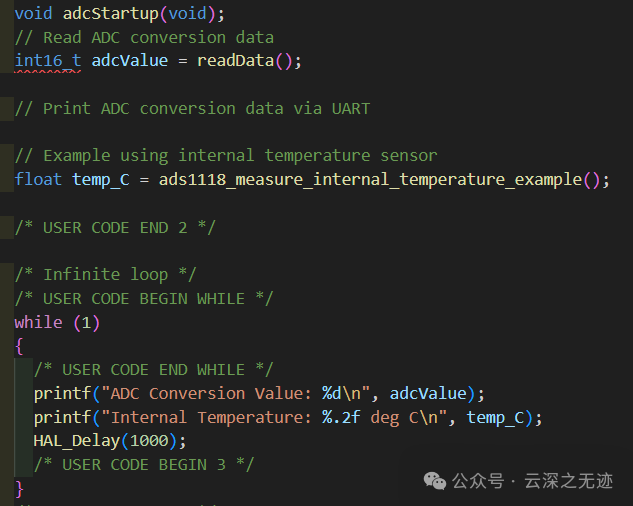

在main里面的文件

我要做的工作是在HAL文件里面構建STM32 SPI的硬件重構

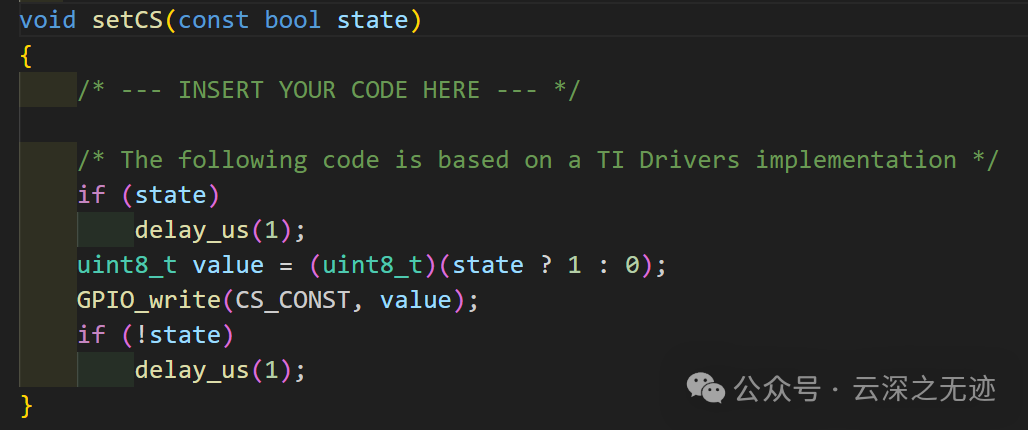

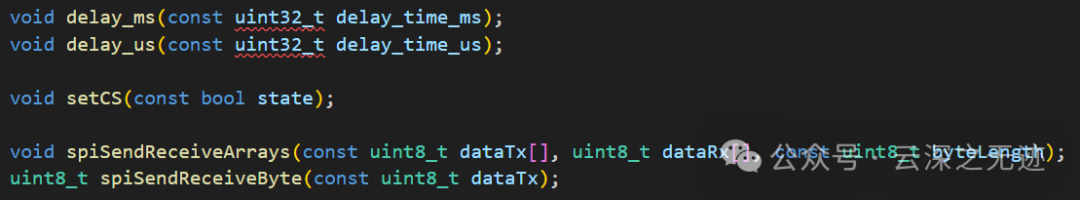

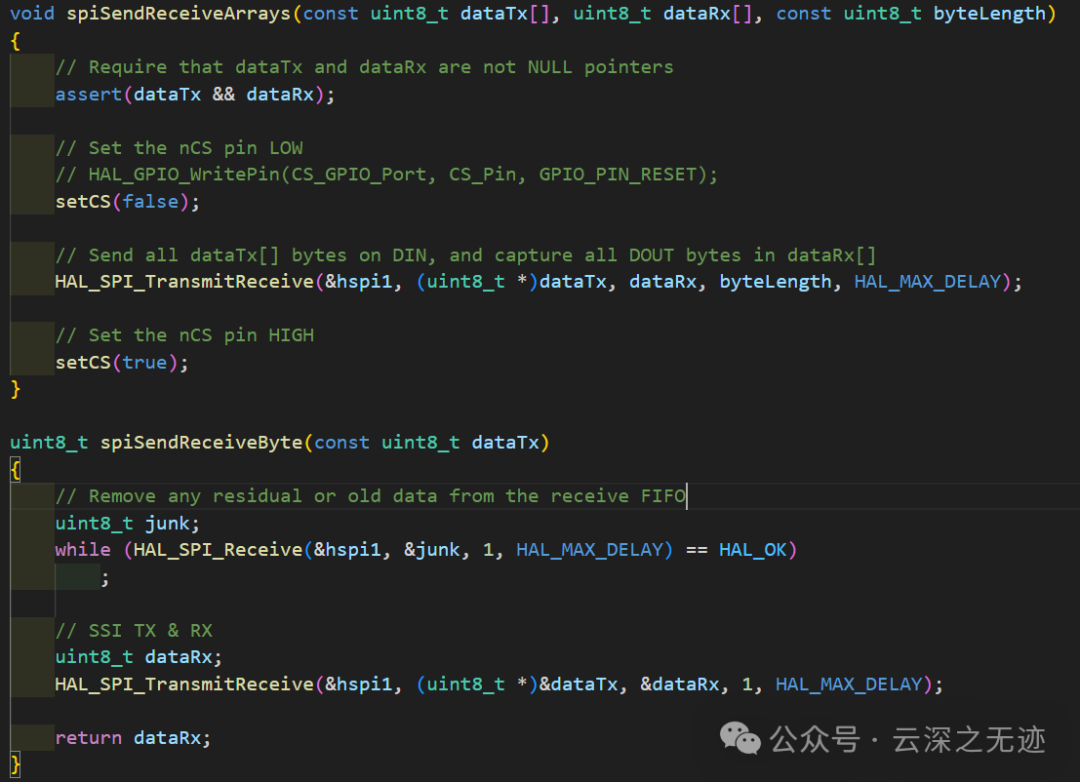

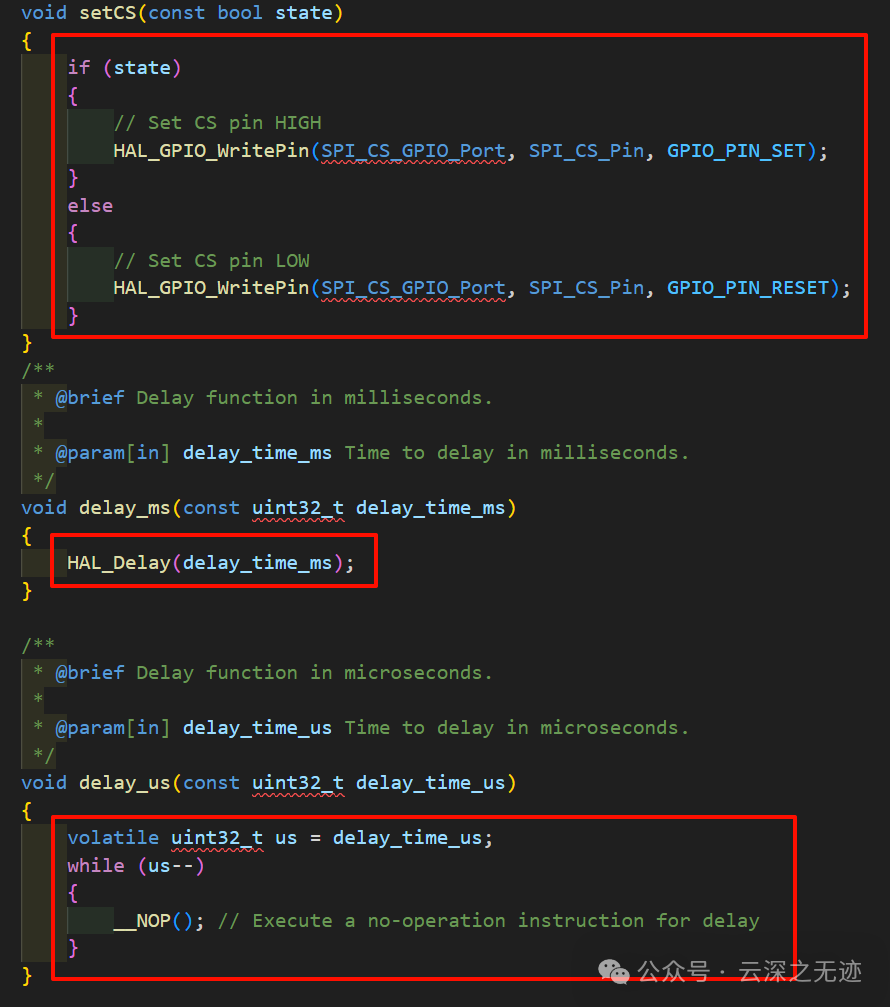

需要實現的是ms和us的延時,CS的控制和收發功能

SPI函數

這里是延時和CS的實現

ADS1118的內部就可以不用管了。別看寫的簡單,debug也很耗時。

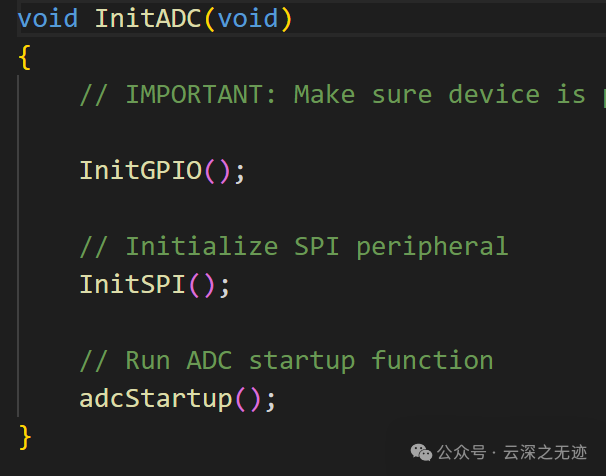

編譯無錯誤,移植完成

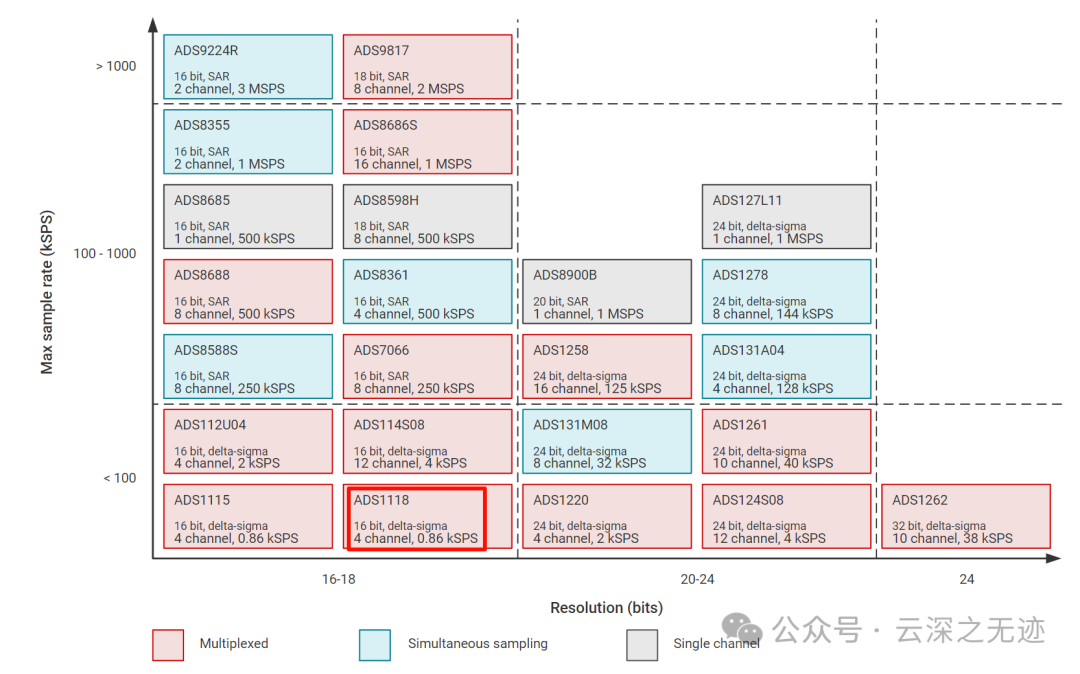

可以看看ADS1118的定位

https://www.stmcu.com.cn/Designresource/detail/software/711298

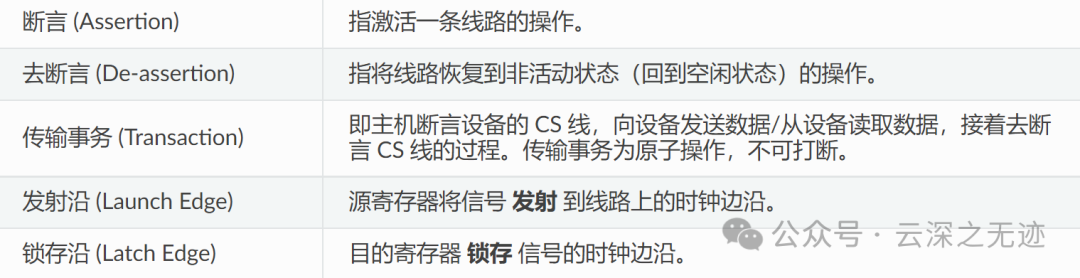

術語表:

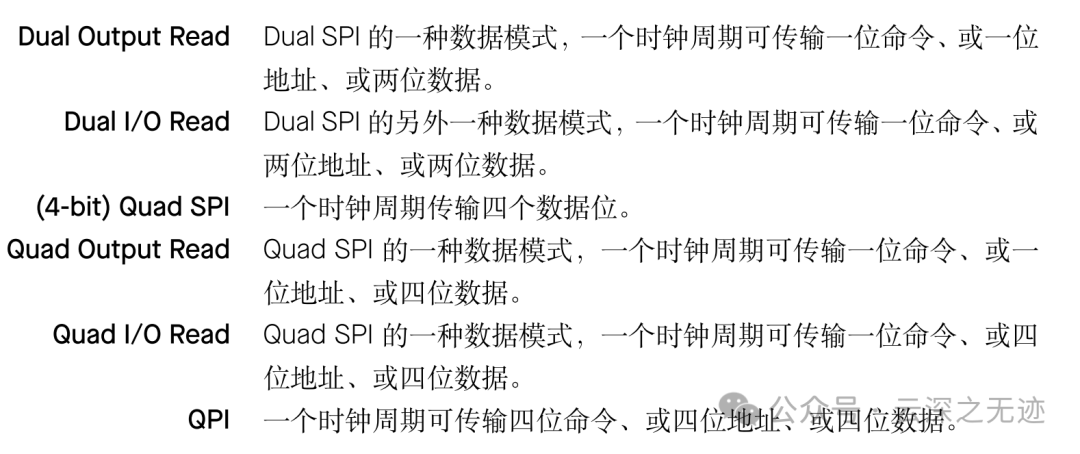

Standard SPI: CLK, /CS, DI, DO, /WP, /Hold Dual SPI: CLK, /CS, IO0, IO1, /WP, /Hold Quad SPI: CLK, /CS, IO0, IO1, IO2, IO3 SIO0(serial io 0)

接口說明

CLK(Serial Clock):時鐘線

/CS(Chip Select):片選接口

DI(Serial Data Input):數據輸入端口

DO(Serial Data Output):輸出輸出端口

審核編輯:劉清

-

上拉電阻

+關注

關注

5文章

359瀏覽量

30606 -

寄存器

+關注

關注

31文章

5336瀏覽量

120230 -

STM32

+關注

關注

2270文章

10895瀏覽量

355729 -

增益放大器

+關注

關注

2文章

100瀏覽量

29047 -

SPI協議

+關注

關注

0文章

18瀏覽量

8361

原文標題:SPI協議詳解以ADS1118為例

文章出處:【微信號:TT1827652464,微信公眾號:云深之無跡】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

SPI協議詳解(以ADS1118為例)

SPI協議詳解(以ADS1118為例)

評論