簡介

本文可讓開發(fā)者們看懂 AMD Vivado Design Tool 2023.2 中的“AMD Versal Adaptive SoCCPM PCIE PIO EP 設計”CED 示例。?

“AMD VersalAdaptive SoCCPM PCIE PIO EP 設計”支持您使用可以正常工作的既定設計來初始化您的系統(tǒng)開發(fā)板,以驗證此開發(fā)板的連接與功能。

PCI Express 系統(tǒng)主機 CPU 通常使用編程輸入/輸出 (PIO) 傳輸事務來訪問 PCI Express 邏輯中的存儲映射輸入/輸出 (MMIO) 位置和配置映射輸入/輸出 (CMIO) 位置。

Endpoints for PCI Express 可接受“Memory and I/O Write”傳輸事務,并以“Completion with Data”傳輸事務來響應“Memory and I/O Read”傳輸事務。

功能特性

AMD VersalAdaptive SoCPIO 設計的 CED 示例按“DWORD Aligned Mode”來配置。以下提供了您可利用設計示例來實踐的部分功能特性:

此設計在 AMD Versal Adaptive SoC器件塊 RAM 內實現(xiàn)一個目標空間。

此目標空間可通過存儲器寫 32 TLP 和存儲器讀 32 TLP 來訪問。

對于來自核的有效的存儲器讀 32 TLP 請求,PIO 會生成完成包(大小即有效載荷的大小)以作為響應。

PIO 設計會通過將有效載荷更新到 AMDVersal Adaptive SoC器件中的塊 RAM 空間的目標地址內來處理 1DW/2DW 存儲器寫或 I/O 寫 TLP。

雖然此鏈接指向 PL PCIE IP 核設計示例,但 AMD Versal Adaptive SoCPIO 設計的 CED 示例同樣基于此設計示例,因此該鏈接中提供的詳細信息同樣適用于 CPM PIO 設計。

設計生成

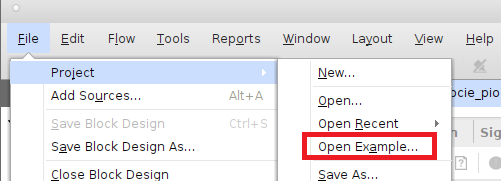

在 AMD Vivado Design Tool 中,轉至“File -> Project -> Open Example”。

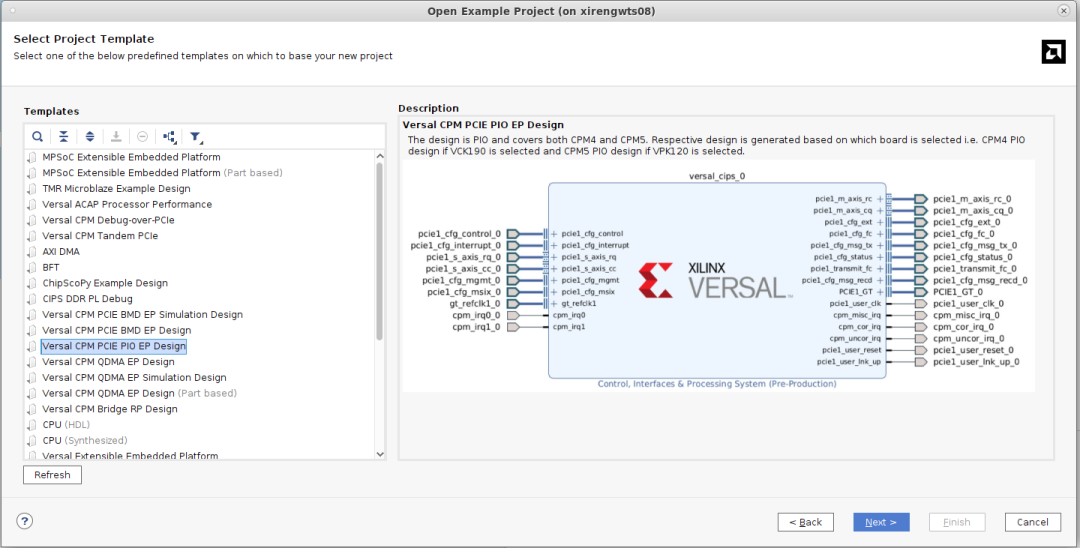

這樣即可看到如下可用示例列表。選中“AMD Versal Adaptive SoCCPM PCIE PIO EP Design”,然后單擊“Next”。

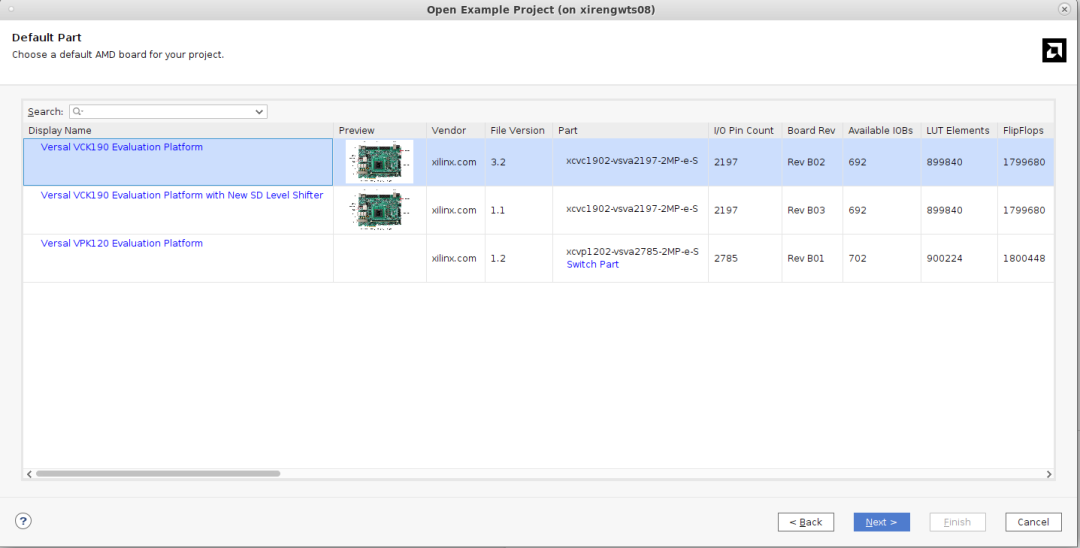

所提供的設計示例支持 VCK190 評估板和 VCK120 評估板。對于其他開發(fā)板,為其中任一開發(fā)板生成的設計示例均可作為參考用于為所需開發(fā)板進行設計轉換。

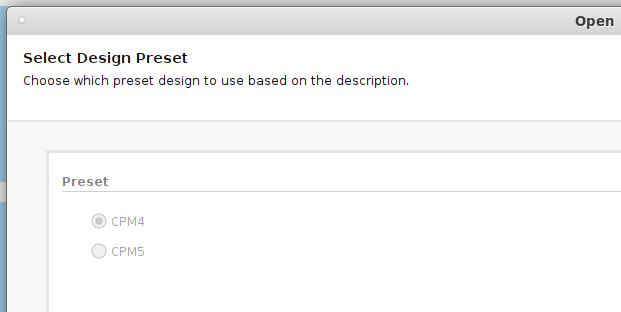

根據(jù)所選開發(fā)板,將自動選擇“Preset”,針對 VCK190 將選中 CPM4,針對 VPK120 則選中 CPM5。

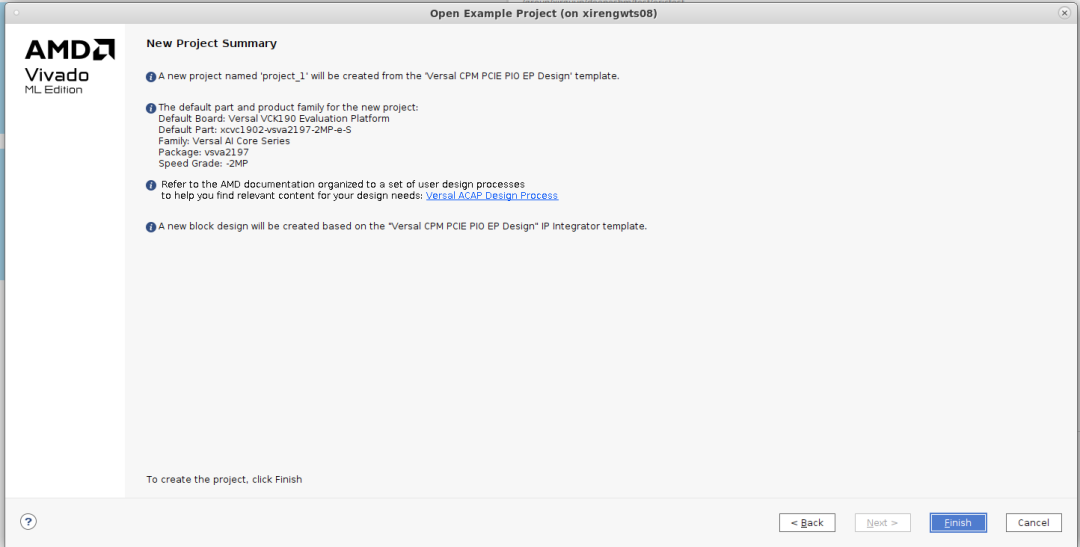

復查工程匯總信息,確認所選部件和產品系列正確。

CPM 配置

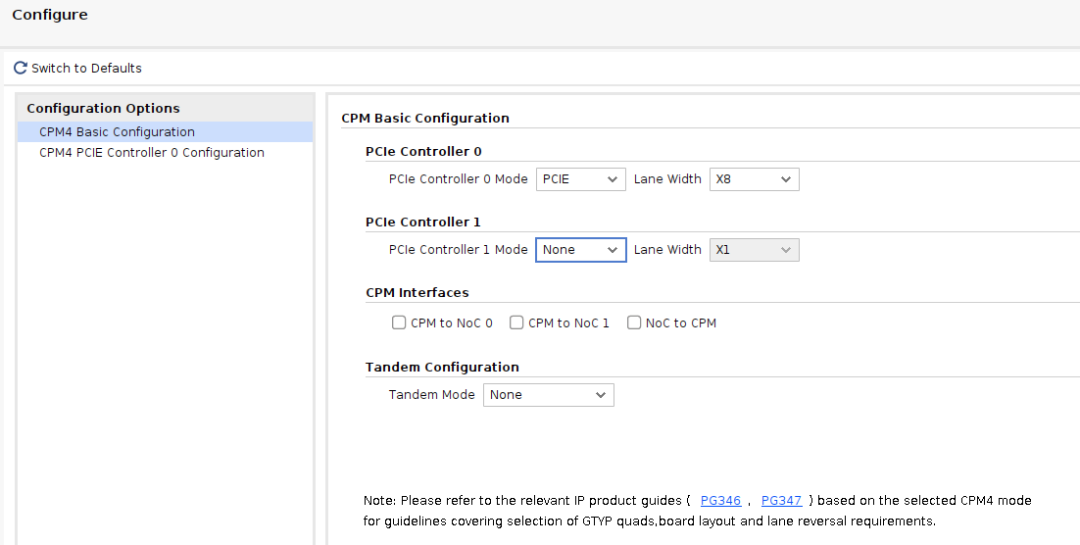

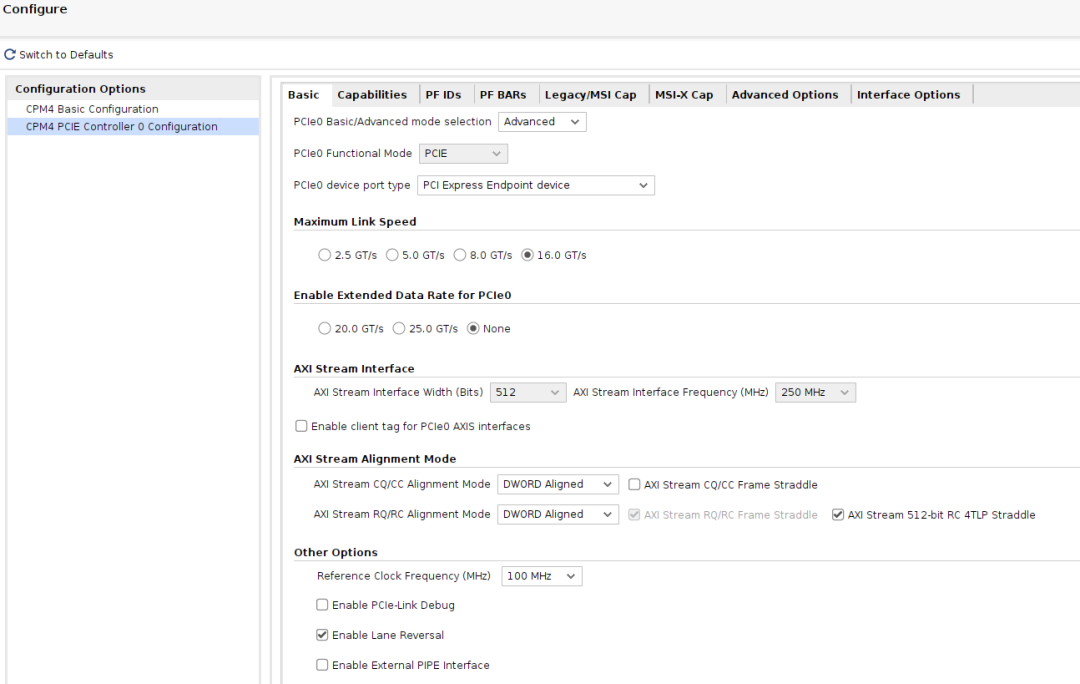

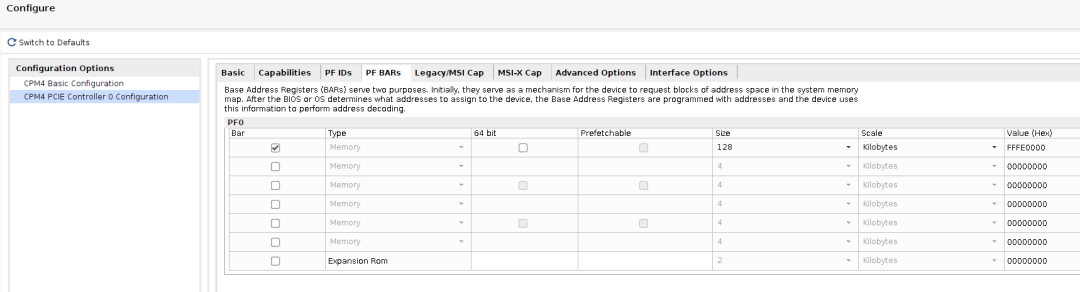

生成的默認 AMD Versal Adaptive SoCCPM PCIE PIO EP 設計配置如下:

Gen4x8。

DWORD 對齊。

啟用 AXI Stream 512 位 RC 4TLP 跨接。

禁用 AXI Stream CQ/CC 跨幀。

啟用通道翻轉。

使用 PCIE 控制器 0。

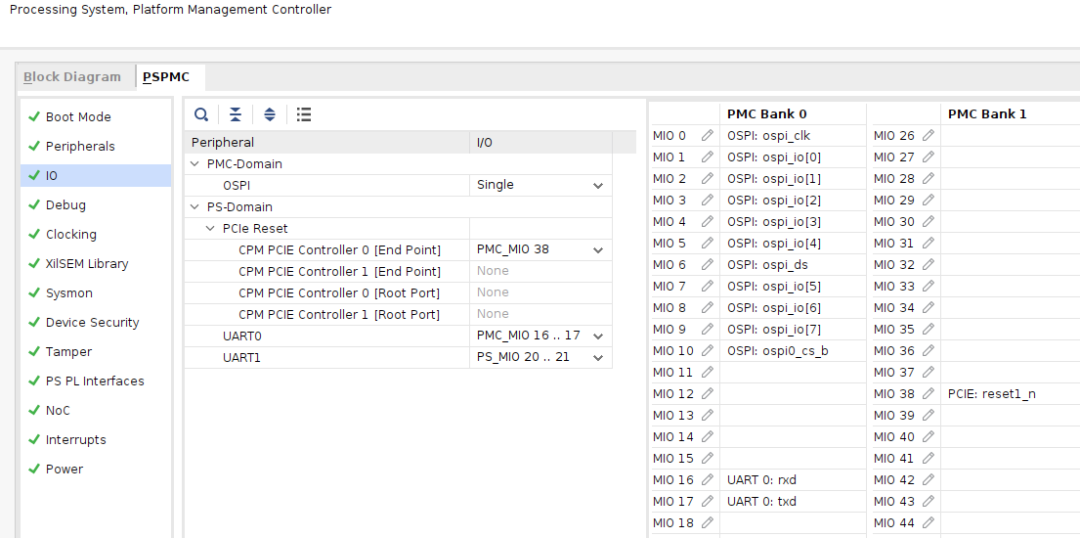

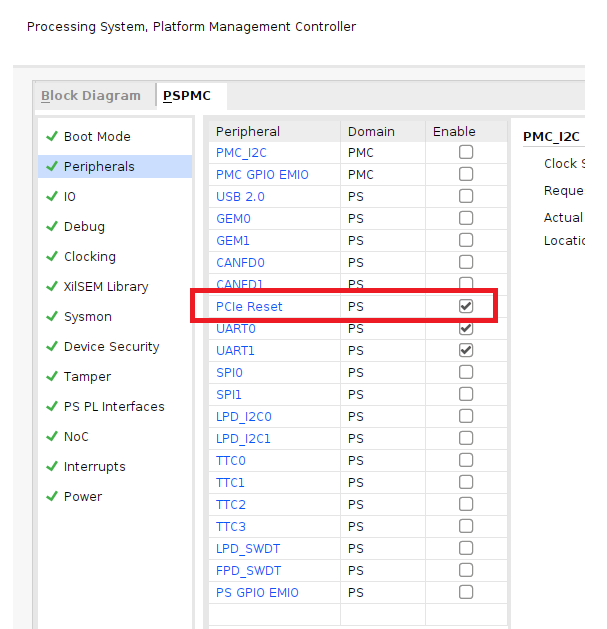

針對所選開發(fā)板和控制器將復位配置到 PMC_MIO 38。

PS PMC 配置

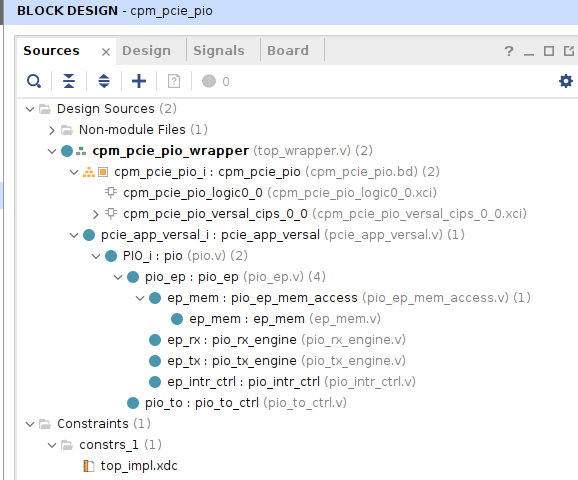

設計示例模塊框圖

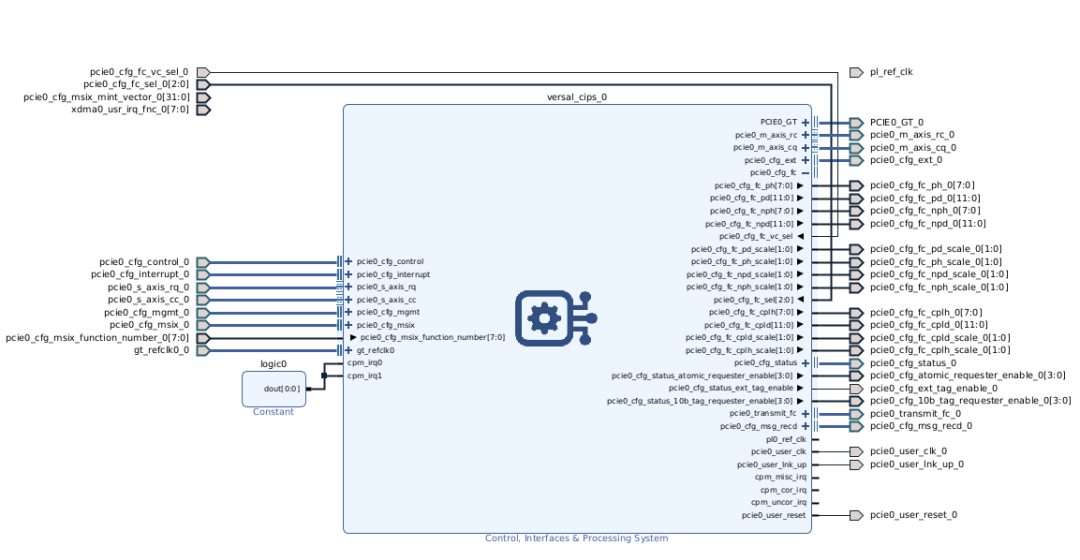

以下是生成的 CIPS 的最終模塊框圖。I/O 和復位約束均由設計示例基于所選開發(fā)板來進行分配。

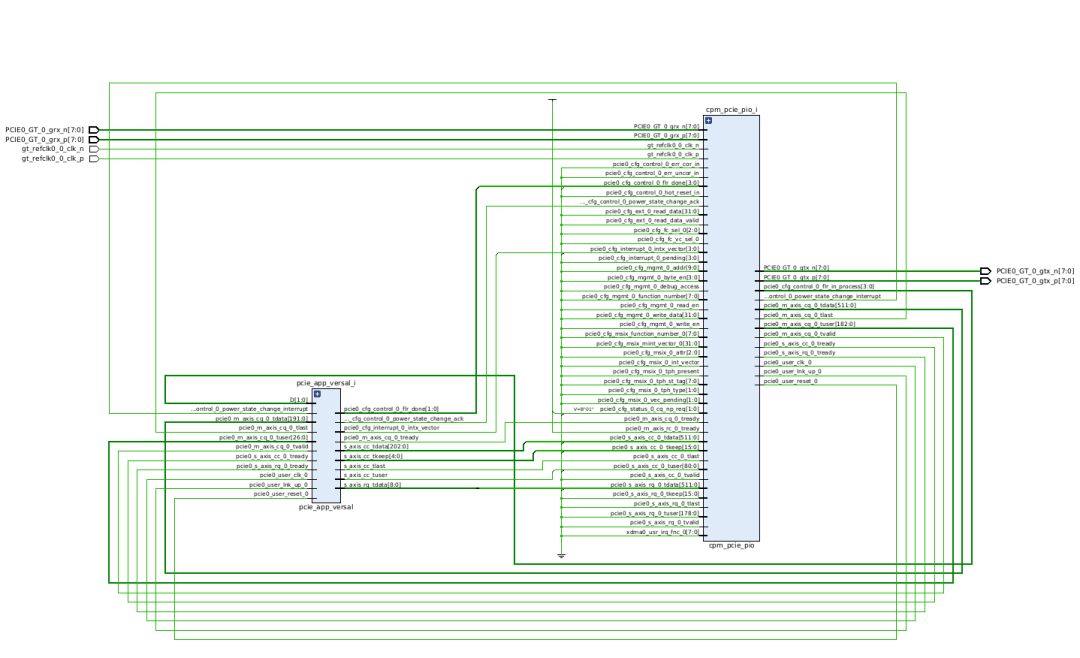

以下板級原理圖設計顯示了由 CPM 與 PIO 應用在后端組成的整體設計示例。

設計示例源文件

pcie_app_versal_i是設計示例模塊,負責處理傳入的“Memory Read”和“Memory Write”,并以“Completion”包來響應。

下表顯示了 PIO 示例設計的文件結構。

| 文件 | 描述 |

| PIO.v | 頂層設計封裝 |

| PIO_INTR_CTRL.v | PIO 中斷控制器 |

| PIO_EP.v | PIO 應用模塊 |

| PIO_TO_CTRL.v | PIO 關閉控制器模塊 |

| PIO_RX_ENGINE.v | 32 位接收引擎 |

| PIO_TX_ENGINE.v | 32 位發(fā)射引擎 |

| PIO_EP_MEM_ACCESS.v | 端點存儲器訪問模塊 |

| PIO_EP_MEM.v | 端點存儲器 |

| PIO_EP_XPM_SDRAM_WRAP.v | 采用 Dword 對齊模式的端點存儲器 |

審核編輯:劉清

-

控制器

+關注

關注

112文章

16332瀏覽量

177806 -

存儲器

+關注

關注

38文章

7484瀏覽量

163762 -

SoC設計

+關注

關注

1文章

148瀏覽量

18774

原文標題:開發(fā)者分享|AMD Versal? Adaptive SoC CPM PCIE PIO EP 設計 CED 示例

文章出處:【微信號:gh_2d1c7e2d540e,微信公眾號:XILINX開發(fā)者社區(qū)】歡迎添加關注!文章轉載請注明出處。

發(fā)布評論請先 登錄

相關推薦

AMD Versal SoC刷新邊緣AI性能,單芯片方案驅動嵌入式系統(tǒng)

Spartan6 PCIe PIO示例無法使用lspci查看卡

使用QEMU啟動Versal VCK190

Versal CPM AXI Bridge模式的地址轉換

用于PCI Express v2.1的Versal ACAP CPM模式產品指南

AMD Versal SoC全新升級邊緣AI性能,單芯片方案驅動嵌入式系統(tǒng)

AMD發(fā)布第二代Versal自適應SoC,AI嵌入式領域再提速

ALINX VERSAL SOM產品介紹

AMD Versal自適應SoC CPM5 QDMA的Tandem PCIe啟動流程介紹

AMD推出第二代Versal Premium系列

AMD Vivado Design Suite 2024.2全新推出

如何通過PMC_GPIO喚醒AMD Versal? Adaptive SoC Linux系統(tǒng)

AMD Versal? Adaptive SoC CPM PCIE PIO EP設計CED示例

AMD Versal? Adaptive SoC CPM PCIE PIO EP設計CED示例

評論