高速先生成員--黃剛

對于高速差分信號到底需要控制多少歐姆的阻抗,高速先生相信大部分工程師首先都會看下例如信號的協(xié)議文檔或者芯片的文檔,看看里面有沒有推薦的控制阻抗值。例如像PCIE信號,在4.0之后的阻抗會明確要求按照85歐姆來控制,USB阻抗會要求控制90歐姆等。除了這一部分有明確的阻抗要求外,其他沒明確要求的高速信號你們會控多少歐姆阻抗呢?就好像為什么PCB的單端走線要控制50歐姆一樣,差分走線如果沒有明確協(xié)議規(guī)定,那就按100歐姆來控制。很多工程師其實都不一定很清楚的知道內在的理論和原因,但是也會潛意識的控制100歐姆,可見100歐姆差分線這個觀念是多么的深入人心!

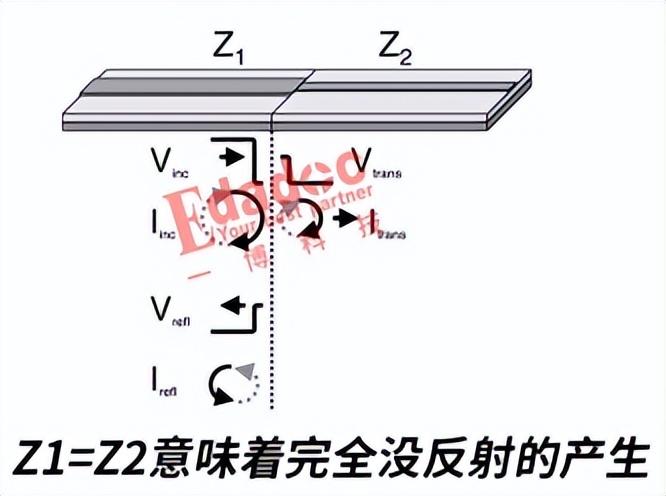

但是,深入人心歸深入人心,本文想探究的是:100歐姆真的是在任何產品中最好的阻抗選擇嗎?當然,從反射的理論來說,如果從收發(fā)芯片的負載到PCB的每個地方鏈路的阻抗都完美的做到100歐姆的話,那高速線控100歐姆肯定是最好的選擇啦!意味著鏈路上的任何地方阻抗都匹配,完全沒有反射的存在,這還能不好嗎?

真實情況會怎么樣呢?為了能有說服力,本文舉2個真實項目的仿真案例,大家一起細品細品哈!

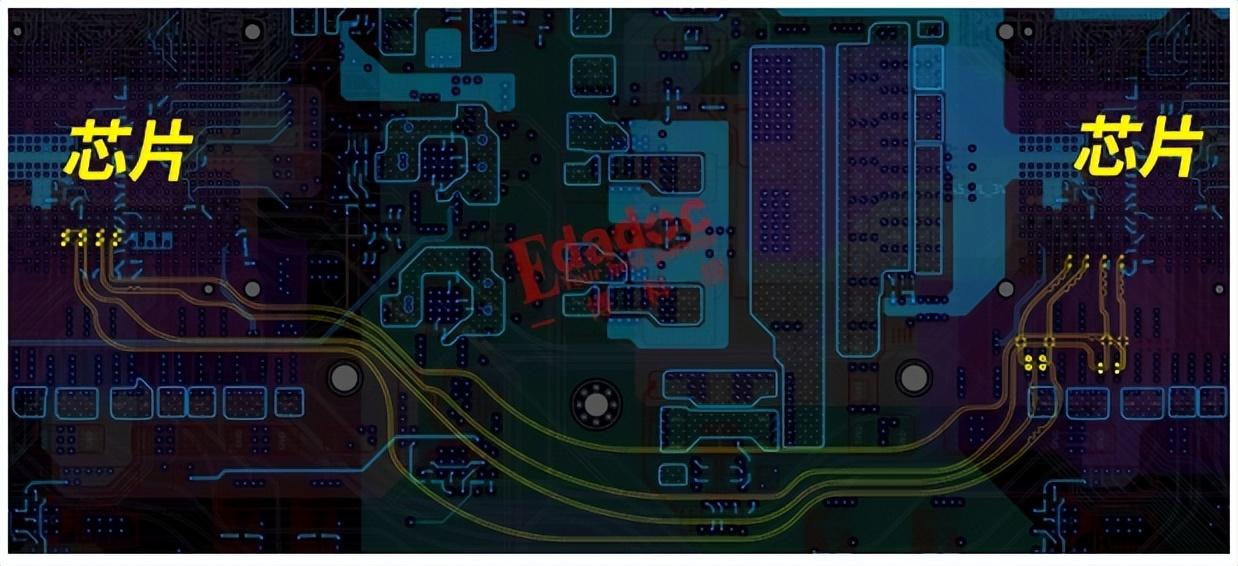

案例一:板內芯片到芯片的25G信號仿真案例

在芯片到芯片的PCB鏈路中,除了PCB走線外,一定會存在一些阻抗不連續(xù)的結構,如上面的案例中,BGA兩端會存在過孔,接收端一般還會有交流耦合電容。有一定仿真經驗的小伙伴們都知道,像BGA的過孔,電容這個位置的阻抗一般來說都很難做到100歐姆,大部分的case無論怎么優(yōu)化,都會低于100歐姆。這個時候我們來驗證如果這幾個阻抗不連續(xù)點的阻抗達不到100歐姆,例如做到比較理想的95歐姆左右的情況下,PCB走線分別按照100和降低到95歐姆控制時的無源仿真性能對比。

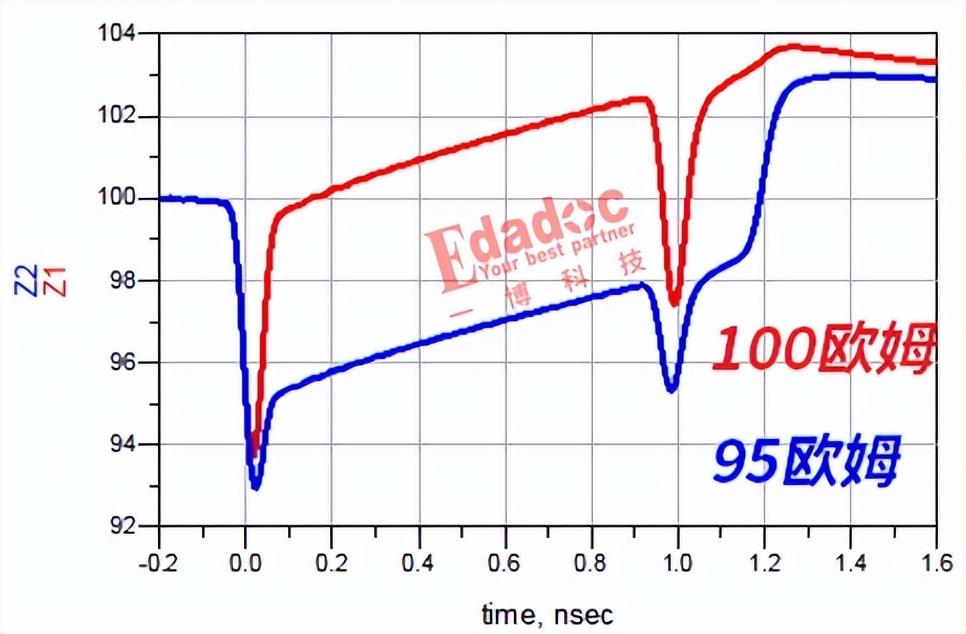

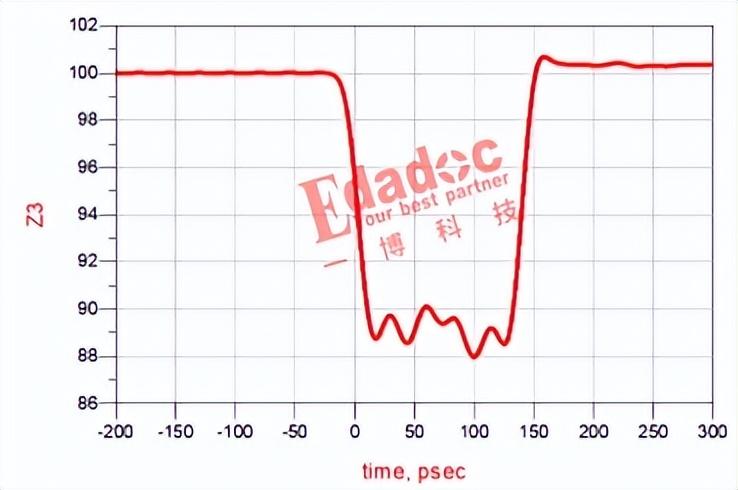

首先我們來看看芯片到芯片鏈路TDR阻抗的對比,也就是PCB走線選擇默認的100歐姆和降低到95歐姆來控制時的差異。

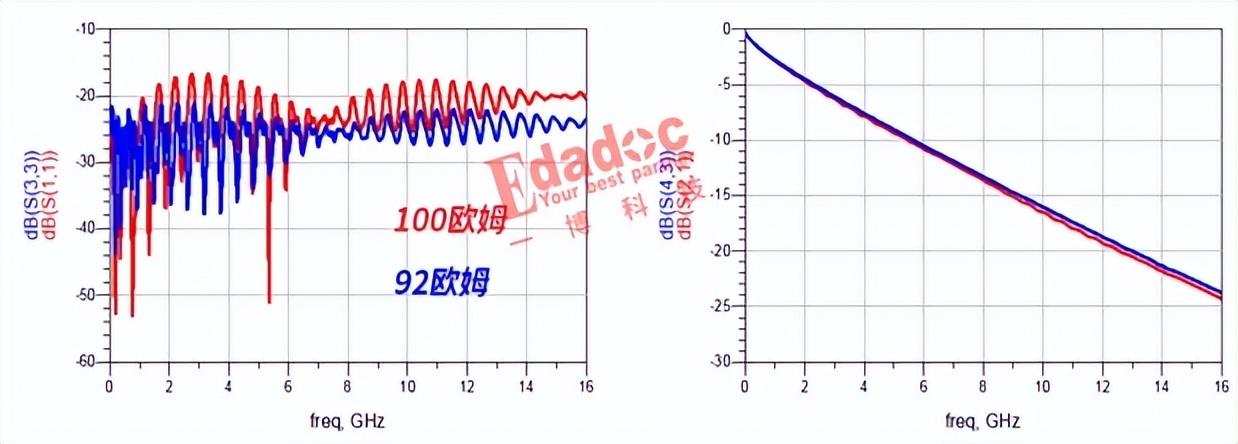

當然從TDR阻抗來看,不能很直觀的看到差異,于是我們來看另外兩個更關鍵的指標,那就是插損和回損的指標。

從插損的指標看,在優(yōu)化好幾個不連續(xù)點后,雖然100歐姆走線的仿真性能也就很不錯了,但是從仿真結果能看到,95歐姆PCB走線的結果更有優(yōu)勢,無論是從回損還是插損的角度看,都是性能更好的一方。

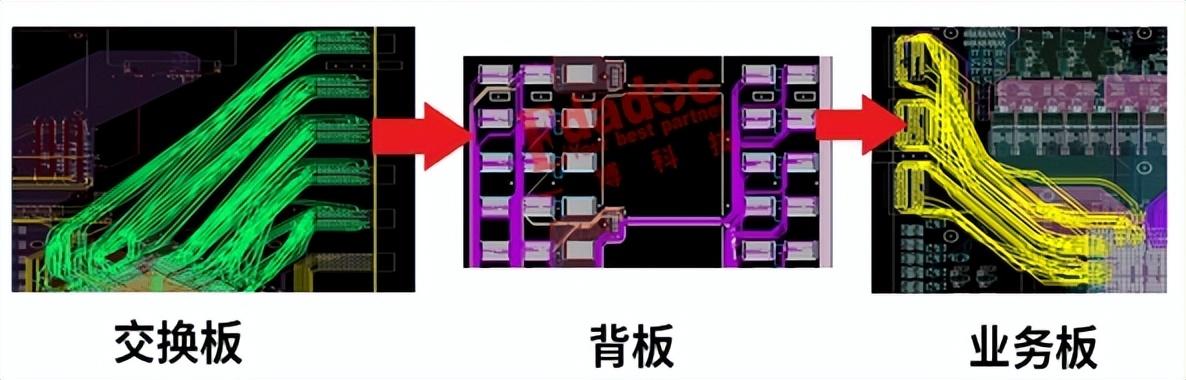

案例二:經過背板連接器的芯片到芯片的25G信號仿真案例

另外一個案例就是跨版的25G信號的case了,整個系統(tǒng)的連接關系如下所示:

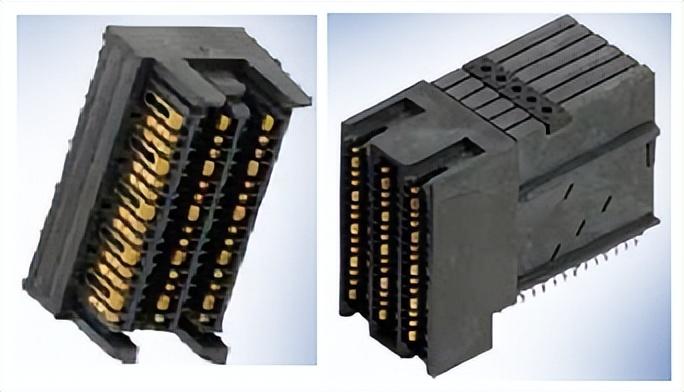

前面單板上的BGA過孔的阻抗就不再敘述了,這里要關注的是跨版連接的高速連接器這個地方。本案例中用到的這款高速背板連接器是某知名廠家的產品,是一款在這個速率下很通用,得到有效驗證的連接器。

這款連接器廠家的標稱阻抗是多少呢?92歐姆,不是你們想象中的100歐姆哦。我們拿到其中的一對連接器信號的阻抗來看,的確也差不多。90歐姆出頭的樣子。

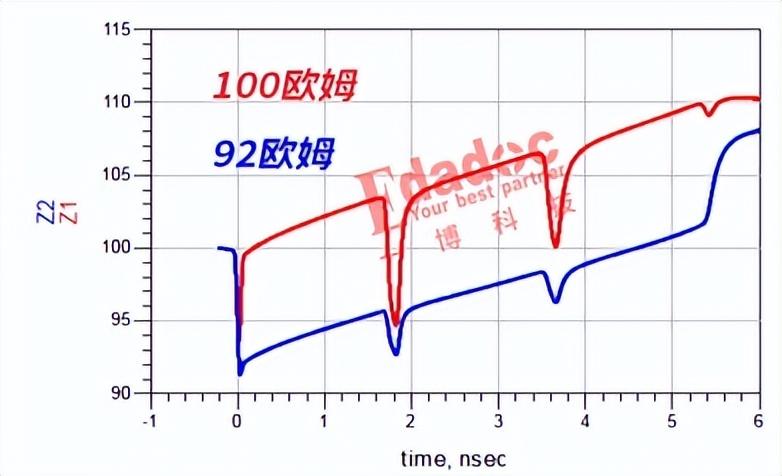

那我們還是一樣,這個系統(tǒng)的三塊互連的板子,我們分別把高速走線的阻抗按照100歐姆和降低到92歐姆來控制,看看性能的對比。

首先我們還是看看整個鏈路的TDR阻抗的對比,能明顯看到兩個連接器的低點,如下所示:

那么插損和回損的性能對比又是怎么樣的呢?還是讓大家失望了,三塊板子控制92歐姆的走線還是會比100歐姆走線的性能來得好。

當然,這中的理論有點復雜,這里就不展開來分析了。從設計的角度來看,如果沒明確的要求,硬件工程師或者設計工程師按照100歐姆來控制高速走線本身也沒太大的問題,我們很多case按照100歐姆的差分信號設計也是完全沒有問題。本文更多的可能是給大家一種另類的思路,去尋找一些更優(yōu)的設計方案。但是還是要弱弱的告示下哈,如果不經過比較精確的仿真,還是不要隨便去嘗試,因為你并不知道多少才是好,只有仿真才能很好的把鏈路的性能給量化出來,設計的朋友請謹慎使用這招,用得不好還是很容易翻車的哦!

問題來了:

列舉下大家的產品在PCB設計中常見的阻抗不連續(xù)的地方,并簡單描述下你們的設計優(yōu)化方法?

審核編輯 黃宇

-

芯片

+關注

關注

459文章

52199瀏覽量

436293 -

阻抗

+關注

關注

17文章

970瀏覽量

47039 -

PCB

+關注

關注

1文章

2022瀏覽量

13204

發(fā)布評論請先 登錄

PCB制板廠加工問題很大啊,高速PCB傳輸線阻抗一直往上跑

PCB Layout中的三種走線策略

揭秘PCB走線設計黑洞:仿真視角下挑戰(zhàn),工程師與PCB設計師必看!

高速信號線走線規(guī)則有哪些

高速信號走線越短越好嗎為什么

從驅動端到串聯電阻之間的這一段走線應該走成多少阻抗呢?

差分信號線的選擇與處理

為什么是50歐姆,50歐姆阻抗的來源和意義

評論