隨著信息技術(shù)的迅猛發(fā)展,存算一體技術(shù)逐漸成為計(jì)算領(lǐng)域的研究熱點(diǎn)。在這一領(lǐng)域,基于SRAM(靜態(tài)隨機(jī)存取存儲(chǔ)器)和MRAM(磁性隨機(jī)存取存儲(chǔ)器)的存內(nèi)計(jì)算和存算一體架構(gòu)日益受到重視,為計(jì)算性能和能效帶來(lái)了新的可能性。本文將深入探討這兩種技術(shù)的原理、優(yōu)勢(shì)及其在不同領(lǐng)域的應(yīng)用,旨在為讀者提供對(duì)存算一體技術(shù)發(fā)展趨勢(shì)的全面了解。

一.基于 SRAM 的存內(nèi)計(jì)算

在信息技術(shù)的不斷發(fā)展中,SRAM存內(nèi)邏輯計(jì)算技術(shù)日益成為研究的焦點(diǎn)。自2016年Jeloka等人提出了基于SRAM的存內(nèi)邏輯計(jì)算以來(lái),這一領(lǐng)域取得了長(zhǎng)足的進(jìn)步。該技術(shù)不僅僅局限于邏輯運(yùn)算,還應(yīng)用于神經(jīng)網(wǎng)絡(luò)的硬件加速,為計(jì)算領(lǐng)域帶來(lái)了全新的可能性。

SRAM的邏輯運(yùn)算是通過(guò)激活同一列的多個(gè)存儲(chǔ)單元來(lái)實(shí)現(xiàn)的。這些存儲(chǔ)單元的字線(xiàn)被同時(shí)激活,通過(guò)靈敏放大器感測(cè)位線(xiàn)電壓,得到存儲(chǔ)單元存儲(chǔ)比特的邏輯運(yùn)算結(jié)果。在增加額外的邏輯門(mén)后,SRAM可以實(shí)現(xiàn)邏輯或非和邏輯與非運(yùn)算。與傳統(tǒng)的SRAM陣列相比,新的陣列具有更高的密度和更低的功耗,為存內(nèi)計(jì)算提供了更廣闊的發(fā)展空間。

在這一領(lǐng)域的持續(xù)探索中,研究者們提出了更多創(chuàng)新的SRAM存內(nèi)計(jì)算架構(gòu)。例如,Aga等人提出了一種新的存內(nèi)計(jì)算架構(gòu),通過(guò)添加解碼器和使用單端靈敏放大器實(shí)現(xiàn)了邏輯異或運(yùn)算。而Dong等人則提出了一種4+2T的SRAM單元,相比傳統(tǒng)的6T SRAM單元具有更好的噪聲容限。

針對(duì)傳統(tǒng)6T SRAM單元存在的讀寫(xiě)干擾和存儲(chǔ)內(nèi)容翻轉(zhuǎn)等問(wèn)題,研究者們提出了8T和10T SRAM單元。Agrawal等人則提出了使用8T SRAM單元和8+T SRAM單元的解耦讀寫(xiě)路徑,成功實(shí)現(xiàn)了存內(nèi)布爾運(yùn)算,包括邏輯與非、邏輯或非、邏輯異或等邏輯運(yùn)算。相比于6T SRAM單元,8T SRAM單元提高了數(shù)據(jù)的吞吐量和處理速度,為計(jì)算性能帶來(lái)了明顯的提升。

一些研究者還探索了SRAM單元與算術(shù)電路協(xié)同的架構(gòu),例如Rajput等人提出了一種8T SRAM單元與算術(shù)電路協(xié)同的架構(gòu),具有更高的能量利用率和讀取裕量。

基于SRAM的存內(nèi)邏輯計(jì)算技術(shù)不斷創(chuàng)新,為計(jì)算領(lǐng)域帶來(lái)了更高的性能和更低的功耗。隨著這一技術(shù)的不斷發(fā)展,我們有理由期待它在未來(lái)的計(jì)算應(yīng)用中發(fā)揮更加重要的作用。

二.基于 SRAM 的存內(nèi)計(jì)算在神經(jīng)網(wǎng)絡(luò)的應(yīng)用

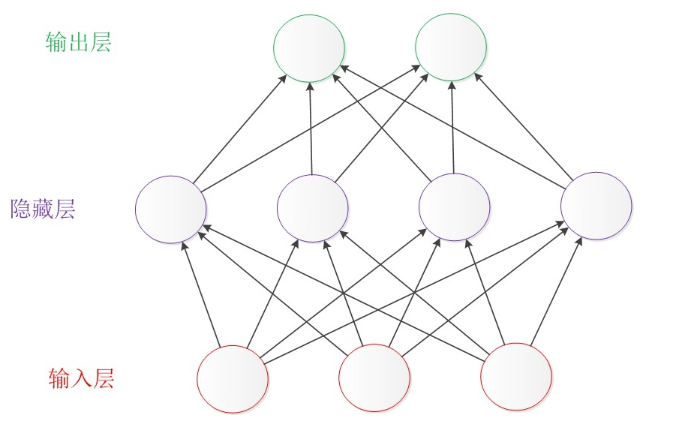

近年來(lái),深度學(xué)習(xí)技術(shù)在神經(jīng)網(wǎng)絡(luò)領(lǐng)域蓬勃發(fā)展,但由于常規(guī)訓(xùn)練通常依賴(lài)于高功耗的CPU或GPU,因此功耗問(wèn)題成為制約其應(yīng)用的重要因素。然而,隨著超大規(guī)模集成電路制造業(yè)的飛速進(jìn)步,嵌入式系統(tǒng)逐漸成為研究的熱點(diǎn)。嵌入式系統(tǒng)以其低功耗和小占用面積的特點(diǎn),成為解決目標(biāo)檢測(cè)等問(wèn)題的理想選擇。

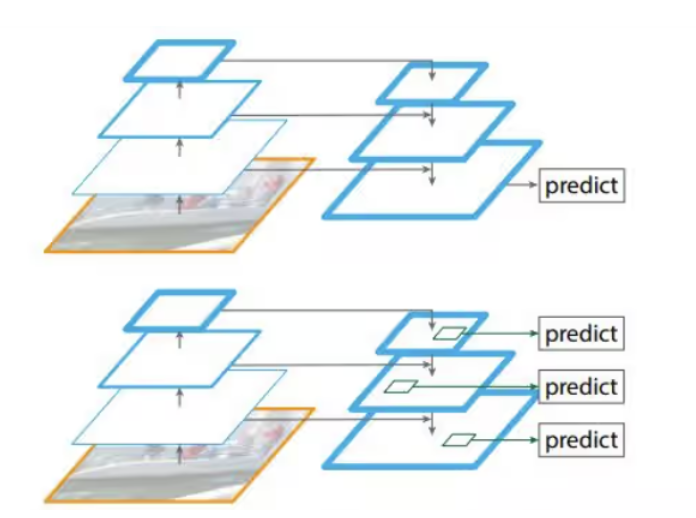

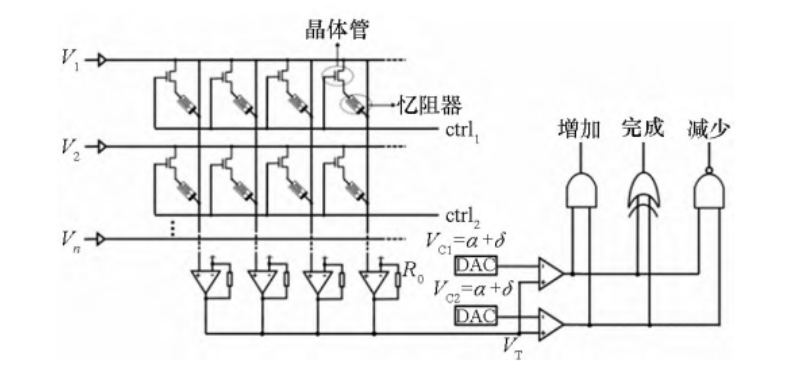

在嵌入式神經(jīng)形態(tài)處理系統(tǒng)的發(fā)展中,基于憶阻器的神經(jīng)形態(tài)計(jì)算體系架構(gòu)引起了廣泛關(guān)注。多種基于憶阻器的神經(jīng)形態(tài)計(jì)算體系架構(gòu)相繼被提出。例如,Sun等人提出了一種基于憶阻器的神經(jīng)形態(tài)計(jì)算架構(gòu),實(shí)現(xiàn)了三層全并行卷積神經(jīng)網(wǎng)絡(luò)(FP-CNN)。而在此基礎(chǔ)上,Sun等人將其作為基本計(jì)算單元提出了一種級(jí)聯(lián)神經(jīng)網(wǎng)絡(luò)體系架構(gòu)。Yakopcic等人則提出了一種基于憶阻器的卷積神經(jīng)網(wǎng)絡(luò),利用多個(gè)憶阻器交叉陣列實(shí)現(xiàn)。

盡管這些方法在網(wǎng)絡(luò)架構(gòu)方面取得了顯著成效,但當(dāng)憶阻器陣列存在低良率問(wèn)題時(shí),其性能卻會(huì)受到明顯影響。為此,本文提出了一種基于憶阻器的神經(jīng)形態(tài)計(jì)算方法,結(jié)合了提高憶阻器陣列乘累加計(jì)算準(zhǔn)確率的校準(zhǔn)方法和可減少訓(xùn)練誤差的原位訓(xùn)練方法,從而能夠提高網(wǎng)絡(luò)在低良率陣列中的識(shí)別率。

這一方法的提出將為嵌入式神經(jīng)計(jì)算帶來(lái)全新的可能性,不僅能夠提高計(jì)算準(zhǔn)確率,還能在較低的功耗下實(shí)現(xiàn)更為穩(wěn)健的性能表現(xiàn)。隨著該方法的進(jìn)一步研究和應(yīng)用,我們有信心在嵌入式神經(jīng)計(jì)算領(lǐng)域邁出更加堅(jiān)實(shí)的步伐,為智能計(jì)算的未來(lái)鋪平道路。

一種編程憶阻器交叉陣列的電路如下圖:

2.1 神經(jīng)網(wǎng)絡(luò)算法(BNN)

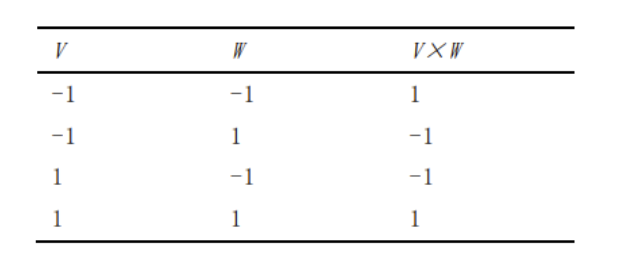

神經(jīng)網(wǎng)絡(luò)算法中,乘加計(jì)算是最為頻繁的操作之一。為了應(yīng)對(duì)計(jì)算需求與功耗之間的平衡,研究者們提出了二值化神經(jīng)網(wǎng)絡(luò)(BNN),將輸入和權(quán)重進(jìn)行二值化,限定為1或-1。這種二值化使得基于SRAM的乘法運(yùn)算可以被視為邏輯同或運(yùn)算。然而,使用一位二值權(quán)重可能會(huì)導(dǎo)致較大的精度損失,因此研究者們將注意力轉(zhuǎn)向了并行計(jì)算,以實(shí)現(xiàn)多位權(quán)重運(yùn)算。

一種被提出的并行計(jì)算結(jié)構(gòu)包括WL開(kāi)關(guān)矩陣用于激活多行字線(xiàn),閃存ADC的多電平檢測(cè)器(MLSA)以及生成基準(zhǔn)電壓的參考生成器。另一種基于6T SRAM的雙拆分結(jié)構(gòu)實(shí)現(xiàn)了完全并行的乘積和累加計(jì)算,取得了顯著的效果。該架構(gòu)不僅可以實(shí)現(xiàn)全連接層的計(jì)算時(shí)間達(dá)到2.3 ns,而且能效最高可達(dá)55.8 TOPS/W。然而,這種架構(gòu)使用了大量的晶體管,導(dǎo)致了較大的面積。

乘法真值表如下。

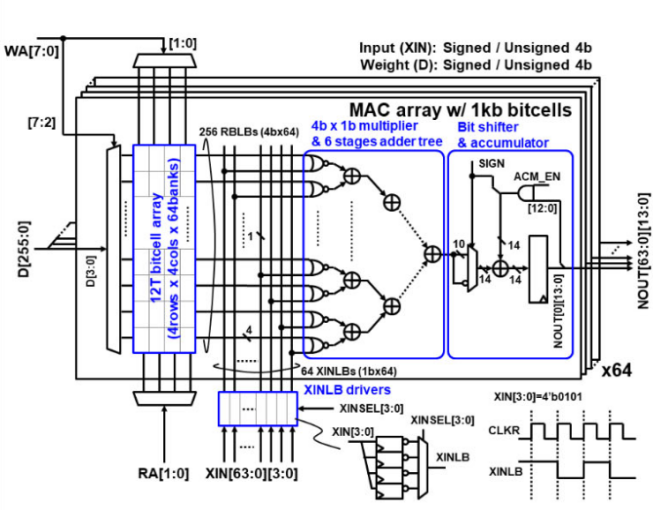

Nguyen等人提出了用于DNN存內(nèi)計(jì)算的10T SRAM,并設(shè)計(jì)了整體架構(gòu),成功映射了LeNet-5手寫(xiě)數(shù)字識(shí)別網(wǎng)絡(luò)。該架構(gòu)支持完全并行的乘加計(jì)算,并且實(shí)現(xiàn)了4位權(quán)重、4位輸入、8位輸出的乘加操作。另外,Su等人提出了可用于2到8位運(yùn)算的雙向轉(zhuǎn)置6T SRAM,支持神經(jīng)網(wǎng)絡(luò)推理和訓(xùn)練的過(guò)程。

此外,為了進(jìn)一步降低功耗,研究者們還研究了稀疏性處理。Han等人提出了一種基于8T SRAM的DNN加速器,不僅具有前向傳播和后向傳播功能,還具有稀疏性處理功能。通過(guò)只存儲(chǔ)非零值及其地址的方式來(lái)過(guò)濾零值,使得不必要的計(jì)算被跳過(guò),最終實(shí)現(xiàn)了功耗上的降低。

在國(guó)內(nèi)外,許多優(yōu)秀團(tuán)隊(duì)也為SRAM的存內(nèi)計(jì)算做出了貢獻(xiàn)。他們提出了各種創(chuàng)新的方法和結(jié)構(gòu),如無(wú)乘法函數(shù)逼近器、更高線(xiàn)性度和吞吐量的SRAM單元、無(wú)ADC的動(dòng)態(tài)SRAM架構(gòu)等,以加速神經(jīng)網(wǎng)絡(luò)的計(jì)算過(guò)程并降低功耗。這些研究成果為神經(jīng)網(wǎng)絡(luò)計(jì)算的進(jìn)一步優(yōu)化提供了重要的參考和啟示。

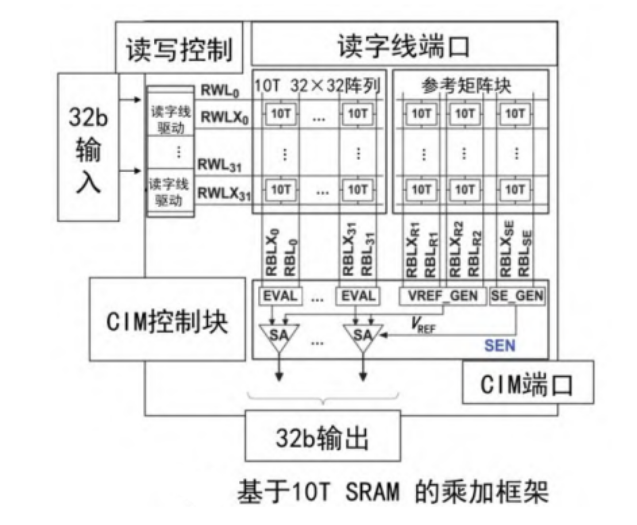

如下圖所示,這種架構(gòu)通過(guò)在一個(gè)32×32的10T SRAM陣列中輸入32個(gè)輸入向量,將輸入向量與權(quán)重矩陣做乘法運(yùn)算。在同一列上的所有SRAM單元的位線(xiàn)上的電流被求和并轉(zhuǎn)換成模擬電壓,在敏感放大器模塊中將此模擬電壓與參考電壓進(jìn)行對(duì)比,生成數(shù)字信號(hào)的輸出。參考電壓由3列10T SRAM組成的參考陣列塊生成,同時(shí)此參考陣列塊還產(chǎn)生檢測(cè)放大器SA的檢測(cè)使能信號(hào)。通過(guò)這樣的方式,完成了矩陣和向量之間的乘加運(yùn)算。

這種架構(gòu)是通過(guò)28納米CMOS工藝實(shí)現(xiàn)的,具有高能效和高吞吐量的優(yōu)勢(shì)。這意味著它在進(jìn)行神經(jīng)網(wǎng)絡(luò)計(jì)算時(shí)能夠以更低的功耗和更高的效率完成任務(wù),從而提高了整個(gè)系統(tǒng)的性能表現(xiàn)。

三.基于 MRAM 的存算一體

基于MRAM(磁性隨機(jī)存取存儲(chǔ)器)的存算一體(MRAM-in-Memory Computing)是一種新型的計(jì)算模式,它結(jié)合了內(nèi)存和計(jì)算的功能,利用MRAM的非易失性和快速讀寫(xiě)特性,在存儲(chǔ)器內(nèi)部進(jìn)行計(jì)算操作,從而提高計(jì)算效率和能源利用率。

MRAM作為一種新型的存儲(chǔ)技術(shù),具有快速的讀/寫(xiě)速度、低功耗和非易失性等優(yōu)點(diǎn)。這些特性使得MRAM非常適合用于存算一體的應(yīng)用。在存算一體中,計(jì)算任務(wù)可以直接在MRAM中進(jìn)行,而無(wú)需將數(shù)據(jù)從存儲(chǔ)器傳輸?shù)紺PU進(jìn)行處理,從而減少了數(shù)據(jù)傳輸?shù)难舆t和能耗。

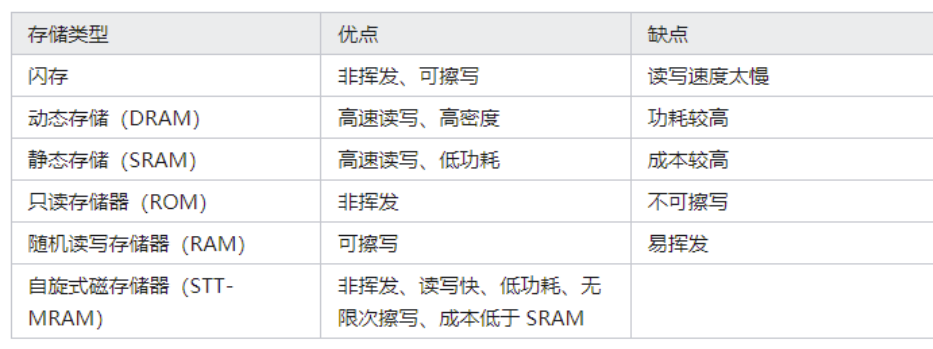

MRAM 與其他類(lèi)型存儲(chǔ)器相比具有明顯優(yōu)勢(shì)。下表列出幾種不同類(lèi)型的存儲(chǔ)器優(yōu)缺點(diǎn)比較:

通過(guò)將計(jì)算操作與存儲(chǔ)操作結(jié)合在一起,存算一體架構(gòu)可以實(shí)現(xiàn)更高效的數(shù)據(jù)處理。例如,對(duì)于機(jī)器學(xué)習(xí)應(yīng)用,可以在MRAM中進(jìn)行矩陣乘法等計(jì)算密集型操作,而無(wú)需將數(shù)據(jù)移動(dòng)到CPU或GPU。這樣可以大大減少數(shù)據(jù)傳輸?shù)臅r(shí)間和能耗,提高系統(tǒng)的整體性能。

此外,存算一體還可以降低硬件系統(tǒng)的復(fù)雜性,減少了CPU和存儲(chǔ)器之間的通信帶寬需求,簡(jiǎn)化了系統(tǒng)架構(gòu),降低了成本。

自旋芯片被認(rèn)為具有SRAM的高速度、DRAM的高密度以及Flash的非易失性等優(yōu)點(diǎn),這一觀點(diǎn)得到了中國(guó)科學(xué)院院士、南京大學(xué)物理系教授和博士生導(dǎo)師的認(rèn)同。此外,自旋芯片的抗輻射性也備受軍方青睞,使其原則上可以取代當(dāng)前各類(lèi)存儲(chǔ)器,成為未來(lái)的通用存儲(chǔ)器。

魯汶儀器的一位員工介紹稱(chēng),目前,MRAM主要在軍工、大數(shù)據(jù)高性能存儲(chǔ)等領(lǐng)域有一些應(yīng)用。然而,隨著工藝的成熟和成本的降低,MRAM有望取代DRAM。

然而歷史上在DRAM和Flash的發(fā)展過(guò)程中,一直有人認(rèn)為還有其他存儲(chǔ)芯片技術(shù)可以取代它們,但都沒(méi)有成功。趙巍勝認(rèn)為,DRAM和Flash將隨著新技術(shù)的引入不斷發(fā)展。例如,DRAM技術(shù)因?yàn)镋UV光刻機(jī)的使用而得以進(jìn)步。目前,MRAM在特定應(yīng)用場(chǎng)景下已經(jīng)有了一定的市場(chǎng)份額,如ToT、車(chē)載、航空航天等領(lǐng)域。然而,未來(lái)MRAM很有可能向新的消費(fèi)級(jí)市場(chǎng)發(fā)起沖擊。

四.SRAM 的存內(nèi)計(jì)算和于 MRAM 的存算一體探討

SRAM的存內(nèi)計(jì)算和基于MRAM的存算一體是兩種不同的計(jì)算模式,它們各自有著獨(dú)特的特點(diǎn)和優(yōu)勢(shì)。

SRAM的存內(nèi)計(jì)算:

工作原理:SRAM的存內(nèi)計(jì)算利用存儲(chǔ)單元的邏輯運(yùn)算功能,通過(guò)激活同一列的多個(gè)存儲(chǔ)單元來(lái)實(shí)現(xiàn)邏輯運(yùn)算。

優(yōu)勢(shì):

高密度和低功耗:相比傳統(tǒng)的SRAM陣列,新的SRAM存內(nèi)計(jì)算架構(gòu)具有更高的密度和更低的功耗,提供了更廣闊的發(fā)展空間。

邏輯運(yùn)算功能:SRAM存儲(chǔ)單元具有邏輯運(yùn)算功能,可以實(shí)現(xiàn)邏輯與非、邏輯或非、邏輯異或等邏輯運(yùn)算。

創(chuàng)新:研究者們提出了各種創(chuàng)新的SRAM存內(nèi)計(jì)算架構(gòu),如8T和10T SRAM單元,以及解耦讀寫(xiě)路徑等,進(jìn)一步提高了計(jì)算性能和能效。

基于MRAM的存算一體:

工作原理:基于MRAM的存算一體將計(jì)算和存儲(chǔ)功能結(jié)合在一起,利用MRAM的快速讀/寫(xiě)速度和非易失性,在存儲(chǔ)器內(nèi)部進(jìn)行計(jì)算操作。

優(yōu)勢(shì):

減少數(shù)據(jù)傳輸:由于計(jì)算任務(wù)可以直接在MRAM中進(jìn)行,無(wú)需將數(shù)據(jù)傳輸?shù)紺PU或GPU,因此可以減少數(shù)據(jù)傳輸?shù)难舆t和能耗。

降低系統(tǒng)復(fù)雜性:存算一體可以降低硬件系統(tǒng)的復(fù)雜性,簡(jiǎn)化系統(tǒng)架構(gòu),降低成本。

應(yīng)用前景:MRAM作為一種新型存儲(chǔ)技術(shù),在軍工、大數(shù)據(jù)高性能存儲(chǔ)等領(lǐng)域已經(jīng)有了一些應(yīng)用,并有望取代DRAM。

對(duì)比:

工作原理差異:SRAM的存內(nèi)計(jì)算主要利用存儲(chǔ)單元的邏輯運(yùn)算功能,而基于MRAM的存算一體則是將計(jì)算和存儲(chǔ)功能集成在MRAM中。

優(yōu)勢(shì)重點(diǎn)不同:SRAM存內(nèi)計(jì)算注重于提高計(jì)算性能和能效,而基于MRAM的存算一體則注重于減少數(shù)據(jù)傳輸延遲和降低系統(tǒng)復(fù)雜性。

應(yīng)用領(lǐng)域不同:SRAM存內(nèi)計(jì)算主要應(yīng)用于邏輯計(jì)算和神經(jīng)網(wǎng)絡(luò)硬件加速,而基于MRAM的存算一體則更多應(yīng)用于軍工、大數(shù)據(jù)高性能存儲(chǔ)等領(lǐng)域。

兩者各有特點(diǎn),適用于不同的場(chǎng)景和應(yīng)用需求。SRAM的存內(nèi)計(jì)算更適用于需要高性能邏輯計(jì)算和神經(jīng)網(wǎng)絡(luò)加速的場(chǎng)景,而基于MRAM的存算一體則更適用于減少數(shù)據(jù)傳輸延遲和簡(jiǎn)化系統(tǒng)架構(gòu)的場(chǎng)景。

五.總結(jié)

本文深入探討了基于SRAM和MRAM的存算一體技術(shù)在計(jì)算領(lǐng)域的應(yīng)用和發(fā)展。首先,介紹了基于SRAM的存內(nèi)邏輯計(jì)算技術(shù),包括其原理、優(yōu)勢(shì)以及在神經(jīng)網(wǎng)絡(luò)領(lǐng)域的應(yīng)用。其次,詳細(xì)討論了基于MRAM的存算一體技術(shù),包括其工作原理、優(yōu)勢(shì)以及在軍工和大數(shù)據(jù)存儲(chǔ)領(lǐng)域的應(yīng)用。最后,對(duì)比了SRAM的存內(nèi)計(jì)算和基于MRAM的存算一體技術(shù)的差異,包括工作原理、優(yōu)勢(shì)重點(diǎn)和應(yīng)用領(lǐng)域等方面。

在全文中,強(qiáng)調(diào)了這兩種技術(shù)在提高計(jì)算性能、降低能耗、簡(jiǎn)化系統(tǒng)架構(gòu)等方面的重要作用,展望了它們?cè)谖磥?lái)的計(jì)算應(yīng)用中的潛力和前景。同時(shí),對(duì)于不同場(chǎng)景下的適用性和優(yōu)勢(shì)進(jìn)行了詳細(xì)的分析和比較,為讀者提供了深入了解存內(nèi)計(jì)算技術(shù)的參考。

參考文獻(xiàn)

DRAM時(shí)代即將到來(lái),泛林集團(tuán)這樣構(gòu)想3D DRAM的未來(lái)架構(gòu)

3D DRAM Is Coming. Here’s a Possible Way to Build It.Benjamin Vincent

3D堆疊DRAM Cache的建模以及功耗優(yōu)化關(guān)鍵技術(shù)研究

存內(nèi)計(jì)算概述

中國(guó)科學(xué)技術(shù)大學(xué)

應(yīng)用于憶阻器陣列存內(nèi)計(jì)算的低延時(shí)低能耗新型感知放大器

基于存算一體集成芯片的大模型專(zhuān)用硬件架構(gòu)

高能效高安全新興計(jì)算芯片:現(xiàn)狀、挑戰(zhàn)與展望 54.01(2024):34-47.

校準(zhǔn)方法和存內(nèi)訓(xùn)練相結(jié)合的憶阻器神經(jīng)形態(tài)計(jì)算方法

Survey of In-Memory Computing Technology Based on SRAM and Non-Volatile Memory

審核編輯 黃宇

-

存儲(chǔ)器

+關(guān)注

關(guān)注

38文章

7641瀏覽量

166665 -

神經(jīng)網(wǎng)絡(luò)

+關(guān)注

關(guān)注

42文章

4811瀏覽量

103049 -

sram

+關(guān)注

關(guān)注

6文章

783瀏覽量

115737 -

MRAM

+關(guān)注

關(guān)注

1文章

236瀏覽量

32196 -

存內(nèi)計(jì)算

+關(guān)注

關(guān)注

0文章

32瀏覽量

1487

發(fā)布評(píng)論請(qǐng)先 登錄

存內(nèi)計(jì)算并不滿(mǎn)足于現(xiàn)有的算力

存內(nèi)生態(tài)構(gòu)建重要一環(huán)- 存內(nèi)計(jì)算工具鏈

存內(nèi)計(jì)算技術(shù)工具鏈——量化篇

存內(nèi)計(jì)算原理分類(lèi)——數(shù)字存內(nèi)計(jì)算與模擬存內(nèi)計(jì)算

知存科技再推存算一體芯片,用AI技術(shù)推動(dòng)助聽(tīng)器智能化

存內(nèi)計(jì)算WTM2101編譯工具鏈 資料

知存科技助力AI應(yīng)用落地:WTMDK2101-ZT1評(píng)估板實(shí)地評(píng)測(cè)與性能揭秘

三星基于HMB的存內(nèi)計(jì)算芯片有何亮點(diǎn)?

?什么是存內(nèi)計(jì)算

2023年存算一體是芯片設(shè)計(jì)的技術(shù)趨勢(shì)

特斯拉的下一代AI芯片:存算一體

存算一體技術(shù)發(fā)展現(xiàn)狀和未來(lái)趨勢(shì)

直播預(yù)約 |開(kāi)源芯片系列講座第24期:SRAM存算一體:賦能高能效RISC-V計(jì)算

知存科技啟動(dòng)首屆存內(nèi)計(jì)算創(chuàng)新大賽

開(kāi)源芯片系列講座第24期:基于SRAM存算的高效計(jì)算架構(gòu)

評(píng)論