TTL三態(tài)門電路的輸出狀態(tài)

TTL(晶體管-晶體管邏輯)三態(tài)門是一種特殊類型的數(shù)字邏輯門,它具有三種輸出狀態(tài):高電平、低電平和高阻抗?fàn)顟B(tài)(也稱為三態(tài)或高阻態(tài))。三態(tài)門的設(shè)計(jì)允許它在不輸出任何信號時(shí)不會影響到總線上的其他設(shè)備,這使得多個(gè)設(shè)備可以共享同一通信總線。

TTL三態(tài)門的基本工作原理

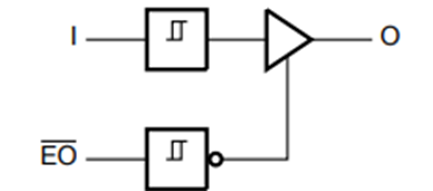

TTL三態(tài)門通常由一個(gè)或多個(gè)TTL邏輯門和一個(gè)額外的控制機(jī)制組成,這個(gè)控制機(jī)制負(fù)責(zé)將輸出置于高阻抗?fàn)顟B(tài)。在最基本的形式中,一個(gè)TTL三態(tài)緩沖器可以簡化為一個(gè)非門(NOT gate)和一個(gè)控制輸入。

輸出狀態(tài)詳解

- 高電平輸出 :當(dāng)控制信號被激活(通常是低電平有效),三態(tài)門將允許其內(nèi)部邏輯門的輸出被驅(qū)動到輸出端。如果內(nèi)部邏輯為非門,那么輸入信號的反相將被驅(qū)動到輸出。

- 低電平輸出 :與高電平輸出類似,當(dāng)控制信號被激活時(shí),如果內(nèi)部邏輯狀態(tài)為低,則輸出也將為低。

- 高阻抗?fàn)顟B(tài)(三態(tài)) :當(dāng)控制信號不被激活(通常是高電平有效),三態(tài)門的輸出將進(jìn)入高阻抗?fàn)顟B(tài)。在這種狀態(tài)下,輸出端不驅(qū)動任何信號,相當(dāng)于開路。這允許其他設(shè)備控制總線,而不會受到這個(gè)三態(tài)門的影響。

TTL三態(tài)門的控制方式

控制三態(tài)門輸出狀態(tài)的是使能信號,它可以是主動低(當(dāng)使能信號為低電平時(shí)允許輸出)或主動高(當(dāng)使能信號為高電平時(shí)允許輸出)。這個(gè)使能信號通常由一個(gè)單獨(dú)的邏輯電路或控制邏輯提供。

-

TTL

+關(guān)注

關(guān)注

7文章

510瀏覽量

70980 -

晶體管

+關(guān)注

關(guān)注

77文章

9881瀏覽量

139804 -

三態(tài)門

+關(guān)注

關(guān)注

1文章

34瀏覽量

18918 -

門電路

+關(guān)注

關(guān)注

7文章

200瀏覽量

40456

發(fā)布評論請先 登錄

相關(guān)推薦

SN74AVC2T244的使能引腳OE到底是OE=低電平時(shí)輸出三態(tài),還是OE=高電平時(shí)輸出三態(tài)?

非門電路的輸入端電阻模式怎么設(shè)置電平狀態(tài)

TTL門電路的基本概念、工作原理及特性參數(shù)

三態(tài)緩沖器在計(jì)算機(jī)中的應(yīng)用

三態(tài)緩沖器的工作原理和應(yīng)用

三態(tài)邏輯電路的工作原理及其四種三態(tài)緩沖器介紹

評論