采用一個4納米厚的鋁酸鑭(lanthanum aluminate)層作為超薄介質(zhì),以及0.5納米厚的氧化鋁層,美國普杜大學(xué)(Purdue University)的銦砷化鎵(IGA)納米晶體管終于達到了一個重要的20納米門限(gate size)的里程碑。當前英特爾公司為其Ivy Bridge硅基晶體管使用的是22納米的制程。

一系列的“4-D”晶體管[圖像來源:普杜大學(xué)]

新的銦砷化鎵(IGA0晶體管像是英特爾的鰭狀3D晶體管,采用了三維門的設(shè)計,但它還更往前邁進了一步,造出了一個奇異可折疊的三重圓錐形納米線設(shè)計,使之看起來更像一棵小松樹。

普杜大學(xué)電氣和計算機工程系的Peide “Peter” Ye教授,為他的新裝置取了一個有趣的名字——“4D晶體管”。

他評價說,“一個單層的房子可住不了那么多人,但是更多的樓層可以容納更多的人,而晶體管也是一樣的。把它們堆疊在一起,可以實現(xiàn)高速的運算所需的更大電流和更快的操作。而這添加了全新的維度,因此我稱之為四維的。新晶體管優(yōu)越的電子遷移率將允許更新穎的設(shè)計,且其繼任者可以更加雄心勃勃。”

目前的硅芯片制造業(yè)處于不確定的狀態(tài)。預(yù)計芯片會在2015達到14nm,研究人員希望到2018年的時候能收縮到10nm。但在14nm之前,繼續(xù)使用當前的“高K”(high-k)介質(zhì)將導(dǎo)致嚴重的泄露電流,因此停留在常規(guī)的道路上的課程研究者們必須展開發(fā)現(xiàn)新電介質(zhì)的競賽。

制程要越過10nm將更加棘手,因為它已經(jīng)把光刻技術(shù)推到了很勉強的邊界。像自組裝(self-assembly)或機械操縱原子(mechanical manipulation)這樣的先進技術(shù)或許能證實10nm以下的關(guān)鍵功能尺寸。

-

納米晶體管

+關(guān)注

關(guān)注

0文章

10瀏覽量

6163

發(fā)布評論請先 登錄

相關(guān)推薦

四維圖新接盤滴滴智駕及座艙資產(chǎn)

四維智聯(lián)計劃購入滴滴智駕座艙業(yè)務(wù)

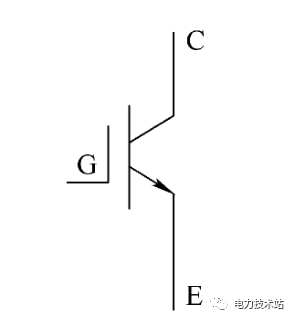

什么是單極型晶體管?它有哪些優(yōu)勢?

什么是NPN型和PNP型晶體管

PNP晶體管符號和結(jié)構(gòu) 晶體管測試儀電路圖

晶體管功率繼電器的基本介紹

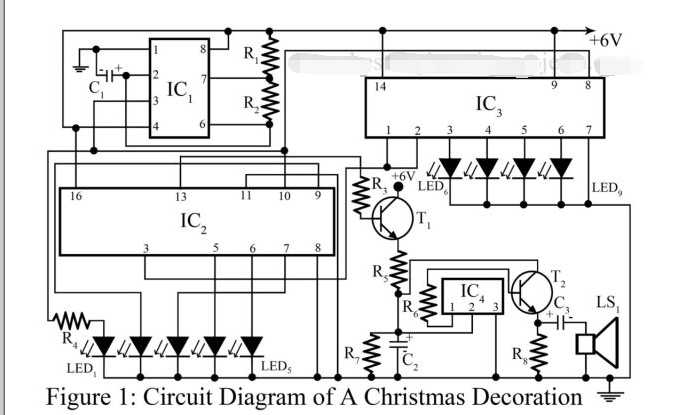

圣誕樹燈電路圖分享

如何提高晶體管的開關(guān)速度,讓晶體管快如閃電

晶體管計算機的主要物理元件為

在特殊類型晶體管的時候如何分析?

有什么方法可以提高晶體管的開關(guān)速度呢?

絕緣柵雙極型晶體管是什么

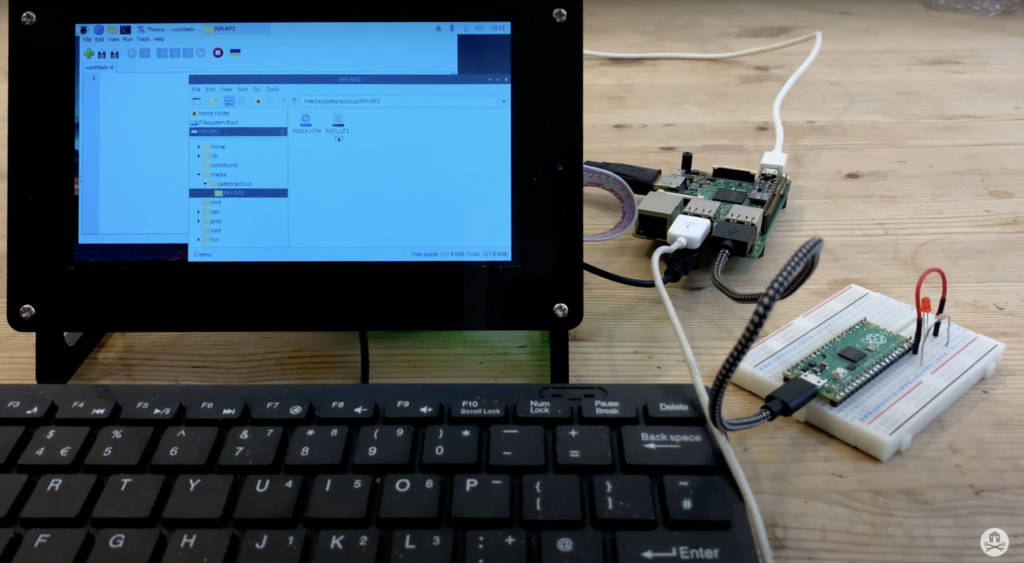

用于室內(nèi)植物或圣誕樹的 Raspberry Pi Pico 水監(jiān)控器

可以提升計算速度的20nm圣誕樹型“四維”晶體管

可以提升計算速度的20nm圣誕樹型“四維”晶體管

評論