一、 阻抗匹配電路的作用

二、 阻抗匹配的理想模型

三、 電感電容的高頻特性

四、 Smith圓圖在RF匹配電路調(diào)試中的應用

五、 RF匹配電路調(diào)試的注意事項

六、 小結(jié)

一、 阻抗匹配電路的作用

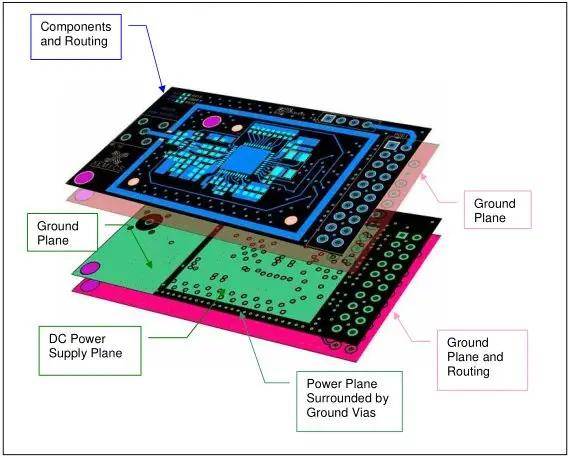

阻抗控制在硬件設(shè)計中是一個比較重要的環(huán)節(jié),IC廠商針對其應用一般會向終端產(chǎn)商提供PCB板材質(zhì)、PCB疊層、PCB板厚等一些相關(guān)參考設(shè)計建議(這些都是跟PCB阻抗控制設(shè)計息息相關(guān)的),終端廠商在拿到這些資料后,會結(jié)合實際情況據(jù)此進行本地化的設(shè)計調(diào)整,然后將相關(guān)設(shè)計資料及要求提供給PCB的生產(chǎn)廠家進行PCB生產(chǎn)。

針對不同信號系統(tǒng)有不同的特征阻抗值,比如75ohm、100ohm、90ohm、50ohm等,而對頻率較高的RF信號來講,最常見的是50ohm的阻抗控制。

在實際的PCB設(shè)計中,RF傳輸線通常都會采用微帶線和帶狀線的走線方式, 且需要選取參考層來進行阻抗控制。考慮到芯片的RF特性、實際PCB生產(chǎn)工藝、及元器件用料的因素,除了需進行PCB RF傳輸線的阻抗控制外,在硬件設(shè)計上通常還需添加一些匹配網(wǎng)絡(luò)電路用作RF的調(diào)試,一般說來,其作用大概為以下幾種:

1、諧振頻率以及帶寬的調(diào)整

2、功率、EVM、ACLR、PA電流、傳導雜散和輻射雜散等指標的調(diào)試等

圖1 某IC廠商建議的4-layer層疊方式

二、 阻抗匹配的理想模型

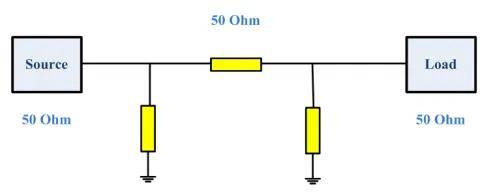

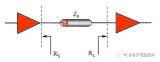

射頻工程師大都遇到過匹配阻抗的問題,通俗的講,阻抗匹配的目的是確保能實現(xiàn)信號或能量從“信號源”到“負載”的有效傳送,其最最理想模型當然是希望Source端的輸出阻抗為50歐姆,傳輸線的阻抗為50歐姆,Load端的輸入阻抗也是50歐姆,一路50歐姆下去,這是最理想的。

圖2 理想阻抗傳輸

然而實際情況是:源端阻抗不會是50ohm,負載端阻抗也不會是50ohm,這個時候就需要若干個阻抗匹配電路,而匹配電路就是由電感和電容所構(gòu)成,這個時候我們就需要使用電容和電感來進行阻抗匹配電路調(diào)試,以達到RF性能最優(yōu)。

三、 電感電容的高頻特性

要用電感電容解決高頻的性能問題,那我們就需要先了解下電容和電感這些器件在高頻的特性。

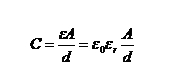

翻一翻以前的物理課本,對電容器,是用平板表面積與平板間距的比值來定義其容量:

(A代表平板表面積,d代表平板間距,理想情況下在平板間沒有電流流動)

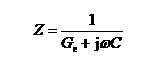

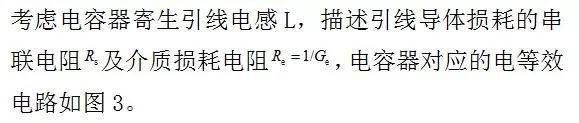

但在高頻信號通過時,電容器平板間的實際電介質(zhì)存在損耗(也就是板間有傳導電流流動),所以,電容器的阻抗需要表示成電導和電納的并聯(lián)組合:

圖3 高頻電容等效電路

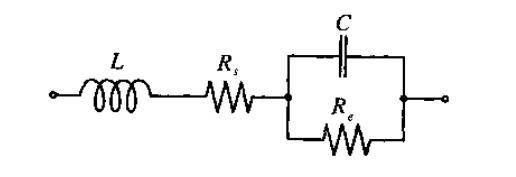

而對電感而言,在射頻電路中經(jīng)常使用的電感為線圈結(jié)構(gòu),其線圈是用導線在圓柱體上繞制而成,線圈除了具有與頻率無關(guān)的電阻之外,它還存在一個“電感”,而臨近的繞圈間存在著分離的移動電荷,所以它還存在一個寄生旁路“電容”。

圖4 高頻電感等效電路

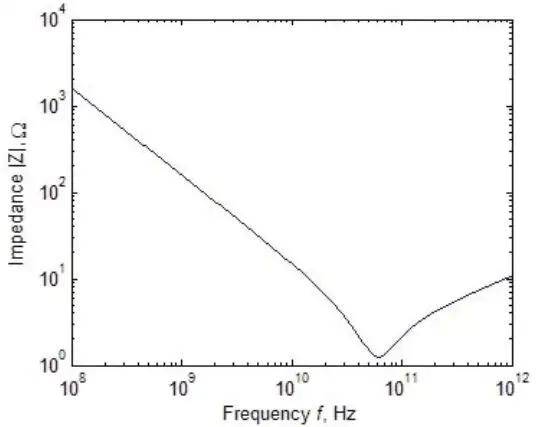

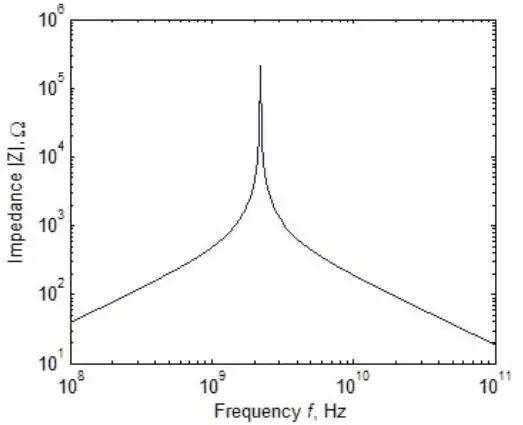

在高頻時,電容器中的電介質(zhì)產(chǎn)生了損耗,所以電容器在諧振點前,呈現(xiàn)的阻抗特性與頻率成反比;而對電感器而言,當頻率接近諧振點時,高頻電感的阻抗迅速提高,當頻率繼續(xù)提高時,寄生電容C的影響成為主要的,線圈阻抗逐漸降低。

所以,一個實際電感或者電容并不能簡單用電感量或電容量來衡量,而應該將其當成寄生旁路電容C、串聯(lián)電阻R、寄生電感L的綜合效應,這個時候通過一個等效網(wǎng)絡(luò)去模擬要更為合理,當然,具體使用時,有時還需考慮集總參數(shù)和分布參數(shù)電路模型。

圖5 高頻電容阻抗頻率曲線

圖6 高頻電感阻抗頻率曲線

四、 Smith圓圖在RF匹配電路調(diào)試中的應用

說完電感、電容的高頻特性,接著我們來看看Smith圓圖。

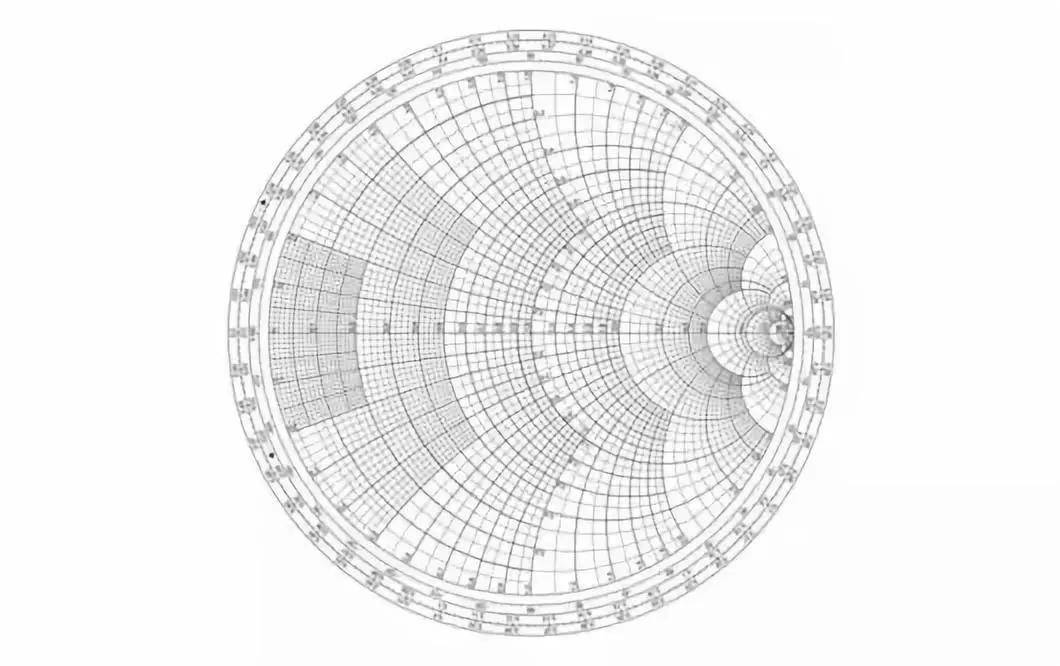

Smith圓圖上可以反映出如下信息:阻抗參數(shù)Z,導納參數(shù)Y,品質(zhì)因子Q,反射系數(shù),駐波系數(shù),噪聲系數(shù),增益,穩(wěn)定因子,功率,效率,頻率信息等抗等參數(shù)。

圖5 Simth圓圖

是不是一臉懵,我們還是來看阻抗圓圖吧:

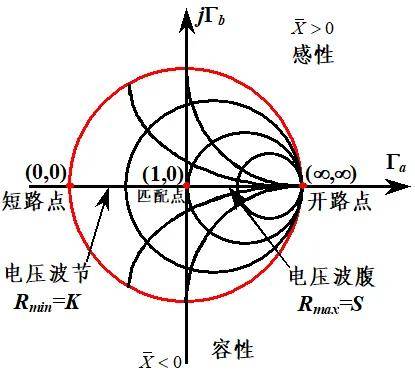

圖6 阻抗圓圖

阻抗圓圖的構(gòu)圖原理是利用輸入阻抗與電壓反射系數(shù)之間的一一對應關(guān)系,將歸一化輸入阻抗表示在反射系數(shù)極坐標系中,其特點歸納如下:

1.上半圓阻抗為感抗,下半圓阻抗為容抗;

2.實軸為純電阻,單位圓為純電抗;

3.實軸的右半軸皆為電壓波腹點(除開路點),左半軸皆為電壓波節(jié)點(除短路點);

4.匹配點(1,0),開路點(∞,∞)和短路點(0,0);

5.兩個特殊圓:最大的為純電抗圓,與虛軸相切的為匹配圓;

6.兩個旋轉(zhuǎn)方向:逆時針轉(zhuǎn)為向負載移動,順時針轉(zhuǎn)為向波源移動。

導納圓圖與阻抗圓圖互為中心對稱,同一張圓圖,即可以當作阻抗圓圖來用,也可以當作導納圓圖來用,但是在進行每一次操作時,若作為阻抗圓圖用則不能作為導納圓圖。

Smith圓圖中,能表示出一些很有意思的特征:

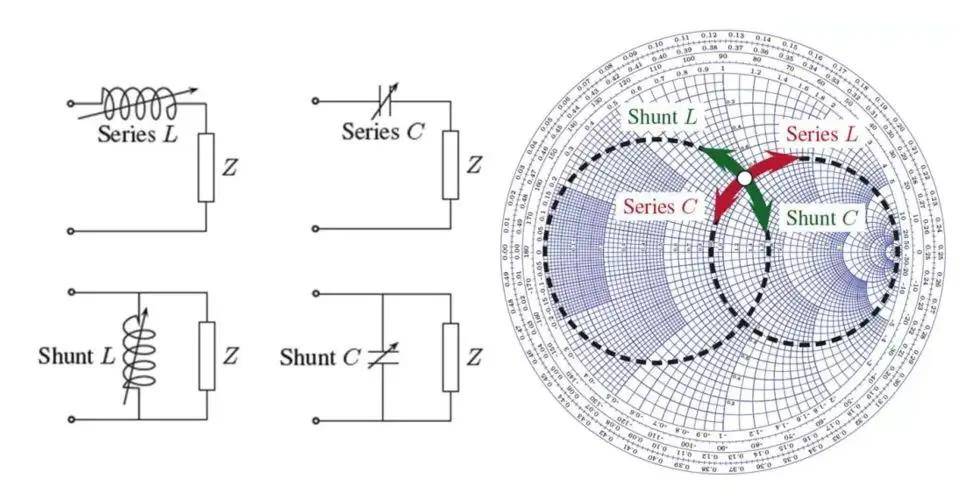

在負載之前串聯(lián)或并聯(lián)一個可變電感/電容,電路圖如圖7左側(cè)4個圖所示,將得到Smith圓圖上右側(cè)的幾條曲線。對應Smith阻抗圓及導納圓,其運動軌跡如下:

1、使用Smith阻抗圓時,串聯(lián)電感順時針轉(zhuǎn),串聯(lián)電容逆時針轉(zhuǎn);

2、使用Smith導納圓時,并聯(lián)電感,逆時針轉(zhuǎn),并聯(lián)電容順時針轉(zhuǎn)。

圖7 聯(lián)接集中元件,Smith軌跡變化規(guī)律

五、 匹配電路調(diào)試的注意事項

以上串并聯(lián)元件對應的smith圖上的運動軌跡可作為調(diào)試的參考及對結(jié)果的初步判斷,而至于RF匹配電路實際調(diào)試過程中的注意事項,一般而言有五項:

1 .電感/電容值不要過小,原因是要維持匹配的穩(wěn)定性,因為電感/電容值會有誤差,以電容為例子,大概有±0.1pF的誤差,如果是一個容值為 0.3pF的電容,則誤差高達33%,其容值范圍為0.2pF~0.4pF,這可能會導致每片PCB的Tx/Rx Performance不一致,進而影響工廠量產(chǎn)時的良率。

2. 落地電容值不要過大,是因為依照容抗公式:

電容值越大,容抗越小,因此落地電容值過大,則可能會讓信號都流到地端。

3.電感/電容值不要過于冷門,原因是方便備料。若是常見的值,則所有廠家都會有,量產(chǎn)過程中,避免出現(xiàn)廠家缺料的情況。

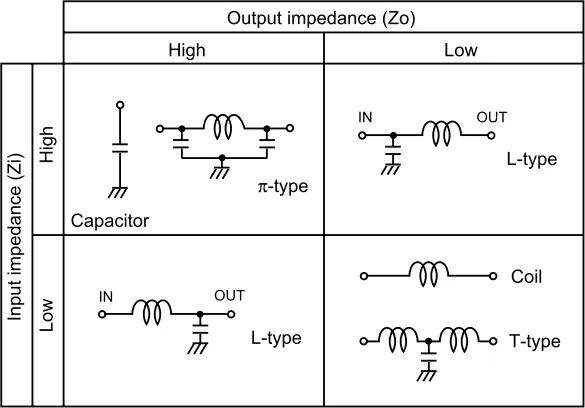

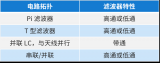

4.盡可能設(shè)計成Low Pass Filter,原因是這樣可以抑制諧波。常用的 Low Pass Filter的組合如下:

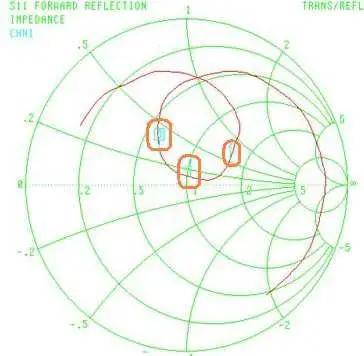

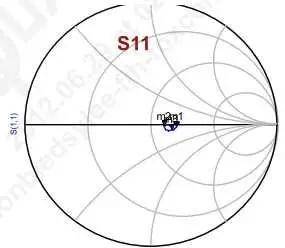

圖8 Low Pass Filter組合

5. 對一般消費電子產(chǎn)品而言,匹配電路整個頻帶的smith原圖軌跡需落在VSWR=2的圓內(nèi),且其整個頻帶的阻抗軌跡盡可能收斂,這是最重要的原則,上述步驟,是以單一頻率點來做匹配,但最后看整個頻率范圍內(nèi)的Smith Chart軌跡,才能決定這一組匹配值可否采用。(如圖9和圖10)

圖9 Smith Chart軌跡

圖10 Smith Chart軌跡

六、 小結(jié)

對于靠近PA或者DUP等射頻前端器件的匹配網(wǎng)絡(luò)大家都會預留,但在一些物聯(lián)網(wǎng)產(chǎn)品設(shè)計中,由于產(chǎn)品尺寸較小又需要設(shè)計PCB板載天線,有些工程師為了節(jié)省空間而省掉了靠近天線端的匹配網(wǎng)絡(luò),從而導致在RF性能的優(yōu)化過程中或者認證要求的雜散測試中束手無策,造成產(chǎn)品開發(fā)周期加長或者硬件設(shè)計的改版,得不償失。

因此,在實際的電路設(shè)計中,還是建議預留匹配電路,不管是射頻前端還是后端的部分。

另外,還存在這樣的一種可能,在將靠近天線端的匹配網(wǎng)絡(luò)作為“天線”的一部分進行調(diào)試時,雖然駐波比得到了優(yōu)化,但天線系統(tǒng)的效率反而會降低。所以,在整機環(huán)境較為惡劣的情況下,僅僅想依靠匹配網(wǎng)絡(luò)的調(diào)整去提升整機的無線性能會有一定的難度,而且會存在雜散超標的風險。

調(diào)整匹配電路雖然能降低反射,但同樣會引入損耗,為了優(yōu)化性能多增加元器件,還有可能在生產(chǎn)制程上增加一些SMT issue的風險。

審核編輯 黃宇

-

天線

+關(guān)注

關(guān)注

68文章

3196瀏覽量

140782 -

阻抗

+關(guān)注

關(guān)注

17文章

957瀏覽量

45914

發(fā)布評論請先 登錄

相關(guān)推薦

Cadence技術(shù)解讀 天線的阻抗匹配技術(shù)

請問運放正向端和反相端阻抗匹配有什么影響,是否跟運放的某些性能指標相關(guān)?

在阻抗匹配中50歐姆好像是一個很特殊的值,為什么呢?

PCB阻抗匹配過孔的多個因素你知道哪些?

什么是阻抗?為什么要做阻抗匹配?

輸入阻抗、輸出阻抗、阻抗匹配到底是個啥?

高速差分信號阻抗匹配詳解

阻抗匹配的原理分析?

光纖溫度傳感器測試阻抗匹配器內(nèi)部溫度技術(shù)方案

無源探頭的阻抗匹配如何操作

PCB板設(shè)計與制造之阻抗匹配和零歐姆電阻解析

為什么要阻抗匹配?怎么進行阻抗匹配?

阻抗匹配有煩惱?來嘮一嘮~

阻抗匹配有煩惱?來嘮一嘮~

評論