近日,IEEE電子元件與技術會議(ECTC,IEEE Electronic Components and Technology Conference,https://ectc.net/)的研究人員推動了這項技術的發展,這項技術對尖端處理器和存儲器至關重要。這項技術被稱為混合鍵合,它將兩個或多個芯片堆疊在同一封裝中,使芯片制造商能夠增加處理器和存儲器中的晶體管數量,盡管曾經定義摩爾定律的傳統晶體管收縮速度普遍放緩。來自主要芯片制造商和大學的研究小組展示了各種艱難的改進,其中一些——包括Applied Materials公司、Imec、英特爾和索尼——顯示的結果可能會導致3D堆疊芯片之間的連接密度創紀錄,每平方毫米硅中約有700萬個鏈路。

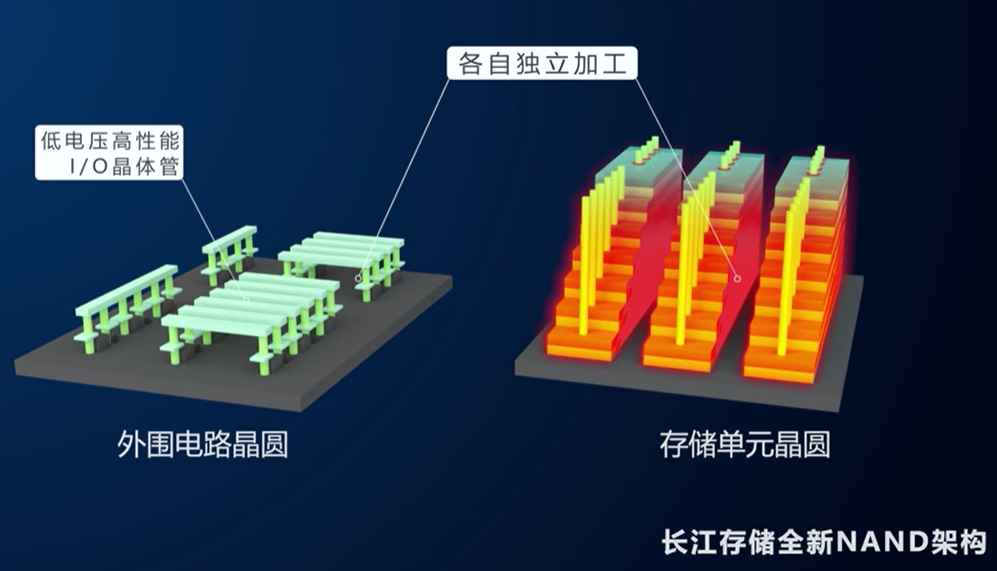

英特爾的Yi Shi告訴ECTC的工程師,由于半導體進步的新性質,所有這些連接都是必要的。正如英特爾技術開發總經理Ann Kelleher在2022年向IEEE Spectrum解釋的那樣,摩爾定律現在由一個稱為系統技術協同優化(STCO,system technology co-optimization)的概念所支配。在STCO中,芯片的功能(例如緩存、輸入/輸出和邏輯)被分離出來,并使用最佳的制造技術進行制造。混合鍵合和其他先進的封裝技術可以將它們重新組裝,使它們像一塊硅一樣工作。但只有高密度的連接才能實現這一點,這種連接可以在幾乎沒有延遲或能耗的情況下在硅片之間傳送比特。

混合鍵合并不是目前唯一一種先進的封裝技術,但它提供了最高密度的垂直連接。Besi公司技術高級副總裁Chris Scanlan表示,混合鍵合在ECTC上占據主導地位,約占所展示研究的五分之一,該公司的工具是多項突破的幕后推手。

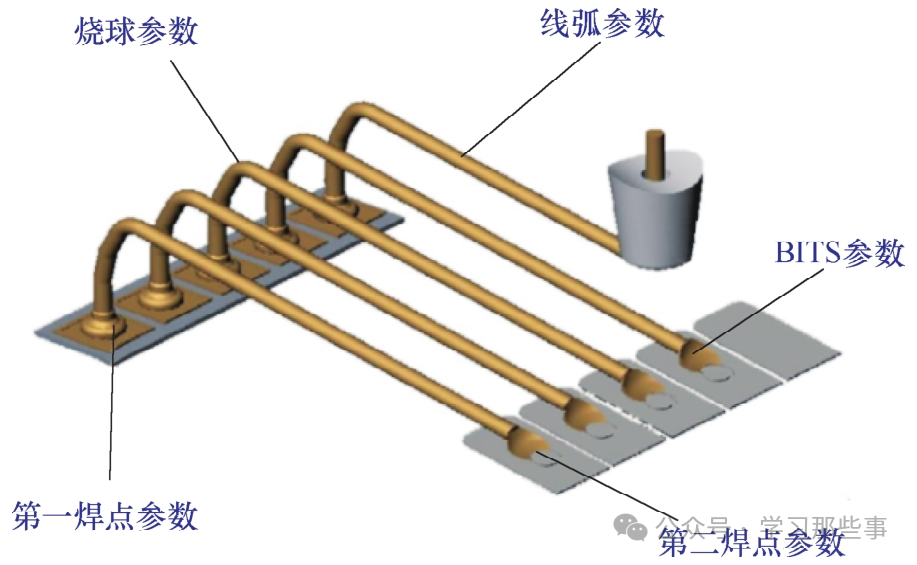

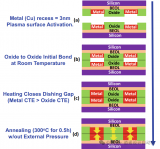

在混合鍵合中,銅焊盤構造在每個芯片的頂面上。銅被絕緣層(通常是氧化硅)包圍,焊盤本身略微凹進絕緣層表面。氧化物經過化學改性后,將兩個芯片面對面壓在一起,使凹進的焊盤相互對齊。然后慢慢加熱這個夾層,使銅膨脹到間隙處,連接兩個芯片。

混合鍵合既可以將單個芯片連接到一個裝滿更大尺寸芯片的晶圓上,也可以用于將兩個裝滿相同尺寸芯片的晶圓粘合在一起,后者比前者更為成熟,部分原因是它在相機芯片中的應用。例如,Imec報道了一些有史以來密度最高的晶圓對晶圓(WoW)鍵合,鍵合距離(或間距)僅為400納米。同一研究中心在芯片對晶圓 (CoW) 場景中實現了 2 微米間距。(當今商用芯片的連接間距約為 9 微米。)

法國研究機構CEA Leti集成與封裝科學負責人Jean-Charles Souriau表示:“有了現有的設備,晶圓對晶圓比對芯片對晶圓更容易,大多數微電子工藝都是針對 [整片] 晶圓進行的。”然而,在AMD的Epyc系列等高端處理器中,芯片對晶片(或芯片對晶片)引起了轟動,該技術用于在其先進的CPU和人工智能加速器中組裝計算核心和緩存。

為了推動兩種方案的間距越來越緊密,研究人員專注于使表面稍微平坦一些,使粘合的晶圓更好地粘在一起,并減少整個過程的時間和復雜性。做好這一切最終可能意味著芯片設計方式的革命。

在報告中,我們看到了最緊密間距(500納米至360納米)的晶圓對晶圓 (WoW) 研究,它們都在一件事上投入了大量精力:平整度。要以100納米級的精度將兩片晶圓結合在一起,整個晶圓必須幾乎完全平整。如果它彎曲或扭曲,整個材料部分就無法連接。

平整晶圓是一種稱為化學機械平坦化(CMP,chemical mechanical planarization)的工藝。這通常是芯片制造的關鍵,尤其是對于在晶體管上方生產互連層的工藝部分。

Souriau說:“CMP是我們必須控制混合鍵合的一個關鍵參數。”近日在ECTC上公布的結果將CMP提升到了另一個水平,不僅使整個晶片變平,而且只減少了銅焊盤之間絕緣層上的納米圓度,以確保更好的連接。

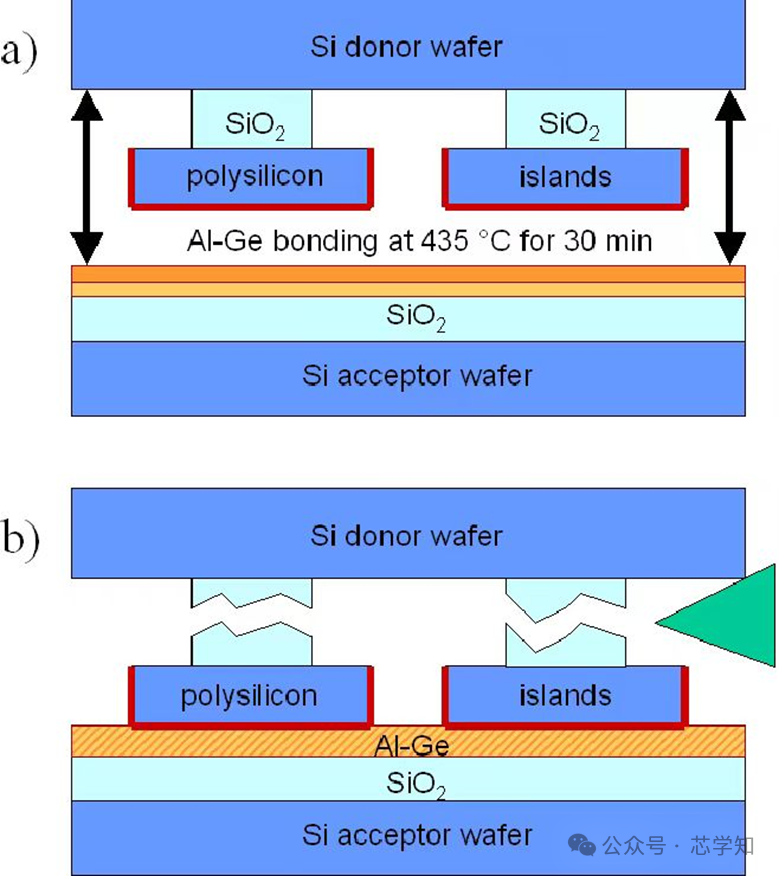

其他研究的重點是通過實驗不同的表面材料,如碳氮化硅而不是氧化硅,或者使用不同的方案來化學激活表面。最初,當晶圓或芯片被壓在一起時,它們會通過相對較弱的氫鍵固定在一起,而重點是確保在粘合和后續步驟之間一切都保持原位。然后,粘合的晶圓和芯片會慢慢加熱(這一過程稱為退火),以形成更強的化學鍵。這些鍵到底有多強——以及如何弄清楚——是ECTC大量研究的主題。

最終的鍵合強度也部分來自于銅連接。退火步驟使銅擴展穿過間隙以形成導電橋。三星的Seung Ho Hahn解釋說,控制這種差距的大小是關鍵。間隙太大,銅無法連接。太少會把晶圓推開。這是一個納米的問題,Hahn報道了一種新的化學工藝的研究,希望通過一次蝕刻掉一個原子層的銅來實現這一目標。

連接的質量也很重要。即使在銅膨脹之后,大多數方案也表明金屬的晶粒邊界不會從一側跨越到另一側。這種跨越降低了連接的電阻,并應能提高其可靠性。日本東北大學的研究人員報告了一種新的冶金方案,該方案最終可以生成跨越邊界的大型單晶銅。“這是一個巨大的變化,” 東北大學副教授 Takafumi Fukushima說,“我們現在正在分析其背后的原因。”

其他實驗集中在簡化混合鍵合過程上。一些人試圖降低形成鍵所需的退火溫度——通常在300°C左右——這是因為有可能降低長期加熱對芯片造成損壞的風險。Applied Materials公司的研究人員介紹了一種從根本上減少退火時間的方法的進展——從幾個小時減少到5分鐘。

晶圓上芯片(CoW) 混合鍵合目前對工業界更有用:它允許芯片制造商將不同大小的芯片堆疊在一起,并在將每個芯片綁定到另一個芯片之前對其進行測試,確保它們不會因單個有缺陷的部件而導致昂貴的CPU發生致命故障。

但CoW具有WoW的所有困難,而且緩解困難的選項較少。例如,CMP旨在使晶圓平整,而不是使單個芯片平整。一旦芯片從源晶圓上切下并經過測試,就很難再提高其鍵合準備度。

盡管如此,英特爾報告稱,CoW混合鍵間距為3μm,而Imec則實現了2μm,主要是通過在轉移的管芯仍附著在晶片上時使其非常平坦,并保持其在后續過程中格外清潔來實現的。兩個小組的工作都使用了等離子體蝕刻來切割模具,而不是通常使用專用刀片的方法。等離子不會導致邊緣碎裂,從而產生干擾連接的碎屑。它還允許Imec團隊塑造芯片,制作倒角,以減輕可能破壞連接的機械應力。

幾位研究人員告訴IEEE Spectrum,CoW混合鍵合將對高帶寬存儲器(HBM,high-bandwidth memory)的未來至關重要。HBM是控制邏輯芯片頂部的DRAM芯片堆棧,目前高度為8到12個芯片。HBM通常與高端GPU放在同一個封裝中(https://spectrum.ieee.org/intel-gaudi-3),對于提供運行ChatGPT等大型語言模型所需的海量數據至關重要。如今,HBM芯片采用所謂的微凸塊技術堆疊,其中每層之間的微小焊球被有機填充物包圍。

但隨著人工智能將內存需求推得更高,DRAM制造商希望在HBM芯片上做20層或更多。然而,微凸塊占用的體積意味著這些堆棧很快就會太高,無法與GPU一起封裝。混合鍵合不僅可以縮小HBM的高度,還可以使封裝中的多余熱量更容易排出,因為其層之間的熱阻更小。

在ECTC,三星的工程師展示了混合鍵合方案可以制作16層HBM堆疊。三星的高級工程師Hyeonmin Lee說:“我認為使用這種技術可以制造20層以上的堆疊。”

其他新的CoW技術可能有助于為高帶寬存儲器帶來混合綁定。Souriau說,盡管他們沒有在ECTC進行這方面的研究,但CEA Leti的研究人員正在研究所謂的自對準技術。這將有助于使用化學過程確保CoW連接。每個表面的某些部分將變得疏水,某些部分將變得親水,從而使表面能夠自動滑入到位。

在ECTC,日本東北大學和雅馬哈機器人公司的研究人員報告了類似方案的研究,利用水的表面張力在實驗性DRAM芯片上對準5微米焊盤,精度優于50納米。

混合鍵合能走多遠?

研究人員幾乎肯定會繼續推動混合鍵合連接的發展。臺灣半導體制造有限公司(Taiwan Semiconductor Manufacturing Co.)的探索項目經理Han-Jong Chia告訴ECTC的工程師,200納米的WoW間距不僅是可能的,也是可取的。臺積電計劃在兩年內推出一種名為“背面供電”的技術(https://spectrum.ieee.org/next-gen-chips-will-be-powered-from-below)。(英特爾計劃在今年年底推出)這項技術將芯片的大塊功率傳輸互連置于硅下方,而不是硅上方。臺積電研究人員計算,有了這些互連,最高層的互連可以更好地連接到更小的混合鍵合焊盤。采用200納米鍵合焊盤的背面供電將大幅降低3D連接的電容,以至于能效和信號延遲的乘積將是400納米鍵合焊盤所能實現的乘積的九倍。

Chia表示,在未來的某個時候,如果鍵距進一步縮小,那么“折疊”電路塊使其跨兩個晶圓構建可能變得切實可行。這樣,塊內的一些較長的連接可能會通過垂直路徑縮短,從而有可能加快計算速度并降低功耗。

并且混合鍵合可能不限于硅。CEA Leti的Souriau表示:“如今硅對硅晶圓的開發取得了很大進展,但我們也在尋求在氮化鎵和硅晶圓以及玻璃晶圓之間進行混合鍵合……一切都在一切之上。”他的組織甚至提出了量子計算芯片混合鍵合的研究,包括排列和鍵合超導鈮而不是銅。

“很難說極限在哪里,”Souriau 說,“事情發展得太快了。”

審核編輯:彭菁

-

芯片

+關注

關注

459文章

52192瀏覽量

436260 -

機械

+關注

關注

8文章

1667瀏覽量

41424 -

晶圓

+關注

關注

52文章

5124瀏覽量

129169 -

人工智能

+關注

關注

1804文章

48717瀏覽量

246544

原文標題:混合鍵合在3D芯片中扮演主角

文章出處:【微信號:IEEE_China,微信公眾號:IEEE電氣電子工程師】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

混合鍵合市場空間巨大,這些設備有機會迎來爆發

閃存沖擊400層+,混合鍵合技術傳來消息

三維堆疊封裝新突破:混合鍵合技術揭秘!

混合鍵合技術:開啟3D芯片封裝新篇章

評論