利用 Cadence Janus NoC,設計團隊可更快獲得更好的 PPA 結果,降低設計風險,節約寶貴的工程資源,傾力打造 SoC 的差異化功能

中國上海,2024 年 7 月 1 日 —— 楷登電子(美國 Cadence 公司,NASDAQ:CDNS)近日宣布擴充其系統 IP 產品組合,新增了 Cadence? Janus? Network-on-Chip(NoC)。隨著當今計算需求的不斷提高,更大、更復雜的系統級芯片(SoC)和分解式多芯片系統在市場上迅速普及,硅組件內部和硅組件之間的數據傳輸變得越來越具有挑戰性,功率、性能和面積(PPA)受到了影響。Cadence Janus NoC 能夠以極低的延遲高效管理這些同步高速通信,幫助客戶以更低的風險更快地實現其 PPA 目標。

“Cadence 是 IP 和設計質量領域備受信賴的領導者,我們將繼續加大投入,提升我們的基礎接口和處理器 IP、系統 IP、軟件和設計服務能力,幫助客戶開發差異化的分解式設計。”Cadence 高級副總裁兼芯片解決方案事業部總經理 Boyd Phelps 表示,“我們不斷擴充的系統 IP 產品組合迎來了新的成員——Cadence Janus NoC,這是這一戰略的重要里程碑。我們從 IP 提供商成長為 SoC 設計合作伙伴,為客戶帶來了更大的價值,使他們能夠集中寶貴的工程資源,專注于實現芯片的差異化設計。”

Cadence Janus NoC 依托 Cadence 值得信賴且久經考驗的 Tensilica? RTL 生成工具。客戶可以使用 Cadence 廣泛的軟硬件產品組合對其 NoC 進行軟件仿真和硬件仿真,并使用 Cadence 的系統性能分析工具(SPA)深入了解 NoC 的性能。該流程支持架構探索,有助于實現可滿足產品需求的最佳 NoC 設計。NoC 依托 Cadence 在 IP 和設計質量領域久負盛名的領導地位,由客戶滿意度遙遙領先的技術團隊提供技術支持。

Cadence Janus NoC 可有效應對與當今復雜的 SoC 互連相關的布線擁塞和時序問題,這些問題在物理實現之前往往并不明顯。Cadence 的第一代 NoC 不僅能滿足當前最迫切的需求,還提供了一個有利于未來的創新平臺,例如支持行業標準存儲器和 I/O 一致性協議。目前該產品提供的功能和優勢包括:

·易于使用:Cadence 擁有功能強大、設計先進的圖形用戶界面(GUI),可輕松支持從小型子系統到完整 SoC 和未來多芯片系統的 NoC 配置。

·加快產品上市:RTL 針對 PPA 經過優化,使 SoC 設計人員能夠實現帶寬和延遲目標。封包化信息可提高線路的利用率,減少線數量,降低時序收斂難度。

·降低風險:NoC 的內置功耗管理、時鐘域交叉和寬度匹配功能有助于降低設計的復雜性。

·快速設計周轉:Cadence 廣泛的軟件仿真和硬件仿真能力可實現早期架構探索,以便于快速驗證 PPA 結果,確保配置滿足設計要求。

·可擴展架構:客戶可以設計一個子系統,并在 NoC 的完整 SoC 環境中重復使用,以便將來在多芯片系統中重復使用。

·靈活:Cadence NoC 兼容任何具有行業標準接口的 IP,包括 AXI4 和 AHB。

“我們很高興看到 Cadence 通過投資系統級解決方案來擴充其 IP 產品組合。”Intel Foundry 副總裁兼生態系統技術辦公室總經理 Suk Lee 表示,“NoC 對于當今 SoC 中的幾乎所有子系統都至關重要,因此我們非常支持 Cadence 開發 NoC 產品,并期待他們未來繼續擴充其 IP 產品組合。”

審核編輯 黃宇

-

Cadence

+關注

關注

65文章

962瀏覽量

143767 -

IP

+關注

關注

5文章

1773瀏覽量

151240 -

電子系統

+關注

關注

0文章

455瀏覽量

31523 -

系統級芯片

+關注

關注

0文章

45瀏覽量

14212 -

NoC

+關注

關注

0文章

39瀏覽量

11878

發布評論請先 登錄

愛普生車規級晶振SG2520CAA智能汽車電子系統的應用

新思科技推出全新硬件輔助驗證產品組合

e絡盟大幅擴充PUI Audio產品系列以強化音頻產品組合

AMD攜多樣化產品組合亮相ISE 2025

羅徹斯特電子的商用航空電子助力經驗證的航空電子系統

線材連接濾波器:電子系統中的守護者

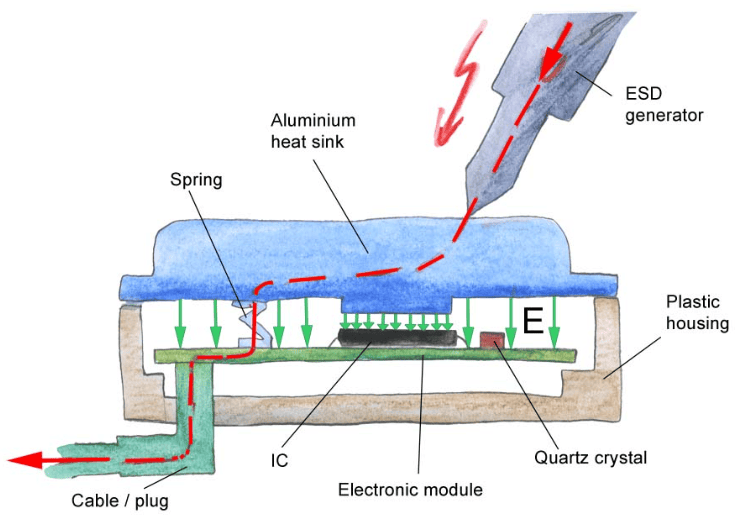

集成電路電磁兼容性及應對措施相關分析(一) — 電子系統性能要求與ESD問題

Celsius EC Solver:對電子系統散熱性能進行準確快速分析

虛擬設計與優化電力電子系統依賴于半導體芯片模型

西門子創新搭載AI的電子系統設計軟件概述 Xpedition NG和HyperLynx NG軟件

FPGA仿真黑科技\"EasyGo Vs Addon \",助力大規模電力電子系統仿真

西門子EDA發布下一代電子系統設計平臺

使用泰克示波器精確診斷并優化汽車電子系統

評論