共讀好書

前言

作為新型功率半導體器件的主流器件,IGBT應用非常廣泛,如家用電器、電動汽車、鐵路、充電基礎設施、充電樁,光伏、風能,工業制造、電機驅動,以及儲能等領域。

IGBT模塊是新一代的功率半導體電子元件模塊,誕生于20世紀80年代,并在90年代進行新一輪的改革升級,通過新技術的發展,現在的IGBT模塊已經成為集通態壓降低、開關速度快、高電壓低損耗、大電流熱穩定性好等等眾多特點于一身,而這些技術特點正式IGBT模塊取代舊式雙極管成為電路制造中的重要電子器件的主要原因。

近些年,電動汽車的蓬勃發展帶動了功率模塊封裝技術的更新迭代。目前電動汽車主逆變器功率半導體技術,代表著中等功率模塊技術的先進水平,高可靠性、高功率密度并且要求成本競爭力是其首先需要滿足的要求。

功率器件模塊封裝結構演進趨勢

IGBT作為重要的電力電子的核心器件,其可靠性是決定整個裝置安全運行的最重要因素。由于IGBT采取了疊層封裝技術,該技術不但提高了封裝密度,同時也縮短了芯片之間導線的互連長度,從而提高了器件的運行速率。

按照封裝形式和復雜程度,IGBT產品可以分為裸片DIE、IGBT單管、IGBT模塊和IPM模塊。

1、裸片DIE:由一片晶圓切割而成的多顆裸片DIE;

2、IGBT單管:由單顆DIE封裝而成的IGBT分立器件,電流能力小,適用于家電等領域;

3、IGBT模塊:由多顆DIE并聯封裝而成,功率更大、散熱能力更強,適用于新能源汽車、高鐵、光伏發電等大功率領域;

4、IPM模塊:在IGBT模塊外圍增加其他功能的智能功率模塊(IPM);

IGBT被稱成為“功率半導體皇冠上的明珠”,廣泛應用于光伏電力發電、新能源汽車、軌道交通、配網建設、直流輸電、工業控制等行業,下游需求市場巨大。IGBT的核心應用產品類型為IGBT模塊。IGBT模塊的市占率能夠達到50%以上,而IPM模塊和IGBT單管分別只有28%左右和20%左右。從產品的投資價值來看,由于IGBT模塊的價值量最大,有利于企業快速提升產品規模,其投資價值最大。

IGBT應用領域

實現IGBT國產化,不僅需要研發出一套集芯片設計、晶圓制造、封裝測試、可靠性試驗、系統應用等于一體的成熟工藝技術,更需要先進的工藝設備。

隨著芯片減薄工藝的發展,對封裝提出了更高的要求。封裝環節關系到IGBT是否能形成更高的功率密度,能否適用于更高的溫度、擁有更高的可用性、可靠性,更好地適應惡劣環境。

IGBT模塊封裝是將多個IGBT集成封裝在一起,以提高IGBT模塊的使用壽命和可靠性,體積更小、效率更高、可靠性更高是市場對IGBT模塊的需求趨勢。常見的模塊封裝技術有很多,各生產商的命名也不一樣,如英飛凌的62mm封裝、TP34、DP70等等。一個IGBT模塊的封裝需經歷貼片、真空焊接、等離子清洗、X-RAY照線光檢測、鍵合、灌膠及固化、成型、測試、打標等等的生產工序。

IGBT封裝工藝流程

IGBT模塊封裝流程簡介

1、絲網印刷:將錫膏按設定圖形印刷于散熱底板和DBC銅板表面,為自動貼片做好前期準備 印刷效果;

2、自動貼片:將IGBT芯片與FRED芯片貼裝于DBC印刷錫膏表面;

IGBT封裝環節包括:絲網印、貼片、鍵合、功能測試等環節。這其中任何一個看似簡單的環節,都需要高水準的封裝技術和設備配合完成。

例如貼片環節,將IGBT芯片與FRED芯片貼裝于DBC印刷錫膏表面。這個過程需要對IGBT芯片進行取放,要確保貼片良率和效率,就要求以電機為核心的貼片機具有高速、高頻、高精力控等特點。

隨著新能源汽車行業的高速發展,對高功率、高密度的IGBT模塊的需求急速增加,很多汽車廠商都已走上了IGBT自研道路,以滿足整車生產需求,不再被上游產業鏈“卡脖子”。

要生產具有高可靠性的IGBT模塊,高精度芯片貼裝設備必不可少。

3、真空回流焊接:將完成貼片的DBC半成品置于真空爐內,進行回流焊接;

高質量的焊接技術,才能生產出高可靠性的產品。一般回流焊爐在焊接過程中會殘留氣體,并在焊點內部形成氣泡和空洞。超標的焊接氣泡會對焊點可靠性產生負面的影響,包括:

(1) 焊點機械強度下降;

(3)高頻器件的阻抗增加明顯;

(4)導熱性降低導致元器件過度升溫。

真空回流焊接工藝是在回流焊接過程中引入真空環境的一種回流焊接技術,相對于傳統的回流焊,真空回流焊在產品進入回流區的后段,制造一個真空環境,大氣壓力可以降到 5mbar(500pa)以下,并保持一定的時間,從而實現真空與回流焊接的結合,此時焊點仍處于熔融狀態,而焊點外部環境則接近真空,由于焊點內外壓力差的作用,使得焊點內的氣泡很容易從中溢出,焊點空洞率大幅降低。低的空洞率對存在大面積焊盤的功率器件尤其重要,由于高功率器件需要通過這些大面積焊盤來傳導電流和熱能,所以減少焊點中的空洞,可以從根本上提高器件的導電導熱性能。

4、超聲波清洗:通過清洗劑對焊接完成后的DBC半成品進行清洗,以保證IGBT芯片表面潔凈度滿足鍵合打線要求求。

5、X-RAY缺陷檢測:通過X光檢測篩選出空洞大小符合標準的半成品,防止不良品流入下一道工序;

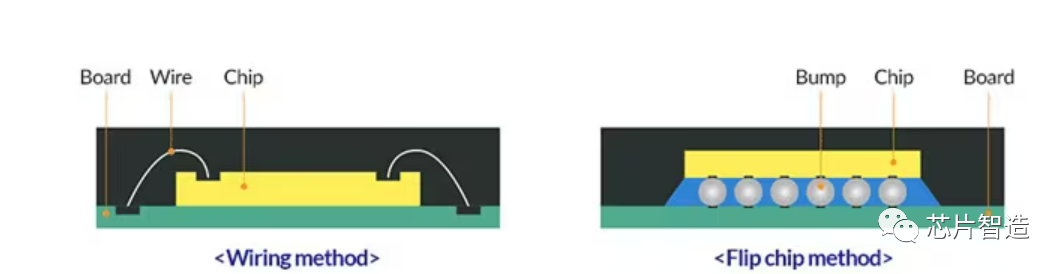

6、自動鍵合:通過鍵合打線,IGBT芯片打線將各個IGBT芯片或DBC間連結起來,形成完整的電路結構。

半導體鍵合AOI主要應用于WB段后的檢測,可為IGBT生產提供焊料、焊線、焊點、DBC表面、芯片表面、插針等全面的檢測。

▲高精度還原線弧

7、激光打標:對IGBT模塊殼體表面進行激光打標,標明產品型號、日期等信息;

8、殼體塑封:對殼體進行點膠并加裝底板,起到粘合底板的作用;

9、功率端子鍵合

10、殼體灌膠與固化:對殼體內部進行加注A、B膠并抽真空,高溫固化 ,達到絕緣保護作用;

11、封裝、端子成形:對產品進行加裝頂蓋并對端子進行折彎成形;

12、功能測試:對成形后產品進行高低溫沖擊檢驗、老化檢驗后,測試IGBT靜態參數、動態參數以符合出廠標準 IGBT 模塊成品。

功率半導體模塊封裝是其加工過程中一個非常關鍵的環節,它關系到功率半導體器件是否能形成更高的功率密度,能否適用于更高的溫度、擁有更高的可用性、可靠性,更好地適應惡劣環境。功率半導體器件的封裝技術特點為:設計緊湊可靠、輸出功率大。其中的關鍵是使硅片與散熱器之間的熱阻達到最小,同樣使模塊輸人輸出接線端子之間的接觸阻抗最低。

IGBT模塊的封裝技術難度高,高可靠性設計和封裝工藝控制是其技術難點。IGBT模塊具有使用時間長的特點,汽車級模塊的使用時間可達15年。因此在封裝過程中,模塊對產品的可靠性和質量穩定性要求非常高。高可靠性設計需要考慮材料匹配、高效散熱、低寄生參數、高集成度。封裝工藝控制包括低空洞率焊接/燒結、高可靠互連、ESD防護、老化篩選等,生產中一個看似簡單的環節往往需要長時間摸索才能熟練掌握,如鋁線鍵合,表面看只需把電路用鋁線連接起來,但鍵合點的選擇、鍵合的力度、時間及鍵合機的參數設置、鍵合過程中應用的夾具設計、員工操作方式等等都會影響到產品的質量和成品率。

集成電路產業鏈包括芯片設計、晶圓制造、芯片封裝和測試等環節,各個細分環節目前都 已經發展成為獨立的子行業。按照集成電路產品的生產制造過程進行劃分,IC 設計行業 是集成電路行業的上游。IC 設計企業設計產品方案,通過代工方式由晶圓代工廠 Foundry、 封裝廠商和測試廠商完成芯片的制造、封裝和測試,然后將芯片產成品作為元器件銷售給 電子設備制造廠商。

集成電路測試服務行業上游的測試機、探針臺等設備主要由美國、日本的海外設備廠商壟 斷。測試服務廠家主要分為兩類:1)封測廠自有測試產線;2)專業的第三方測試公司。芯片設計廠商是芯片測試服務行業的主要客戶,以 SoC/MCU/FPGA 等設計行業為主。早期 的 IC 設計公司會將訂單直接下達至封測廠,再由封測廠外包至第三方的集成電路測試公 司,隨后逐步演進為 IC 設計公司直接下訂單至第三方測試公司。

晶圓測試(Chip Probing),簡稱 CP,是指通過探針臺和測試機的配合使用,對晶圓上的 裸芯片(gross die)進行功能和電學性能參數的測試。測試過程主要為:探針臺將晶圓 逐片傳送至測試位置,芯片端點通過探針、專用連接線與測試機的功能模塊進行連接,測試機對芯片施加輸入信號并采集輸出信號,以判斷芯片功能和性能是否達到設計規范要求。對裸片的測試結果通過通信接口傳送至探針臺,探針臺會根據相應的信息對芯片進行打點 標記,形成晶圓的 Mapping,即晶圓的電性能測試結果。CP 測試設備主要由支架、測試機、 探針臺、探針卡等部件組成。CP 測試會統計出晶圓上的芯片合格率、不合格芯片的確切位 置和各類形式的良率等,可用于指導芯片設計和晶圓制造的工藝改進。

芯片成品測試(Final Test),簡稱 FT,FT 測試是在芯片封裝后按照測試規范對電路成品 進行全面的電路性能檢測,目的是挑選出合格的成品芯片,保障芯片在任何環境下都可以 維持設計規格書上所預期的功能及性能。通過分選機和測試機配合使用,測試過程主要為:分選機將被測芯片逐個傳送至測試工位,被測芯片的引腳通過測試工位上的基座、專用連 接線與測試機的功能模塊進行連接,測試機對芯片施加輸入信號并采集輸出信號,判斷芯 片功能和性能是否達到設計規范要求。測試結果通過通信接口傳送至分選機,分選機據此 對被測芯片進行標記、分選、收料或編帶。FT 測試系統通常由支架、測試機、分選機、測 試板和測試座組成。FT 測試環節的數據可以用于指導封裝環節的工藝改進。

CP 測試的主要目的在于挑出壞的裸片,減少后續的封裝和 FT 測試成本;FT 測試的主要目 的確保芯片符合交付要求,避免將不合格的芯片交付給下游用戶。相比于 FT 測試,CP 測 試精密度要求更高、技術要求更高、難度更大。芯片在完成封裝后處于良好的保護狀態, 體積也較晶圓狀態的裸片增加幾倍至數十倍,因此 FT 測試對潔凈等級和作業精細程度的 要求較 CP 測試低一個級別,但測試作業的工作量和人員用工量更大。CP 測試和 FT 測試 在確保芯片良率、控制生產成本、指導 IC 設計和生產工藝改進等方面都起到了至關重要 的作用。

1.2AI 芯片加大Chiplet等先進封測需求,芯片測試 “量價齊升”

在 AI 浪潮下,算力是生成式 AI 核心。GPU 可以通過并行化矩陣運算,使得生成式 AI 中 龐大的語言模型能夠同時處理海量數據,從而顯著加快了訓練時間。目前龍頭公司英偉達 的新產品GB200已經采用Chiplet方案,將兩個GPU和一個CPU相連形成一個“Blackwell” 芯片,與上一代 H100 相比,有望將訓練性能提高 4 倍,推理性能提高 30 倍。

此外,AMD 的 MI300 同樣采用 CPU+GPU 合封的 Chiplet 方式,單卡硬件性能出色。MI300A 成為全球首個為 AI 和 HPC 打造的 APU 加速卡。采用 Chiplet 設計,擁有 13 個小芯片,基 于 3D 堆疊,包括 24 個 Zen4 CPU 內核,同時融合了 6 顆 CDNA 3 GPU 和 8 個 HBM3,集成 了 5nm 和 6nm IP,總共包含 128GB HBM3 顯存和 1460 億晶體管。根據 AMD 發布會,MI300A 相比上一代產品 MI250X 在 AI 算力上是上一代的 8 倍,而在單位能耗的 AI 運算上是上一 代的 5 倍。MI300X 沒有集成 CPU,而是集成 8 個 GPU 以及 8 個HBM內存模組,其集成的晶 體管數量達到了 1530 億。

在 AI 算力芯片的設計中,Chiplet 相較于 SoC 對于性能提升更有優勢、性價比更高,有 望成為 AI 芯片設計公司的主流設計方案。Chiplet 具體是指小型模塊化芯片,通過 dieto-die 內部互聯技術將多個模塊芯片與底層基礎芯片封裝在一起形成一個整體的內部芯 片。與 SoC 不同,SoC 是在設計階段將不同的模塊設計到一顆 die(芯片裸片)中,晶圓 制造完成后封裝;Chiplet 則將不同模塊從設計時就按照不同計算或者功能單元進行分解, 制作成不同 die 后使用先進封裝技術互聯封裝,不同模塊制造工藝可以不同。

Chiplet 相比傳統 SoC 芯片優勢明顯。Chiplet 能利用最合理的工藝滿足數字、射頻、模 擬、I/O 等不同模塊的技術要求,把大規模的 SoC 按照功能分解為模塊化的芯粒,在保持 較高性能的同時,大幅度降低了設計復雜程度,有效提高了芯片良率、集成度,降低芯片 的設計和制造成本,加速了芯片迭代速度。Chiplet 技術的興起,拉動測試產業整體需求。在 CP 測試環節,因為 Chiplet 封裝成本 高,為確保良率、降低成本,需要在封裝前對每一顆芯片裸片進行 CP 測試,相較于 SoC, Chiplet 對芯片的 CP 測試需求按照芯片裸片數量成倍增加;在 FT 測試環節,隨著 Chiplet 從 2D 逐漸發展到 2.5D、3D,測試的難度提升,簡單測試機減少,復雜測試機增加。Chiplet 技術拉動了測試需求,半導體測試廠商有望迎來需求起量。

大趨勢下的國產替代:芯片制造鏈從臺系向內地轉移

中國大陸正承接產業遷移,帶動國內半導體測試產能擴張。自從上世紀 70 年代半導體產 業在美國形成規模以來,半導體產業沿著“美國→日本→韓國和中國臺灣→中國大陸”的 順序共經歷了三次產業遷移。中國大陸憑借著勞動力成本、技術、人才等優勢,完成了半 導體產業的原始積累。此外,受地緣政治等因素的影響,建立自主可控的產業鏈已成為當 前階段的重要目標,特別是特種芯片及高端 AI 算力芯片制造鏈回遷迫在眉睫。半導體國 產化進程正持續加深,帶動國內半導體測試新產能不斷擴張。

國內晶圓廠及 IDM 廠商資本開支處于高位,擴產趨勢明顯,有望拉動整體測試需求。受產 業鏈轉移趨勢影響,國內晶圓廠及 IDM 廠商資本開支持續處于高位,正處于不斷擴產的過 程。測試在產業鏈中的位置緊貼晶圓廠,伴隨著晶圓制造產能的遷移,測試產能有望隨之 向國內轉移。根據中芯國際 2023 年報中給出的對于 2024 年的指引,資本開支較 2023 年 有望保持持平。展望未來,國內晶圓廠資本開支有望持續處于高位,與之配套的測試服務 產能有望迎來快速增長。

01.芯片封測

芯片封測是半導體生產過程的關鍵環節之一,包括芯片測試和芯片封裝兩個步驟。

芯片測試是在半導體制造的過程中對芯片進行嚴格的檢測和測試,以驗證芯片是否符合設計要求,包括數字、模擬、混合信號電路的測試等,并檢查焊點的可靠性和連接強度。這一步是為了確保芯片的質量和穩定性。

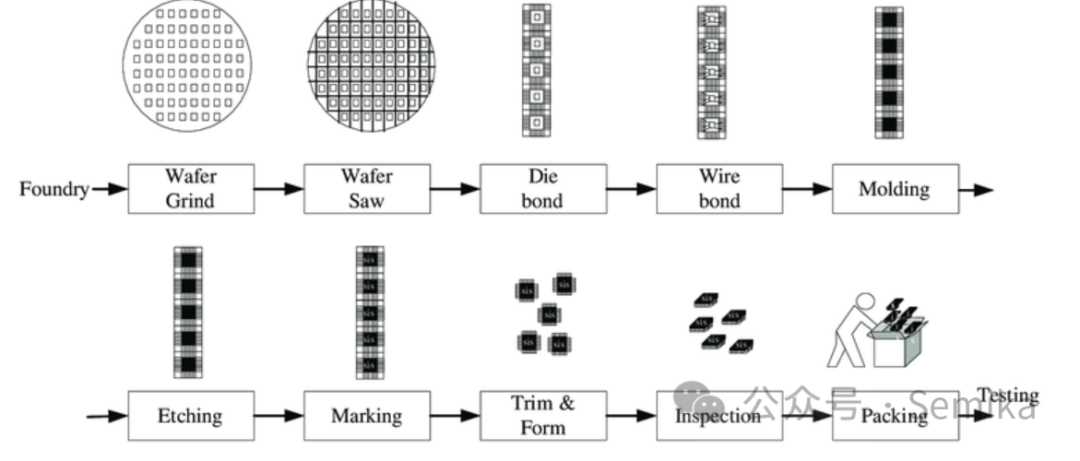

芯片封裝則是將測試完成的芯片進行封裝,以便其被應用在各種設備中。封裝過程涉及一系列工藝和技術,包括晶圓減薄、晶圓切割、光檢查、芯片貼裝等,封裝后還要對封裝工藝質量和代工質量進行測試,以保證芯片的穩定性和可靠性。

02.芯片封測的基本流程

芯片封測的基本流程主要包括封裝和測試兩大環節。

在封裝環節,首先進行晶圓減薄,將剛出廠的晶圓進行背面減薄,達到封裝需要的厚度。接著是晶圓切割,將晶圓切割成一個個獨立的Dice,并對這些Dice進行清洗。然后,進行芯片粘接,即將芯片粘接在基板上,銀漿固化以防止氧化,再進行引線焊接。完成這些步驟后,進行注塑,用EMC(塑封料)把產品封裝起來,并加熱硬化。隨后,進行激光打字,在產品上刻上生產日期、批次等內容。緊接著是高溫固化,以保護IC內部結構,消除內部應力。之后,去溢料,修剪邊角。最后,進行電鍍,提高導電性能,增強可焊接性。

在測試環節,主要包括功能測試和焊點可靠性測試等。功能測試是對芯片的功能進行測試,驗證芯片是否符合設計要求。焊點可靠性測試則是對芯片焊點的可靠性進行測試,驗證焊點的可靠性和連接強度。

常見的封測設備和工具

封裝設備:封裝設備主要用于將芯片封裝在適當的封裝體中,常見的封裝設備有自動封裝機、上膠機、壓合機等。這些設備能夠自動化完成芯片的封裝過程,提高生產效率。

測試設備:測試設備用于對封裝好的芯片進行測試,包括性能測試和功能測試。常見的測試設備有測試機、探針臺、顯微鏡等。測試機能夠對芯片進行電性能測試,探針臺則用于對芯片進行物理連接和信號傳輸,顯微鏡則用于觀察芯片的結構和缺陷。

測量工具:測量工具用于精確測量芯片的尺寸、形狀和位置等參數。常見的測量工具有顯微鏡、千分尺、投影儀等。這些工具能夠確保芯片的封裝精度和質量。

此外,在芯片封測過程中,還需要使用一些輔助設備和工具,如清洗設備、烘烤設備、夾具、吸盤等。這些設備和工具在封裝和測試過程中起著重要的作用,確保芯片能夠正常工作和符合質量標準。

自動測試設備(ATE)

自動測試設備(ATE)是一種自動化系統,專門用于電氣、熱力和物理測試,無需人工直接干預。ATE的主要目的是加速測試過程、執行重復任務或增強測試系統的重復性和一致性。它廣泛應用于半導體領域,對被測對象進行性能驗證和故障診斷,具有工作效率高、操作簡單、靈敏度高、精度高等優勢。

ATE的主要工作流程是以計算機編程代替人工測試,基于測試程序控制儀器并對待測品進行輸入和輸出信號檢測分析,從而判斷待測品的性能是否符合要求。ATE的應用可以顯著減少人工測試的成本和誤差,提高測試效率和準確性。

隨著技術的發展,ATE正朝著高度集成化、更高的測試速度以及適應5G和物聯網(IoT)應用等方向發展。高度集成化的ATE測試座將整合更多的測試功能和自動化控制,以適應電子產品的復雜性和需求的增加。同時,ATE也需要具備更快的測試和數據傳輸速度,以滿足更高的產能需求。

探針卡

探針卡(probe card)又稱晶元探針卡,是晶圓測試廠廣泛用于晶圓測試的關鍵接口,主要由PCB、探針、ring組成,根據不同需求,還可能有電子元件等。其功能是將探針卡上的探針直接與芯片上的焊墊或凸塊直接接觸,導出芯片訊號,再配合周邊測試儀器與軟件控制達到自動化量測晶圓的目的。探針卡的應用范圍廣泛,包括內存、邏輯、消費、驅動、通訊IC等科技產品的晶圓測試。

探針卡主要分為懸臂探針卡和垂直探針卡兩類,廣泛應用于集成電路、光電器件、傳感器件、電子器件、LCD等測試領域,服務的產業涉及半導體、軍工、航天、汽車電子、工業控制、消費類電子等。

在操作時,需要準備一支探針卡和一臺測試電路板的儀器設備,并檢查電路板是否有損壞或松動的部件。然后,根據測試需求在電路板上選擇測試點,并將探針卡的探頭連接到測試點。最后,在測試儀器上觀察結果并記錄。

探針卡對于前期測試的開發及后期量產測試的良率保證都非常重要,是晶圓制造過程中對制造成本影響相當大的重要制程。

03.封測技術的分類

封測技術是指將半導體芯片進行封裝,并進行測試的過程,其分類可以從多個維度進行考察。

從測試目的和階段來看,封裝測試技術主要可以分為成品測試技術、封裝材料測試技術以及封裝失效分析技術。成品測試技術是在電子產品組裝和封裝后進行的最終測試,主要用于檢測產品是否符合設計要求和規格要求,通常包括功能測試、信號測試、無損測試等。封裝材料測試技術則主要用于測試封裝過程中所使用的材料是否符合要求,涉及到材料的可靠性、耐久性、機械強度和導電性等方面。封裝失效分析技術則是對封裝過程中所發生的各種故障進行分析和診斷,確定故障原因和采取措施。

從測試手段和方法來看,常見的封裝測試技術有人工目檢(MVI)、在線測試(ICT)、自動光學測試(AOI)、自動X射線測試(AXI)以及飛針測試等。人工目檢是一種用肉眼檢查的方法,但在處理細間距芯片和焊接質量檢查時,其效果可能并不理想。飛針測試則是以兩根探針對器件加電來實現檢測的方法,但隨著器件的小型化和產品的高密度化,其不足也逐漸顯現。ICT針床測試是一種廣泛使用的測試技術,測試速度快,適合單一品種大批量的產品。自動光學檢測(AOI)則是近幾年興起的一種檢測方法,具有高效、準確的特點。

此外,根據封裝形式和技術特點,還有系統級封裝(SiP)和晶圓級封裝(WLP)等先進封裝測試技術。這些技術不僅提高了芯片的集成度和可靠性,還在尺寸、重量和功耗等方面取得了顯著優勢。

04.封測過程中的常見問題和挑戰

封裝問題:封裝過程中可能出現的問題有焊接不良、封裝裂紋、封裝漏膠等。焊接不良可能表現為焊點未焊接、焊接不良或焊點短路等,影響芯片的電氣性能。封裝裂紋則可能由于材料的熱膨脹系數不匹配或溫度控制不當導致,影響封裝的穩定性和可靠性。封裝漏膠則與封裝膠水不足或不均勻有關,可能導致封裝器件出現漏膠現象。

測試問題:測試階段的問題主要包括測試程序錯誤、測試環境干擾等。測試程序可能存在錯誤或不完整,導致測試結果不準確或無法正確評估芯片的性能。測試環境中可能存在干擾或噪聲等因素,影響測試結果的準確性。此外,常見的測試挑戰還包括漏氣或滲漏、破裂、不均勻壓力分布等問題,這些都可能導致測試結果不準確或測試失敗。

操作和技術挑戰:芯片封測過程中,操作技術不當也可能引發問題。例如,操作員可能未能正確安裝密封部件,或者使用了不合適的密封材料,這些都可能導致密封性能不達標。此外,隨著芯片尺寸的不斷縮小和集成度的提高,對測試設備的精度和穩定性要求也越來越高,這增加了操作和技術上的難度。

環境與可靠性挑戰:溫度變化和材料膨脹等因素也可能對封裝和測試過程造成影響。溫度變化可能引起材料膨脹或收縮,導致密封件不再緊密。而材料膨脹則可能在高溫和高壓環境下導致密封材料破壞。

05.封裝故障

焊接不良:

焊點裂縫:由于焊接過程中產生的熱應力造成。

焊點虛焊:焊接溫度或時間不足導致。

焊點短路:焊料流動不良或焊點位置偏移造成。

接觸不良:

引腳接觸不良:由引腳表面氧化、污染或引腳與接插件之間的接觸不良造成。

引腳斷裂:引腳材料缺陷或外力引起。

引腳過度磨損:長時間插拔或使用環境惡劣導致。

封裝裂紋和漏膠:

由于封裝材料選擇不當、封裝工藝參數不合適或環境因素(如溫度變化、濕度等)的影響,可能導致封裝體出現裂紋。

封裝漏膠則可能與封裝膠水的質量、涂覆工藝或固化過程有關。

機械損傷:

在封裝、運輸或安裝過程中,芯片可能受到物理沖擊、振動等機械應力的作用,導致封裝體或內部結構受損。

材料問題:

封裝材料的質量、成分和屬性對封裝質量有重要影響。例如,材料的熱膨脹系數不匹配可能導致封裝體在溫度變化時產生應力,進而引發故障。

06.測試失敗

芯片設計問題:設計缺陷是導致測試失敗的重要原因之一。芯片設計中如果存在錯誤或不完善的地方,其功能或性能可能無法滿足預期。設計上的不足可能導致芯片在測試階段表現出不符合要求的行為,從而引發測試失敗。

測試程序問題:測試程序是評估芯片性能的關鍵工具。如果測試程序存在錯誤或不完整,那么測試結果可能不準確或無法正確評估芯片的性能。測試程序的設計和優化是確保測試準確性和可靠性的重要環節。

環境因素:測試環境中的干擾或噪聲等因素也可能對測試結果產生負面影響。這些環境因素可能干擾測試信號的準確性,導致測試結果與實際情況不符,從而引發測試失敗。

為了降低測試失敗的風險,可以采取以下措施:

在芯片設計階段進行全面的驗證和仿真,盡量避免設計缺陷的出現。

優化測試程序和方案,確保覆蓋率和準確性,提高測試的可靠性。

加強測試環境的控制,減少干擾和噪聲的影響,確保測試結果的準確性和可靠性。

07.封測技術的發展趨勢

封測技術的發展趨勢呈現出多個方向,隨著電子信息產業的快速發展和新興領域的不斷涌現,芯片封測市場需求持續增長,為封測技術的發展提供了廣闊的空間。

隨著物聯網、智能家居等領域的興起,對高可靠性集成電路的需求不斷增加,因此,高可靠性封測方案的需求也在增長。這要求封測技術不斷創新,以滿足市場對高質量集成電路的需求。

先進封裝技術將成為未來封測市場的主要增長點。在芯片制程技術進入“后摩爾時代”后,先進封裝技術能在不單純依靠芯片制程工藝實現突破的情況下,通過晶圓級封裝和系統級封裝,提高產品集成度和功能多樣化,滿足終端應用對芯片輕薄、低功耗、高性能的需求,同時大幅降低芯片成本。

隨著新材料、新工藝的不斷涌現,芯片封測技術將迎來更加廣闊的發展空間。新材料和新工藝的應用將進一步提升封測技術的性能,降低制造成本,并推動產業向高端化、智能化發展。

審核編輯 黃宇

-

芯片

+關注

關注

456文章

50879瀏覽量

424139 -

IGBT

+關注

關注

1267文章

3797瀏覽量

249167 -

功率半導體

+關注

關注

22文章

1161瀏覽量

43008

發布評論請先 登錄

相關推薦

半導體封裝工藝面臨的挑戰

功率半導體IGBT模塊的封裝工藝及芯片封測技術發展

功率半導體IGBT模塊的封裝工藝及芯片封測技術發展

評論