隨著人工智能技術(shù)的飛速發(fā)展,神經(jīng)網(wǎng)絡(luò)作為其核心組成部分,已廣泛應(yīng)用于圖像識別、語音識別、自然語言處理等多個領(lǐng)域。然而,傳統(tǒng)基于CPU或GPU的神經(jīng)網(wǎng)絡(luò)計(jì)算方式在實(shí)時性、能效比等方面存在諸多挑戰(zhàn)。現(xiàn)場可編程門陣列(FPGA)作為一種靈活、高效的硬件實(shí)現(xiàn)方式,為神經(jīng)網(wǎng)絡(luò)的加速提供了新的思路。本文將從FPGA實(shí)現(xiàn)神經(jīng)網(wǎng)絡(luò)的基本原理、關(guān)鍵技術(shù)、實(shí)現(xiàn)流程以及應(yīng)用前景等方面進(jìn)行詳細(xì)闡述。

一、FPGA與神經(jīng)網(wǎng)絡(luò)概述

1.1 FPGA簡介

FPGA(Field-Programmable Gate Array)是一種可編程邏輯器件,其內(nèi)部包含大量的可配置邏輯塊(CLBs)、輸入輸出塊(IOBs)以及互連資源。用戶可以通過編程方式,根據(jù)具體需求定制FPGA的硬件功能,實(shí)現(xiàn)高度靈活性和定制化。

1.2 神經(jīng)網(wǎng)絡(luò)基礎(chǔ)

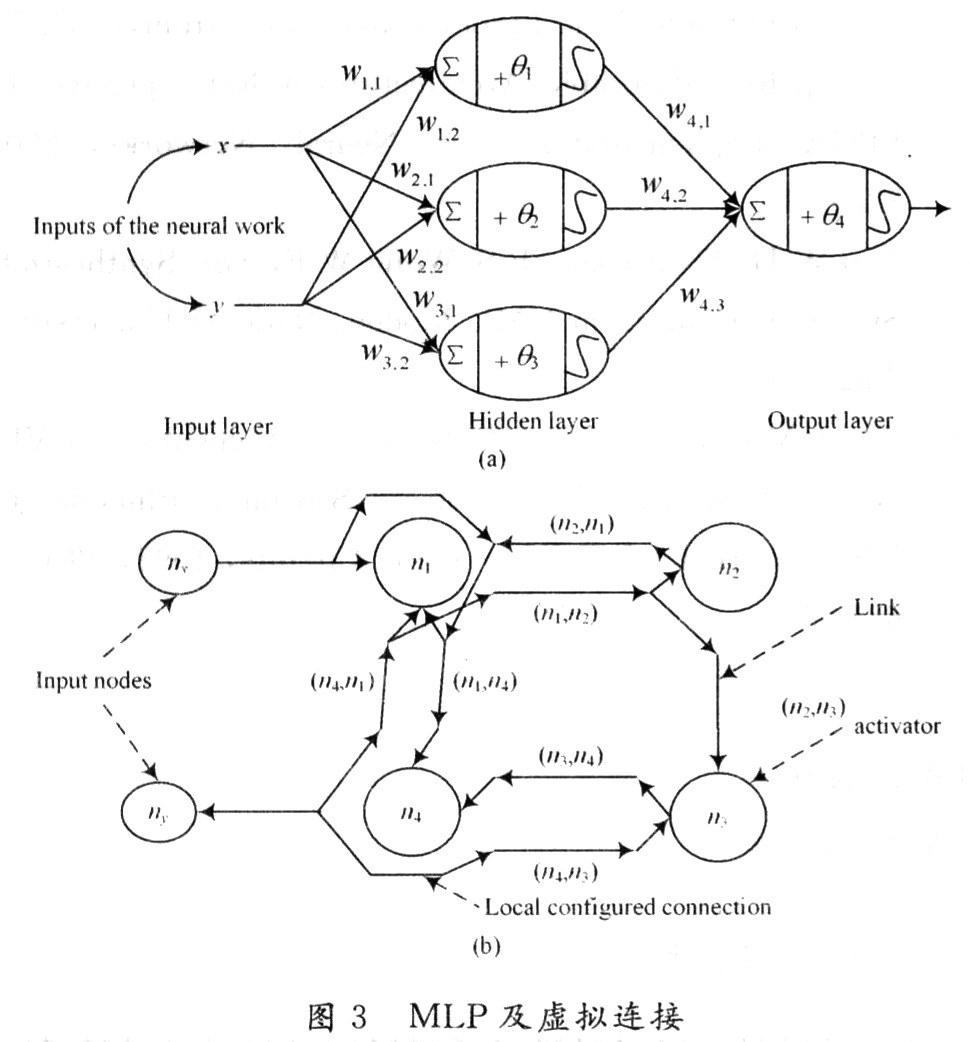

神經(jīng)網(wǎng)絡(luò)是一種模擬人腦神經(jīng)元網(wǎng)絡(luò)結(jié)構(gòu)的計(jì)算模型,由多個神經(jīng)元相互連接而成。每個神經(jīng)元接收輸入信號,通過激活函數(shù)進(jìn)行非線性轉(zhuǎn)換,并將輸出傳遞給其他神經(jīng)元。神經(jīng)網(wǎng)絡(luò)通過層次結(jié)構(gòu),可以學(xué)習(xí)和識別復(fù)雜的模式和規(guī)律。

二、FPGA實(shí)現(xiàn)神經(jīng)網(wǎng)絡(luò)的關(guān)鍵技術(shù)

2.1 并行計(jì)算能力

FPGA具有高效的并行計(jì)算能力,可以同時處理多個數(shù)據(jù)點(diǎn),從而加速神經(jīng)網(wǎng)絡(luò)的運(yùn)算過程。在神經(jīng)網(wǎng)絡(luò)中,大量矩陣運(yùn)算和向量運(yùn)算可以通過FPGA的并行處理能力進(jìn)行優(yōu)化,顯著提高計(jì)算效率。

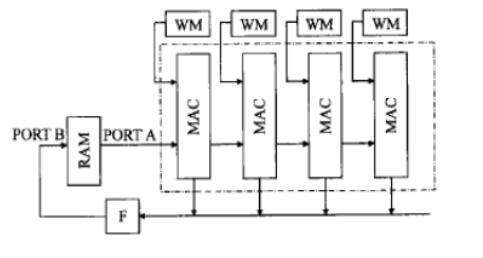

2.2 定制化硬件加速

FPGA可以根據(jù)神經(jīng)網(wǎng)絡(luò)的具體需求,定制化設(shè)計(jì)硬件加速結(jié)構(gòu)。例如,針對神經(jīng)網(wǎng)絡(luò)中的乘法累加(MAC)操作,可以設(shè)計(jì)專用的MAC單元,減少資源消耗并提高計(jì)算速度。

2.3 低功耗設(shè)計(jì)

相比于CPU或GPU,F(xiàn)PGA在實(shí)現(xiàn)相同計(jì)算能力時具有較低的功耗。這是因?yàn)镕PGA的硬件設(shè)計(jì)更加緊湊,減少了不必要的功耗開銷。在神經(jīng)網(wǎng)絡(luò)應(yīng)用中,低功耗設(shè)計(jì)對于延長設(shè)備續(xù)航時間和減少能源消耗具有重要意義。

2.4 實(shí)時性保障

FPGA的硬件實(shí)現(xiàn)方式使得神經(jīng)網(wǎng)絡(luò)計(jì)算具有更強(qiáng)的實(shí)時性。在一些對實(shí)時性要求較高的應(yīng)用場景中,如自動駕駛、實(shí)時圖像處理等,F(xiàn)PGA可以提供更為可靠的解決方案。

三、FPGA實(shí)現(xiàn)神經(jīng)網(wǎng)絡(luò)的流程

3.1 設(shè)計(jì)神經(jīng)網(wǎng)絡(luò)模型

首先,根據(jù)具體應(yīng)用需求設(shè)計(jì)合適的神經(jīng)網(wǎng)絡(luò)模型。這包括確定神經(jīng)網(wǎng)絡(luò)的架構(gòu)、層次結(jié)構(gòu)、激活函數(shù)等參數(shù)。網(wǎng)絡(luò)設(shè)計(jì)可以使用深度學(xué)習(xí)框架,如TensorFlow或PyTorch進(jìn)行模擬和驗(yàn)證。

3.2 模型轉(zhuǎn)換與代碼生成

將訓(xùn)練好的神經(jīng)網(wǎng)絡(luò)模型轉(zhuǎn)換為適用于FPGA的格式。這通常涉及將模型參數(shù)和結(jié)構(gòu)通過算法轉(zhuǎn)化為低級的硬件描述語言(如VHDL或Verilog),或者利用高級硬件描述語言(如HLS)進(jìn)行算法級別的轉(zhuǎn)換。轉(zhuǎn)換過程中需要考慮FPGA的并行計(jì)算特性和存儲器訪問優(yōu)化。

3.3 FPGA硬件設(shè)計(jì)

使用FPGA開發(fā)工具(如Xilinx Vivado或Intel Quartus)將轉(zhuǎn)換后的代碼編譯為FPGA可以運(yùn)行的硬件電路。這一步驟包括綜合、布局和布線等工藝,以優(yōu)化FPGA的資源利用率和性能。

3.4 部署與測試

將編譯好的電路下載到FPGA芯片上,并根據(jù)需要連接輸入輸出設(shè)備。運(yùn)行測試程序,驗(yàn)證FPGA上的神經(jīng)網(wǎng)絡(luò)能夠正常工作。測試過程中需要關(guān)注神經(jīng)網(wǎng)絡(luò)的識別準(zhǔn)確率、運(yùn)算效率以及功耗等指標(biāo)。

四、FPGA實(shí)現(xiàn)神經(jīng)網(wǎng)絡(luò)的優(yōu)化策略

4.1 神經(jīng)網(wǎng)絡(luò)壓縮

神經(jīng)網(wǎng)絡(luò)模型壓縮是減少模型大小和計(jì)算復(fù)雜度的重要手段。通過模型剪枝、權(quán)值量化與共享、霍夫曼編碼等方法,可以在不損失精度的前提下顯著降低神經(jīng)網(wǎng)絡(luò)的存儲需求和計(jì)算量。這對于在FPGA等小型設(shè)備上實(shí)現(xiàn)神經(jīng)網(wǎng)絡(luò)具有重要意義。

4.2 定制化加速器設(shè)計(jì)

針對神經(jīng)網(wǎng)絡(luò)中的特定運(yùn)算(如卷積、池化、激活函數(shù)等),可以設(shè)計(jì)專用的硬件加速器。這些加速器可以充分利用FPGA的并行計(jì)算能力和定制化優(yōu)勢,提高神經(jīng)網(wǎng)絡(luò)的計(jì)算效率。

4.3 存儲器訪問優(yōu)化

存儲器訪問是FPGA實(shí)現(xiàn)神經(jīng)網(wǎng)絡(luò)中的關(guān)鍵瓶頸之一。通過優(yōu)化數(shù)據(jù)布局、減少數(shù)據(jù)移動次數(shù)、采用流水線技術(shù)等手段,可以顯著提高存儲器的訪問效率,降低神經(jīng)網(wǎng)絡(luò)的計(jì)算延遲。

五、FPGA實(shí)現(xiàn)神經(jīng)網(wǎng)絡(luò)的應(yīng)用前景

5.1 邊緣計(jì)算

隨著5G、物聯(lián)網(wǎng)等技術(shù)的普及,邊緣計(jì)算成為未來發(fā)展的重要趨勢。FPGA在邊緣計(jì)算領(lǐng)域的應(yīng)用將為神經(jīng)網(wǎng)絡(luò)的實(shí)時推斷和計(jì)算提供更為高效的解決方案。通過FPGA實(shí)現(xiàn)的神經(jīng)網(wǎng)絡(luò)可以在終端設(shè)備上進(jìn)行快速處理,減少數(shù)據(jù)傳輸延遲和帶寬消耗。

5.2 自動駕駛

自動駕駛是神經(jīng)網(wǎng)絡(luò)應(yīng)用的重要領(lǐng)域之一。FPGA可以在自動駕駛系統(tǒng)中實(shí)現(xiàn)高效的圖像處理和決策控制功能。通過定制化硬件加速和并行計(jì)算能力,F(xiàn)PGA可以顯著提高自動駕駛系統(tǒng)的實(shí)時性和準(zhǔn)確性。

5.3 實(shí)時圖像處理

在視頻監(jiān)控、安防、醫(yī)療影像等領(lǐng)域,實(shí)時圖像處理對計(jì)算速度和準(zhǔn)確性有著極高的要求。FPGA憑借其高并行處理能力和低延遲特性,在這些應(yīng)用中展現(xiàn)出巨大潛力。通過FPGA實(shí)現(xiàn)的神經(jīng)網(wǎng)絡(luò)可以實(shí)時分析視頻流中的關(guān)鍵信息,如人臉識別、物體檢測、異常行為識別等,從而大幅提升監(jiān)控系統(tǒng)的智能化水平和響應(yīng)速度。

在醫(yī)療影像領(lǐng)域,F(xiàn)PGA加速的神經(jīng)網(wǎng)絡(luò)可以加速圖像重建、分割、診斷等過程,幫助醫(yī)生更快、更準(zhǔn)確地診斷疾病。特別是在處理高分辨率醫(yī)學(xué)影像(如CT、MRI)時,F(xiàn)PGA的并行計(jì)算能力能夠顯著提升處理速度,減少患者等待時間,提高醫(yī)療服務(wù)效率。

5.4 嵌入式系統(tǒng)與物聯(lián)網(wǎng)

在嵌入式系統(tǒng)和物聯(lián)網(wǎng)(IoT)領(lǐng)域,F(xiàn)PGA因其低功耗、小體積和高度定制化的特點(diǎn)而受到青睞。通過FPGA實(shí)現(xiàn)的神經(jīng)網(wǎng)絡(luò)可以嵌入到各種智能終端設(shè)備中,如智能家居設(shè)備、可穿戴設(shè)備、工業(yè)傳感器等,實(shí)現(xiàn)智能控制、環(huán)境監(jiān)測、健康監(jiān)測等功能。這些設(shè)備能夠?qū)崟r處理傳感器數(shù)據(jù),并根據(jù)神經(jīng)網(wǎng)絡(luò)的分析結(jié)果做出相應(yīng)決策,從而為用戶提供更加智能、便捷的生活體驗(yàn)。

5.5 學(xué)術(shù)研究與原型開發(fā)

FPGA作為一種靈活的硬件平臺,也非常適合用于學(xué)術(shù)研究和原型開發(fā)。研究人員可以利用FPGA快速驗(yàn)證新的神經(jīng)網(wǎng)絡(luò)架構(gòu)和算法,探索神經(jīng)網(wǎng)絡(luò)在各個領(lǐng)域的應(yīng)用潛力。FPGA的可編程性和可擴(kuò)展性使得研究人員能夠輕松修改和優(yōu)化硬件設(shè)計(jì),以滿足不同實(shí)驗(yàn)需求。此外,F(xiàn)PGA還可以作為連接算法與硬件的橋梁,幫助研究人員將算法從軟件層面遷移到硬件層面,實(shí)現(xiàn)算法的硬件加速。

六、挑戰(zhàn)與展望

盡管FPGA在實(shí)現(xiàn)神經(jīng)網(wǎng)絡(luò)方面展現(xiàn)出諸多優(yōu)勢,但仍面臨一些挑戰(zhàn)。首先,F(xiàn)PGA的硬件設(shè)計(jì)復(fù)雜度高,需要專業(yè)的硬件設(shè)計(jì)知識和經(jīng)驗(yàn)。其次,F(xiàn)PGA的編譯和調(diào)試過程相對繁瑣,開發(fā)周期較長。此外,F(xiàn)PGA的定制化設(shè)計(jì)可能導(dǎo)致資源利用率不高,且難以適應(yīng)網(wǎng)絡(luò)結(jié)構(gòu)的頻繁變化。

為了克服這些挑戰(zhàn)并推動FPGA在神經(jīng)網(wǎng)絡(luò)領(lǐng)域的進(jìn)一步發(fā)展,未來可以從以下幾個方面進(jìn)行努力:一是加強(qiáng)FPGA硬件與深度學(xué)習(xí)框架的集成,簡化模型轉(zhuǎn)換和部署過程;二是開發(fā)更加高效、易用的FPGA開發(fā)工具鏈,降低開發(fā)門檻;三是探索更加靈活、可擴(kuò)展的FPGA架構(gòu),以適應(yīng)不同規(guī)模和復(fù)雜度的神經(jīng)網(wǎng)絡(luò)需求;四是加強(qiáng)跨學(xué)科合作與交流,推動FPGA與計(jì)算機(jī)科學(xué)、電子工程、人工智能等領(lǐng)域的深度融合。

總之,F(xiàn)PGA作為一種高效的硬件加速平臺,在神經(jīng)網(wǎng)絡(luò)實(shí)現(xiàn)中展現(xiàn)出巨大潛力。隨著技術(shù)的不斷進(jìn)步和應(yīng)用場景的不斷拓展,F(xiàn)PGA將在更多領(lǐng)域發(fā)揮重要作用,推動人工智能技術(shù)的快速發(fā)展和普及。

-

FPGA

+關(guān)注

關(guān)注

1643文章

21925瀏覽量

612566 -

神經(jīng)網(wǎng)絡(luò)

+關(guān)注

關(guān)注

42文章

4798瀏覽量

102461 -

人工智能

+關(guān)注

關(guān)注

1804文章

48508瀏覽量

245294

發(fā)布評論請先 登錄

脈沖耦合神經(jīng)網(wǎng)絡(luò)在FPGA上的實(shí)現(xiàn)誰會?

【PYNQ-Z2申請】基于PYNQ的卷積神經(jīng)網(wǎng)絡(luò)加速

基于賽靈思FPGA的卷積神經(jīng)網(wǎng)絡(luò)實(shí)現(xiàn)設(shè)計(jì)

人工神經(jīng)網(wǎng)絡(luò)實(shí)現(xiàn)方法有哪些?

如何設(shè)計(jì)BP神經(jīng)網(wǎng)絡(luò)圖像壓縮算法?

如何利用SoPC實(shí)現(xiàn)神經(jīng)網(wǎng)絡(luò)速度控制器?

如何移植一個CNN神經(jīng)網(wǎng)絡(luò)到FPGA中?

基于FPGA的神經(jīng)網(wǎng)絡(luò)的性能評估及局限性

matlab實(shí)現(xiàn)神經(jīng)網(wǎng)絡(luò) 精選資料分享

用FPGA去實(shí)現(xiàn)大型神經(jīng)網(wǎng)絡(luò)的設(shè)計(jì)

基于FPGA的人工神經(jīng)網(wǎng)絡(luò)實(shí)現(xiàn)方法的研究

基于FPGA的人工神經(jīng)網(wǎng)絡(luò)實(shí)現(xiàn)方法的研究

基于FPGA的RBF神經(jīng)網(wǎng)絡(luò)硬件實(shí)現(xiàn)

基于FPGA的神經(jīng)網(wǎng)絡(luò)硬件實(shí)現(xiàn)方法

基于FPGA的RBF神經(jīng)網(wǎng)絡(luò)的硬件實(shí)現(xiàn)

評論