電子發(fā)燒友網(wǎng)報道(文/李彎彎)日前,瀾起科技發(fā)布業(yè)績預(yù)告,2024年半年度實現(xiàn)營業(yè)收入16.65億元,較上年同期增長79.49%;2024年半年度實現(xiàn)歸屬于母公司所有者的凈利潤5.83億元~6.23億元,較上年同期增長612.73%~661.59%。

原因方面,一是公司內(nèi)存接口及模組配套芯片需求實現(xiàn)恢復(fù)性增長,DDR5下游滲透率提升且DDR5子代迭代持續(xù)推進,2024年上半年DDR5第二子代RCD芯片出貨量已超過第一子代 RCD 芯片;二是公司部分AI “運力”芯片新產(chǎn)品開始規(guī)模出貨,為公司帶來新的業(yè)績增長點。

瀾起科技互連類芯片產(chǎn)品有效提升系統(tǒng)“運力”

在人工智能時代,計算機的“算力”和“存力”需求快速增長,系統(tǒng)對“運力”提出了更高的需求。瀾起科技是一家為計算和智算提供高性能“運力”的企業(yè),公司多款高速互連芯片產(chǎn)品可有效提升系統(tǒng)的“運力”,將在未來的人工能智時代發(fā)揮重要作用。

瀾起科技的互連類芯片產(chǎn)品主要包括內(nèi)存接口芯片(含MRCD/MDB 芯片)、內(nèi)存模組配套芯片、 CKD芯片、PCIe Retimer 芯片、MXC 芯片等。

MRCD、MDB芯片:是服務(wù)器高帶寬內(nèi)存模組 MRDIMM 的核心邏輯器件。AI 及大數(shù)據(jù)應(yīng)用的發(fā)展以及相關(guān)技術(shù)的演進推動服務(wù)器 CPU 的內(nèi)核數(shù)量快速增加,迫切需要大幅提高內(nèi)存系統(tǒng)的帶寬,以滿足多核 CPU 中各個內(nèi)核的數(shù)據(jù)吞吐要求,MRDIMM正是基于這種應(yīng)用需求而生。

MRDIMM 工作原理是,MDB芯片用來緩沖來自內(nèi)存控制器或DRAM內(nèi)存顆粒的數(shù)據(jù)信號, 在標準速率下,通過MDB芯片可以同時訪問兩個DRAM內(nèi)存陣列,從而實現(xiàn)雙倍的帶寬。MRCD 用來緩沖來自內(nèi)存控制器的地址、命令、時鐘、控制信號。

MRDIMM 的特點和優(yōu)勢在于:1、使用的是常規(guī)的DRAM顆粒;2、與現(xiàn)有DDR5生態(tài)系統(tǒng)有良好的適配性;3、可以大幅提升內(nèi)存模組的帶寬。

CKD芯片:長久以來,時鐘驅(qū)動功能一直集成在寄存時鐘驅(qū)動器芯片中,應(yīng)用于服務(wù)器 RDIMM或LRDIMM內(nèi)存模組,但尚未在PC端部署。隨著DDR5傳輸速率持續(xù)提升,時鐘信號頻率越來越高,時鐘信號完整性問題日益凸顯。當(dāng)DDR5數(shù)據(jù)速率達到6400MT/s及以上時,PC端的內(nèi)存模組需采用專用時鐘驅(qū)動器(CKD)芯片,對內(nèi)存模組上的時鐘信號進行緩沖和重新驅(qū)動,才能滿足高速時鐘信號的完整性和可靠性要求。

瀾起于2022年9月發(fā)布業(yè)界首款DDR5第一子代CKD工程樣片,并已送樣給業(yè)界主流內(nèi)存廠商,用于新一代臺式機和筆記本電腦內(nèi)存。該芯片的主要功能是緩沖來自臺式機和筆記本電腦中央處理器的高速內(nèi)存時鐘信號,并將其重新驅(qū)動輸出到UDIMM、SODIMM模組上的多個DRAM內(nèi)存顆粒。

PCIe Retimer芯片:是適用于PCIe高速數(shù)據(jù)傳輸協(xié)議的超高速時序整合芯片,這是公司在全互連芯片領(lǐng)域布局的一款重要產(chǎn)品。

近年來,高速數(shù)據(jù)傳輸協(xié)議從 PCIe 3.0(8GT/S)發(fā)展至 PCIe 4.0(16GT/S),再升級至 PCIe 5.0(32GT/S),數(shù)據(jù)傳輸速率不斷翻倍,同時也帶來了顯著的信號衰減和參考時鐘時序重整問題, 這些問題較大限制了超高速數(shù)據(jù)傳輸協(xié)議在下一代計算平臺的應(yīng)用范圍。PCIe 4.0/5.0 的高速傳輸挑戰(zhàn)促進了優(yōu)化高速電路與系統(tǒng)互連設(shè)計的需求,加大了在超高速傳輸環(huán)境下保持信號完整性的研發(fā)熱度。

為了補償高速信號的損耗,提升信號質(zhì)量,通常需在鏈路中引入超高速時序整合芯片 (Retimer)。PCIe Retimer芯片已成為高速電路中不可或缺的重要器件,主要解決數(shù)據(jù)中心數(shù)據(jù)高速、遠距離傳輸時,信號時序不齊、損耗嚴重、完整性差等問題。

瀾起科技的PCIe Retimer芯片采用先進的信號調(diào)理技術(shù),能夠補償信道損耗并消除各種抖動源的影響,從而提升信號完整性,增加高速信號的有效傳輸距離,為服務(wù)器、存儲設(shè)備及硬件加速器等應(yīng)用場景提供可擴展的高性能PCIe互連解決方案。

2023年,公司PCIe 5.0/CXL 2.0 Retimer芯片實現(xiàn)量產(chǎn)。其PCIe 4.0/5.0 Retimer芯片可應(yīng)用于 AI服務(wù)器、NVMe SSD、Riser卡等典型應(yīng)用場景。

MXC芯片:是一款CXL內(nèi)存擴展控制器芯片,可為CPU及基于CXL協(xié)議的設(shè)備提供高帶寬、低延遲的高速互連解決方案,實現(xiàn) CPU 與各 CXL 設(shè)備間的內(nèi)存共享,在大幅提升系統(tǒng)性能的同時,顯著降低軟件堆棧復(fù)雜性和數(shù)據(jù)中心總體擁有成本(TCO)。

MXC 芯片主要應(yīng)用于內(nèi)存擴展及內(nèi)存池化領(lǐng)域,為內(nèi)存 AIC 擴展卡、背板及 EDSFF 內(nèi)存模組而設(shè)計,可大幅擴展內(nèi)存容量和帶寬,滿足高性能計算、人工智能等數(shù)據(jù)密集型應(yīng)用日益增長的需求。

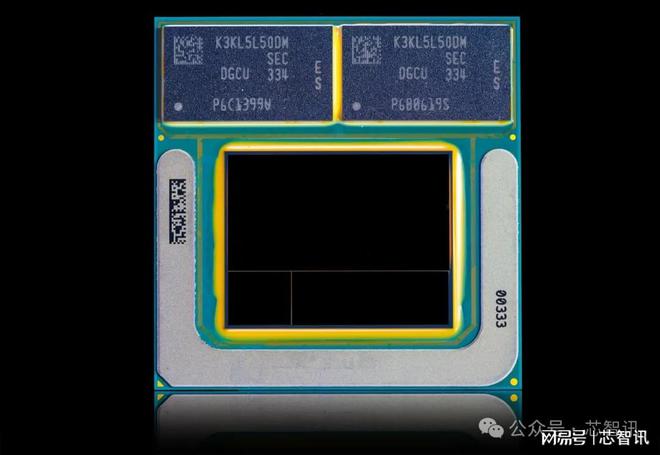

2022年,瀾起發(fā)布了全球首款CXL內(nèi)存擴展控制器芯片(MXC)。2023 年 5 月,三星電子推出其首款支持 CXL 2.0的128GB DRAM,加速了下一代存儲器解決方案的商用化進程,瀾 起的 MXC 芯片作為該解決方案的核心控制器而被采用。

AI高性能“運力”芯片新產(chǎn)品進展

瀾起持續(xù)投入研發(fā),不斷拓寬產(chǎn)品品類,穩(wěn)步推進產(chǎn)品迭代升級。去年,在運力芯片領(lǐng)域,瀾起成功量產(chǎn)PCIe 5.0/CXL 2.0 Retimer芯片;率先試產(chǎn)DDR5第三子代RCD芯片;完成DDR5 第一子代MRCD/MDB芯片、DDR5第一子代CKD芯片、第一代MXC芯片量產(chǎn)版本的研發(fā);完成時鐘發(fā)生器工程樣片的流片;開展DDR5第四子代RCD芯片、第二子代 MRCD/MDB芯片、第二代MXC芯片的工程研發(fā),推進PCIe 6.0 Retimer芯片關(guān)鍵IP的開發(fā)及驗證工作。

2024年上半年,受益于全球 AI 服務(wù)器需求旺盛以及公司市場份額提升,公司的PCIe Retimer 芯片出貨量快速增長,繼2024年第一季度出貨約15萬顆之后,第二季度出貨約30萬顆。

受益于AI及高性能計算對更高帶寬內(nèi)存模組需求的推動,搭配瀾起MRCD/MDB芯片的服務(wù)器高帶寬內(nèi)存模組開始在境內(nèi)外主流云計算/互聯(lián)網(wǎng)廠商規(guī)模試用,公司的MRCD/MDB 芯片銷售收入快速增長,繼2024 年第一季度銷售收入首次超過2,000萬元人民幣之后,第二季度銷售收入超過 5,000 萬元人民幣。

瀾起CKD 芯片于2024 年4月在業(yè)界率先試產(chǎn),受益于AI PC產(chǎn)業(yè)趨勢的推動,以及客戶端新CPU平臺(支持內(nèi)存速率為6400MT/S)發(fā)布時間臨近,相關(guān)內(nèi)存模組廠商開始批量采購 CKD芯片用于備貨,2024 年第二季度公司的CKD芯片開始規(guī)模出貨,單季度銷售收入首次超過1,000萬元人民幣。

寫在最后

可以看到,隨著人工智能時代的日益臨近,互連類芯片產(chǎn)品的重要性將會日益凸顯。如PCIe Retimer芯片,目前一臺典型配置8塊GPU的主流AI服務(wù)器需要8顆或16顆PCIe 5.0 Retimer芯片。未來,PCIe Retimer 芯片的市場空間將隨著GPU需求量的增加而持續(xù)擴大。

-

AI

+關(guān)注

關(guān)注

87文章

30728瀏覽量

268886 -

PCIe

+關(guān)注

關(guān)注

15文章

1234瀏覽量

82579 -

瀾起科技

+關(guān)注

關(guān)注

0文章

100瀏覽量

14754 -

AI芯片

+關(guān)注

關(guān)注

17文章

1879瀏覽量

34990 -

算力

+關(guān)注

關(guān)注

1文章

964瀏覽量

14793 -

存力

+關(guān)注

關(guān)注

0文章

23瀏覽量

80

發(fā)布評論請先 登錄

相關(guān)推薦

直播預(yù)約 |開源芯片系列講座第25期:RISC-V架構(gòu)在高性能領(lǐng)域的進展與挑戰(zhàn)

國芯科技與賽昉科技合作,高性能AI MCU芯片CCR7002測試成功

賽昉聯(lián)合國芯推出高性能AI MCU芯片,實現(xiàn)RISC-V+AI新應(yīng)用

國芯科技:高性能AI MCU芯片CCR7002內(nèi)部測試成功

國芯科技AI MCU芯片CCR7002內(nèi)部測試成功

AI高性能計算平臺是什么

SiFive發(fā)布MX系列高性能AI加速器IP

星宸科技SSU9386榮獲2024年度AI創(chuàng)新產(chǎn)品獎,彰顯AI芯實力

名單公布!【書籍評測活動NO.43】 算力芯片 | 高性能 CPU/GPU/NPU 微架構(gòu)分析

Lunar Lake:NPU性能全面提升,能耗也大幅降低,綜合AI算力提升至120TOPS

AI高性能“運力”芯片新產(chǎn)品進展,規(guī)模出貨大幅提升業(yè)績

AI高性能“運力”芯片新產(chǎn)品進展,規(guī)模出貨大幅提升業(yè)績

評論