高速先生成員--黃剛

每一位剛進入PCB行業的同學,基本上頭幾個接觸到的設計經驗就肯定少不了“3H”原則。當然大家也都知道,這個原則是為了傳輸線之間的串擾改善而建立的規定,那就是要求傳輸線中心到中心的距離滿足至少3H的值(也就是空氣間距gap大于2H),其中H是傳輸線到參考平面的距離,其實也就相當于是上下層PP或者CORE的厚度了,就好像下面的樣子。

當然PCB設計工程師本身只會對物理規則負責,不對電氣規則負責。也就是說,SI工程師定下來“3H”原則后,PCB工程師通過疊層文件知道了H的數值后,然后在組內的高速差分線應用上去就好了。空間緊張的滿足“3H”,空間不緊張的拉開到“5H”,甚至是驚人的“7H”!總之,PCB工程師只管在PCB版圖上實現就完事了。

這不有一天,公司內一群好學的PCB工程師同事找到了Chris,想知道到底“3H”原則是不是就一定能讓高速信號之間的串擾變得很小了,有沒有必要做成“5H”甚至“7H”,總之就是,他們想讓Chris把物理規則量化成電氣規則。面對同事的“軟磨硬泡”,行唄,那就以他們手頭上的這個25Gbps的高速項目為例給他們說道說道。

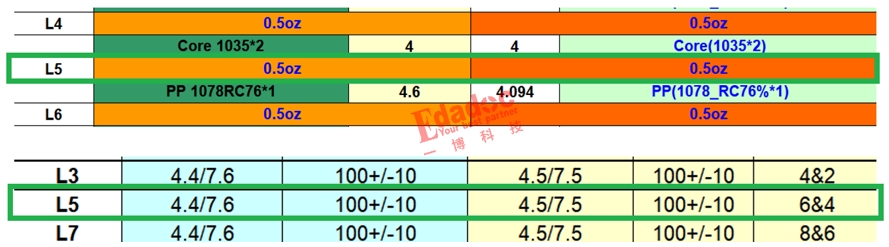

Chris先打開他們設計文件的疊層,高速線走了很多個內層,結構線寬都相同。以L5層高速線為例,上面的core厚度是4mil,下面的PP也差不多4mil。然后按照100歐姆阻抗控制的話,線寬為4.5mil,線間距為7.5mil,如下所示:

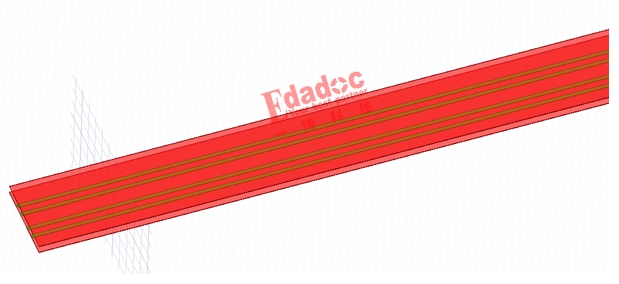

那我們把L5層的走線提取到3D模型中去,通過仿真來驗證所謂的“3H”原則。模型就是下面這樣了。

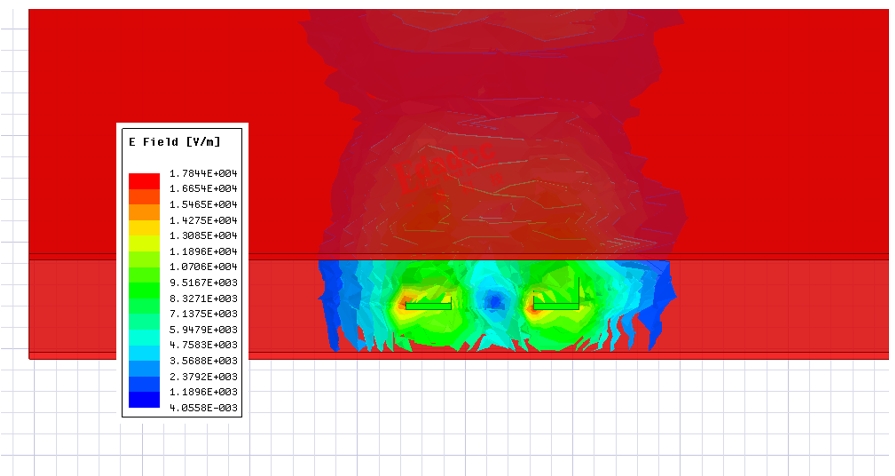

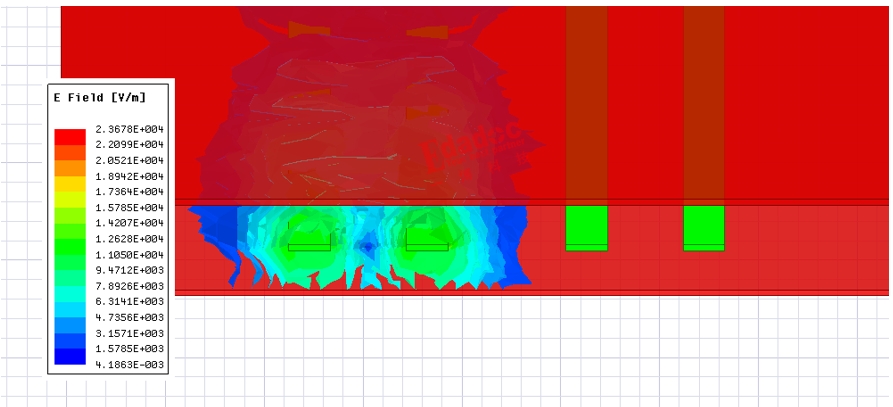

那首先我們看看只有一對走線的情況下,去仿真它的電磁場特性,結果如下:

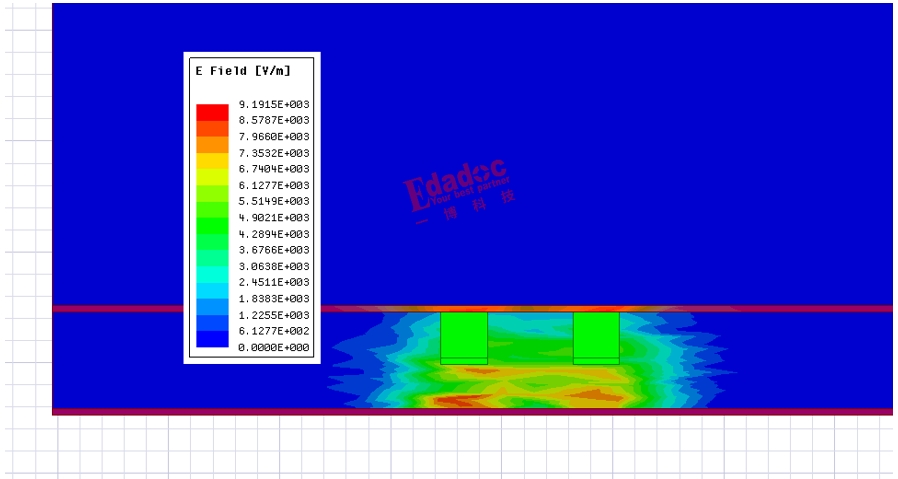

可以看到,電磁場的范圍基本上就在差分線中心往左邊或者右邊3H的距離,H是4mil。再遠的地方其實就沒太多電磁場分布了。從參考地平面的角度去看也是類似的結論,如下所示,也還是基本集中在3H的范圍。

當然如果把另外一對做到3H原則的差分線一起放進來看,也能有同樣的結論,左邊這對攻擊線的電磁場其實還沒波及到右邊這對受害線上面去。既然電磁場沒波及過去,也就說明其實串擾能量也不會很多的傳遞過去。

Chris從電磁場的角度給設計的同事去分析,他們的確是有一種get到新知識的新鮮感,而且這個場的仿真結果也比較形象,能直觀的看到“3H”設計原則的效果,他們看到都紛紛表示。。。贊!

當然,場的仿真結果其實也還是個定性的結果了,可能給PCB設計的同事看比較直觀,但是并沒有起到一個量化的效果。如果要量化具體指標的話,還得回到傳統的S參數仿真方法,也就是直接進行串擾的頻域仿真。

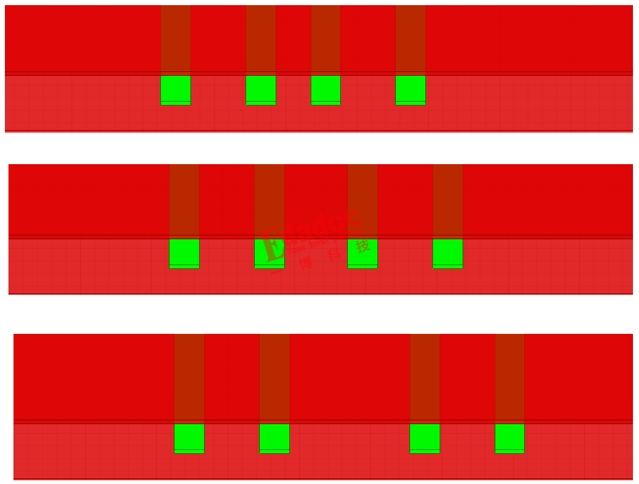

Chris對模型賦上一定的掃描變量,看看這兩對差分線從最小的“2H”到“3H”再到“5H”(其實Chris還順帶偷偷仿真了“7H”哈)的情況下串擾具體數量的差異!以下就是“2H”、“3H”和“5H”三種case的仿真模型。

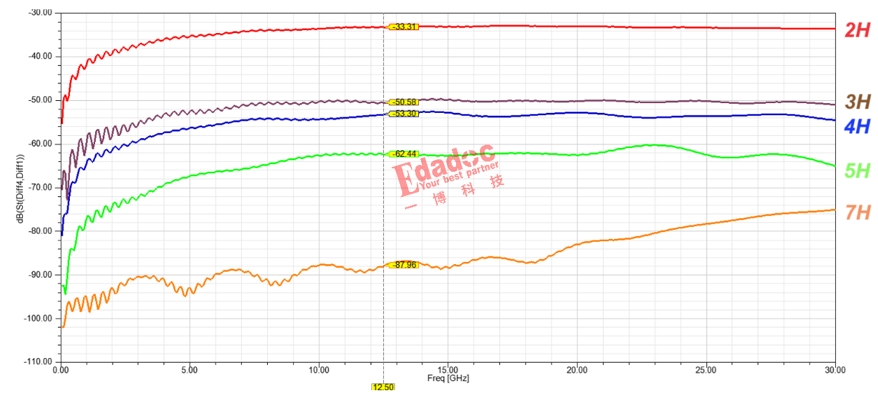

唰一下,不同差分線間距的串擾仿真結果都完成了,我們把結果放到一起來直觀的對比,如下所示:可以看到,2H的情況下串擾就比較大了,只有不到35db,3H的話已經能做到50db,4H和3H其實差異就不大了,如果要往60db去做的話,就要達到5H的距離,如果繼續追求高指標的話,7H可能是你們喜歡的設計哈!

當然對于25Gbps信號來說,編碼方式是NRZ編碼,其實3H是夠用的了。如果在同樣基頻下要跑到56Gbps-PAM4的話,可能需要往5H做,因為PAM4的串擾的要求還是比較高的。反正需要做到多少間距,一個是看你們的產品的速率來定,另外就是看設計工程師能不能做到了哈。

當Chris把這個量化的S參數結果做出來準備再給設計部的同事展示的時候,發現他們早就跑光了,全部回去繼續做他們的設計去了,對于設計工程師來說,知道原理和定性的看到電磁場的結果,他們其實已經滿足了……

審核編輯 黃宇

-

阻抗

+關注

關注

17文章

957瀏覽量

45915 -

仿真

+關注

關注

50文章

4070瀏覽量

133552 -

PCB設計

+關注

關注

394文章

4683瀏覽量

85548 -

串擾

+關注

關注

4文章

189瀏覽量

26943

發布評論請先 登錄

相關推薦

PCB設計中的爬電距離:確保電路板安全可靠

pcb設計中布局的要點是什么

pcb設計中如何設置坐標原點

PCB設計與PCB制板的緊密關系

多層pcb設計如何過孔的原理

什么是PCB扇孔,PCB設計中對PCB扇孔有哪些要求

【Longan Pi 3H 開發板試用連載體驗】+實驗室終端設備+開箱體驗

【Longan Pi 3H 開發板試用連載體驗】基于 Longan Pi 3H 開發板完成智能家居控制小型項目

PCB設計軟件有哪些 pcb設計軟件哪個好用

pcb設計布局布線原則及規則

矽速科技全新推出的高性價比 Linux SBC Longan Pi 3H

深入分析:常說的3H原則在PCB設計中的應用

深入分析:常說的3H原則在PCB設計中的應用

評論