基于FPGA的CCD工業相機系統設計是一個綜合性的項目,它結合了硬件電路設計、FPGA編程以及圖像處理技術。以下是一個詳細的系統設計方案,包括設計概述、硬件架構、FPGA編程要點以及部分關鍵代碼示例。

一、設計概述

1.1 項目背景

隨著工業自動化和機器視覺技術的快速發展,CCD工業相機因其高穩定性、高分辨率和低噪聲等特點,在圖像采集和處理領域得到了廣泛應用。基于FPGA的CCD工業相機系統能夠利用FPGA的高速并行處理能力,實現高效的圖像采集和處理,滿足實時性和高精度要求。

1.2 設計目標

- 設計并實現一個基于FPGA的CCD工業相機系統,能夠實時采集和處理圖像數據。

- 實現CCD驅動電路,產生符合CCD傳感器要求的時序信號。

- 利用FPGA實現圖像預處理和校正算法,提高圖像質量。

- 實現圖像數據的快速傳輸和存儲,支持上位機實時顯示和處理。

二、硬件架構

2.1 系統組成

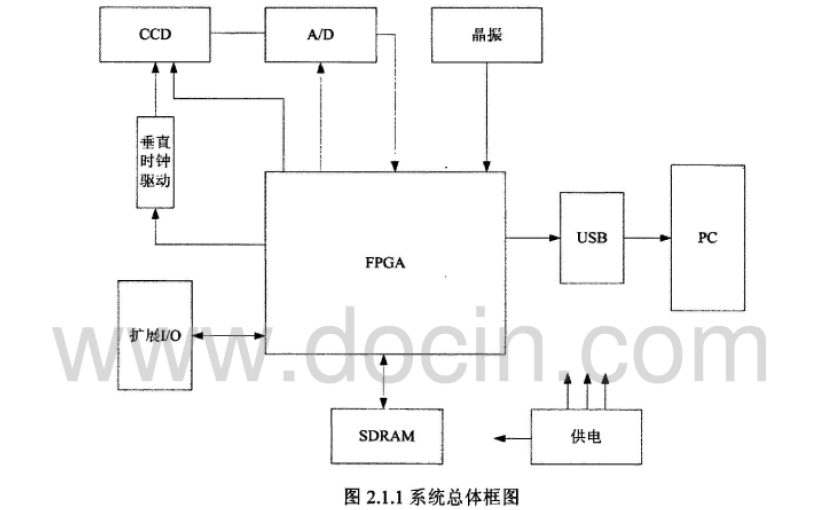

基于FPGA的CCD工業相機系統主要包括以下幾個部分:

- CCD傳感器 :負責將光信號轉換為電信號。

- FPGA模塊 :作為系統的核心控制單元,負責產生CCD驅動時序、圖像信號處理和數據傳輸控制。

- A/D轉換模塊 :將CCD輸出的模擬信號轉換為數字信號。

- 緩存模塊 :用于暫存圖像數據,以便后續處理。

- 數據傳輸接口 :如USB、CameraLink等,用于將圖像數據傳輸到上位機。

2.2 硬件電路設計

- CCD驅動電路 :根據CCD傳感器的要求設計時序電路和偏置電壓電路。時序電路通常由FPGA控制,產生轉移脈沖、采樣保持脈沖等。

- A/D轉換電路 :選擇高速、高精度的A/D轉換器,將CCD輸出的模擬信號轉換為數字信號。

- FPGA外圍電路 :包括電源電路、時鐘電路、復位電路等,為FPGA提供穩定的工作環境。

三、FPGA編程

3.1 編程工具與環境

3.2 主要模塊設計

- CCD時序控制模塊 :根據CCD的數據手冊,設計相應的時序控制邏輯,產生符合CCD要求的驅動信號。

- A/D控制模塊 :控制A/D轉換器的工作狀態,包括啟動、停止和數據讀取等。

- 圖像預處理模塊 :實現圖像的去噪、校正等預處理算法,提高圖像質量。

- 數據傳輸控制模塊 :實現圖像數據的緩存和傳輸控制,將數據通過USB或CameraLink接口發送到上位機。

3.3 示例代碼(Verilog)

CCD時序控制模塊的部分示例代碼:

module ccd_timing_control(

input clk, // 時鐘信號

input rst_n, // 復位信號

output reg sh, // 轉移脈沖

output reg f1, f2, // 二相驅動脈沖

output reg sp, // 采樣保持脈沖

output reg rs, cp // 復位脈沖和箝位脈沖

);

// 內部參數定義

parameter CLOCK_DIV = 1000000; // 時鐘分頻因子

reg [23:0] counter; // 計數器

// 時鐘分頻

always @(posedge clk or negedge rst_n) begin

if (!rst_n) begin

counter <= 0;

end else if (counter == CLOCK_DIV - 1) begin

counter <= 0;

end else begin

counter <= counter + 1;

end

end

// 產生時序脈沖

always @(posedge clk or negedge rst_n) begin

if (!rst_n) begin

sh <= 0;

f1 <= 0;

f2 <= 0;

sp <= 0;

rs <= 0;

cp <= 0;

end else if (counter == SOME_THRESHOLD1) begin

sh <= 1;

// 根據需要設置其他脈沖

end else if (counter == SOME_THRESHOLD2) begin

// 其他脈沖變化邏輯

end

// ...(省略其他條件判斷和脈沖設置)

end

endmodule

當然,我會繼續擴展基于FPGA的CCD工業相機系統設計的內容,包括更詳細的FPGA編程要點、圖像處理算法的實現、系統測試與驗證,以及可能面臨的挑戰和解決方案。

四、FPGA編程要點

4.1 圖像處理算法實現

在FPGA中實現圖像處理算法時,需要充分考慮算法的并行性和資源利用率。以下是一些常見的圖像處理算法及其在FPGA上的實現方法:

- 圖像去噪 :可以采用中值濾波、均值濾波等算法。這些算法在FPGA上可以通過并行處理多個像素點來加速。例如,中值濾波可以通過并行比較多個像素值,并使用多路選擇器(multiplexer)或查找表(LUT)來實現。

- 圖像校正 :包括亮度校正、白平衡校正等。這些校正算法通常涉及到像素值的線性變換或查找表映射。在FPGA中,可以通過配置寄存器或RAM來存儲校正參數,并在圖像處理流水線中插入校正模塊。

- 邊緣檢測 :如Sobel算子、Canny邊緣檢測器等。這些算法在FPGA上可以通過并行計算梯度或邊緣強度來實現。可以使用FPGA的DSP塊來加速乘法運算,并使用并行邏輯來同時處理多個像素點。

4.2 數據流與緩存管理

在FPGA中,有效管理數據流和緩存是確保系統性能的關鍵。以下是一些策略:

- 流水線設計 :通過引入流水線設計,可以重疊處理不同階段的操作,從而提高系統吞吐量。在圖像處理中,可以將圖像分割成多個塊或行,并并行處理這些塊或行。

- 緩存策略 :合理使用FPGA內部的Block RAM(BRAM)或外部SRAM/DDR來緩存圖像數據。緩存策略應根據系統帶寬、延遲需求和資源可用性來定制。例如,可以使用雙緩沖技術來避免處理過程中的數據沖突。

- DMA(直接內存訪問) :在FPGA與外部存儲器(如DDR)之間實現DMA傳輸,可以進一步提高數據傳輸效率。DMA控制器可以在不占用CPU或FPGA主邏輯資源的情況下,自動完成數據傳輸任務。

五、系統測試與驗證

5.1 測試環境搭建

為了驗證基于FPGA的CCD工業相機系統的性能,需要搭建一個全面的測試環境。測試環境應包括:

- CCD傳感器 :用于生成測試圖像。

- FPGA開發板 :搭載設計的FPGA程序。

- 圖像采集軟件 :用于從FPGA接收圖像數據,并顯示在屏幕上。

- 測試圖像庫 :包含各種測試圖像,如標準灰度圖、彩色圖、噪聲圖等。

- 測試儀器 :如示波器、邏輯分析儀等,用于監測FPGA的輸入輸出信號和時序。

5.2 測試步驟

- 功能測試 :驗證FPGA是否正確生成了CCD驅動時序,并成功接收了CCD輸出的圖像數據。

- 性能測試 :測試系統的幀率、分辨率、信噪比等性能指標。

- 圖像處理算法驗證 :通過對比FPGA處理前后的圖像,驗證圖像處理算法的正確性和效果。

- 穩定性測試 :長時間運行系統,觀察是否存在數據丟失、圖像畸變等問題。

- 壓力測試 :在高負載條件下測試系統的性能,如同時處理多個圖像流。

六、可能面臨的挑戰與解決方案

6.1 時序同步問題

由于CCD傳感器和FPGA之間的時序要求非常嚴格,任何微小的時序偏差都可能導致圖像質量下降或數據丟失。解決方案包括:

- 精確的時序設計 :根據CCD傳感器的數據手冊,精確設計FPGA中的時序控制邏輯。

- 使用PLL(鎖相環) :在FPGA中使用PLL來生成穩定的時鐘信號,并調整相位以匹配CCD傳感器的時序要求。

- 時序仿真與驗證 :在FPGA編程過程中,使用仿真工具對時序進行驗證,確保在實際硬件中也能正常工作。

6.2 資源利用與功耗優化

FPGA資源有限,如何在有限的資源內實現高性能的圖像處理算法,并降低功耗,是一個挑戰。解決方案包括:

- 算法優化 :選擇適合FPGA并行處理的算法,并優化算法以減少資源消耗。

- 資源復用 :通過復用FPGA內部的資源(如DSP塊、BRAM等),來減少總體資源需求。

- 動態功耗管理 :根據系統負載情況,動態調整FPGA的工作頻率和電壓,以降低功耗。

6.3 噪聲與干擾問題

在工業環境中,CCD相機可能會受到電磁干擾、光干擾等噪聲源的影響。解決方案包括:

6.4 數據傳輸與同步

數據傳輸的效率和同步性對于整個系統的實時性至關重要。在基于FPGA的CCD工業相機系統中,可能會遇到數據傳輸速率受限、同步信號不匹配等問題。以下是一些解決方案:

- 高速接口選擇 :采用高速接口標準,如Camera Link、GigE Vision或CoaXPress等,以提高數據傳輸速率。這些接口通常支持更高的帶寬和更低的延遲,能夠滿足高分辨率、高幀率圖像傳輸的需求。

- 同步信號設計 :確保FPGA與CCD傳感器、A/D轉換器以及外部設備之間的同步信號精確匹配。這包括水平同步信號(HSYNC)、垂直同步信號(VSYNC)以及像素時鐘(PCLK)等。在FPGA內部,可以通過設計專門的同步控制模塊來管理這些信號,確保它們在正確的時刻被觸發和傳遞。

- 數據緩沖與流控 :在數據傳輸過程中,使用適當的緩沖機制來平衡數據生成和數據消費之間的速率差異。這可以通過在FPGA內部實現FIFO(先進先出)緩沖器或使用外部SRAM/DDR存儲器來實現。同時,實施流量控制策略,以避免數據溢出或丟失。

- 錯誤檢測與糾正 :在數據傳輸過程中加入錯誤檢測(如CRC校驗)和糾正機制,以提高數據傳輸的可靠性。當檢測到錯誤時,可以采取重傳或數據恢復等措施來恢復正確的數據。

6.5 圖像處理算法優化

圖像處理算法的優化是提升系統性能的關鍵。在FPGA上實現圖像處理算法時,需要考慮算法的并行性、資源消耗和功耗等因素。以下是一些優化策略:

- 并行化處理 :充分利用FPGA的并行處理能力,將圖像處理算法分解為多個可并行執行的子任務。例如,在邊緣檢測算法中,可以并行計算不同像素點的梯度值。

- 流水線設計 :通過引入流水線設計來減少處理延遲并提高吞吐量。在圖像處理流水線中,每個處理階段都可以獨立運行,并且可以同時處理多個數據塊。

- 定點數運算 :為了減少資源消耗和功耗,可以考慮使用定點數運算代替浮點數運算。定點數運算在FPGA上更容易實現,并且具有更低的資源占用和功耗。

- 查找表(LUT)優化 :對于某些復雜的計算操作,如非線性變換或顏色校正,可以使用查找表來加速計算過程。通過將預計算的結果存儲在LUT中,可以在單個時鐘周期內完成復雜的計算操作。

6.6 系統集成與調試

系統集成與調試是將各個組件組合成一個完整系統并驗證其性能的過程。在基于FPGA的CCD工業相機系統中,系統集成與調試是一個復雜而關鍵的任務。以下是一些建議:

- 模塊化設計 :采用模塊化設計方法將系統劃分為多個獨立的模塊,如CCD驅動模塊、圖像處理模塊、數據傳輸模塊等。每個模塊都可以獨立進行設計和測試,從而降低整體系統的復雜性和調試難度。

- 分階段測試 :在系統集成過程中,分階段進行測試以確保每個模塊都能正常工作。首先測試單個模塊的功能和性能,然后將它們逐步集成到整個系統中進行測試。在測試過程中,使用仿真工具和測試儀器來監測信號和數據流,以便及時發現和解決問題。

- 問題定位與解決 :當系統出現問題時,采用系統分析方法來定位問題的根源。這包括查看日志文件、分析信號波形、使用調試工具進行斷點調試等。一旦找到問題所在,就采取相應的措施進行修復和優化。

- 文檔編寫與維護 :在系統開發過程中,及時編寫和維護相關文檔,包括設計文檔、測試報告、用戶手冊等。這些文檔對于系統的后期維護和升級至關重要。

七、未來發展方向

隨著技術的不斷進步和應用需求的不斷變化,基于FPGA的CCD工業相機系統也將不斷發展和完善。以下是一些可能的發展方向:

- 更高分辨率和幀率 :隨著CCD傳感器技術的不斷發展,更高分辨率和更高幀率的相機將成為可能。這將要求FPGA具有更強的處理能力和更高的數據傳輸速率來支持這些新特性。

- 智能化處理 :將人工智能和機器學習技術引入到圖像處理算法中,實現更復雜的圖像分析和識別任務。這要求FPGA具有更高的計算能力和更大的存儲空間來支持這些算法的實現。

- 多傳感器融合 :將多個不同類型的傳感器(如CCD、CMOS、紅外等)集成到一個系統中,并利用FPGA進行多傳感器數據的融合處理。這將提高系統的感知能力和魯棒性。

- 無線傳輸與遠程控制 :通過引入無線通信技術(如Wi-Fi、藍牙等),實現相機的無線傳輸和遠程控制功能。這將使相機系統更加靈活和便捷地應用于各種場景中。

- 低功耗設計 :隨著對能效要求的不斷提高,低功耗設計將成為未來發展的重要方向。通過優化算法、降低FPGA的工作頻率和電壓以及采用低功耗的硬件組件等方法來實現低功耗設計。

總之,基于FPGA的CCD工業相機系統作為現代工業檢測與成像領域的核心技術之一,其發展與進步不僅依賴于硬件技術的革新,也離不開軟件算法的優化以及系統架構的創新。以下是對該領域未來發展方向的進一步探討和展望。

相機系統作為現代工業檢測與成像領域的核心技術之一,其發展與進步不僅依賴于硬件技術的革新,也離不開軟件算法的優化以及系統架構的創新。以下是對該領域未來發展方向的進一步探討和展望。

七、未來發展方向

7.1 實時性與精準度的雙重提升

在工業應用中,對圖像處理的實時性和精準度有著極高的要求。未來的FPGA相機系統將更加注重在這兩個方面的雙重提升。通過優化FPGA的硬件架構,比如增加更多的DSP單元、優化內部互聯網絡以及采用更先進的時鐘管理技術,可以顯著提高系統的數據處理速度和效率。同時,結合先進的圖像處理算法,如深度學習算法,可以在保證處理速度的同時,進一步提升圖像識別的精準度和魯棒性。

7.2 高度集成化與模塊化設計

隨著半導體技術的不斷進步,FPGA芯片的性能和集成度將持續提升。未來的FPGA相機系統將更加注重高度集成化設計,將更多的功能模塊(如圖像傳感器、A/D轉換器、圖像處理單元、數據傳輸接口等)集成到單個FPGA芯片上,以減小系統體積、降低功耗并提高可靠性。同時,模塊化設計也將成為趨勢,允許用戶根據實際需求靈活配置系統模塊,實現定制化解決方案。

7.3 自動化校準與自適應調整

在工業環境中,環境條件的變化(如光照強度、溫度等)可能會對相機系統的性能產生影響。未來的FPGA相機系統將更加注重自動化校準和自適應調整功能。通過內置傳感器監測環境參數,并根據監測結果自動調整相機參數(如曝光時間、增益等),以確保在不同環境條件下都能獲得高質量的圖像。此外,還可以利用機器學習算法對相機進行訓練,使其能夠自動識別并適應不同的應用場景。

7.4 網絡安全與數據保護

隨著物聯網技術的普及和應用場景的不斷拓展,網絡安全和數據保護問題日益凸顯。未來的FPGA相機系統將更加注重網絡安全和數據保護設計。通過集成加密模塊、實現安全通信協議以及加強身份驗證機制等措施,可以確保相機系統在網絡傳輸過程中的數據安全性和隱私保護。同時,還需要加強對系統漏洞的監測和修復能力,以防止惡意攻擊和數據泄露。

7.5 跨平臺兼容性與可擴展性

為了滿足不同用戶和應用場景的需求,未來的FPGA相機系統將更加注重跨平臺兼容性和可擴展性設計。通過支持多種操作系統和通信協議以及提供豐富的API接口和軟件開發工具包(SDK),可以方便用戶在不同平臺上進行集成和開發。同時,還需要支持硬件升級和軟件更新功能,以便用戶能夠根據實際需求對系統進行擴展和升級。

7.6 綠色環保與可持續發展

在全球關注環保和可持續發展的背景下,未來的FPGA相機系統也將更加注重綠色環保設計。通過采用低功耗設計、使用環保材料和工藝以及優化能源利用效率等措施,可以降低系統對環境的影響并促進可持續發展。此外,還可以探索將相機系統應用于環保監測和治理等領域中,為環保事業貢獻一份力量。

綜上所述,基于FPGA的CCD工業相機系統在未來將朝著更高分辨率、更高幀率、更智能化、更集成化、更安全可靠以及更綠色環保的方向發展。隨著技術的不斷進步和應用需求的不斷拓展,我們有理由相信這一領域將迎來更加廣闊的發展前景和更加豐富的應用場景。

-

FPGA

+關注

關注

1636文章

21841瀏覽量

608494 -

機器視覺

+關注

關注

163文章

4440瀏覽量

121169 -

工業相機

+關注

關注

5文章

336瀏覽量

23983

發布評論請先 登錄

相關推薦

深圳康耐視CCD工業視覺相機高價回收

回收COGNEX康耐視 IS智能影像ID讀碼器系統 CCD工業相機回收

CCD相機的高速數據采集系統設計

基于FPGA的CCD工業相機系統設計

基于FPGA的CCD工業相機系統設計

評論