【現象描述】

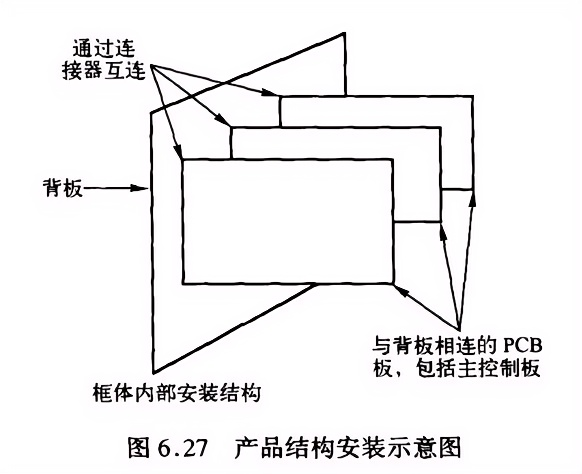

某產品采用框體背板結構,其他PCB板插在背板上通過背板進行互連,正視面的底板安裝背板PCB,其他PCB板與背板垂直連接,產品結構安裝示意圖如圖6.27所示。框體采用-48V直流供電。-48V電源信號通過背板傳送到插在框體并與背板相連的各個PCB板中。其中,主控制板是框體系統的總控制系統。

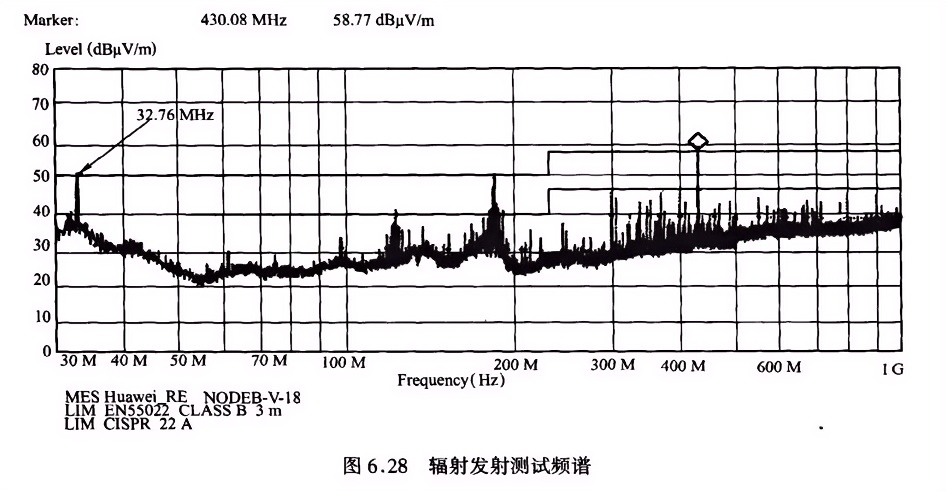

進行輻射發射測試時,發現在頻點 32.76MHz處輻射高,準峰值為53.8dBμV/m,超過 CLASS A 限值近 4 dB,如圖 6.28 所示。

在定位過程中發現,主控制板不插在槽位的時候就消失,只要主控制板一插上,無論其他PCB板如何配置,該點的輻射均存在。定位過程中還發現,如在電源線上串磁環,則該點的輻射也將消失,這說明該點是通過電源線進行輻射的,而該頻點源頭來自于主控板,耦合途徑可能在主控制板上,也有可能在背板上。

【原因分析】

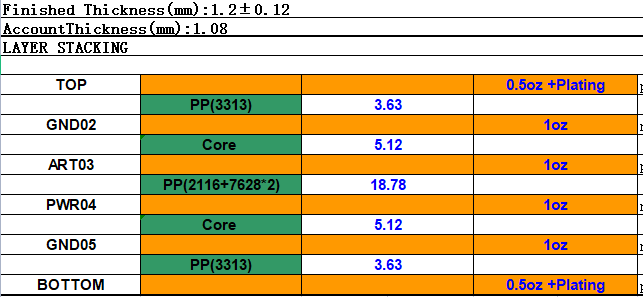

為了確定輻射源的耦合途徑,首先對框體的背板和主控制板的PCB進行詳細的檢查。

通過對背板及主控制板的PCB布線檢查,發現干擾信號耦合到電源線的途徑和原因有以下幾種可能:

(1)背板上主控制板槽位的時鐘走線離框體供電電源-48V地較近,同時與背板DGND的隔離距離為50mil,可能會耦合到電源線。

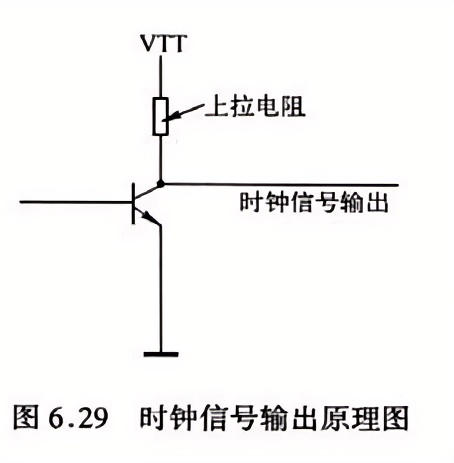

(2)時鐘線走線是采用兩端匹配的方式,通過上拉電阻匹配到VTT電源層。時鐘信號輸出原理圖如圖6.29所示。

如果VTT濾波電容選擇的不合理,則可能會將干擾傳人VTT層,而VTT層與-48V電源層在主控制板上有較大面積的重合,-48V電源層很有可能被耦合到干擾。

經過以上的初步分析,可按以下步驟定位測試:

步驟一

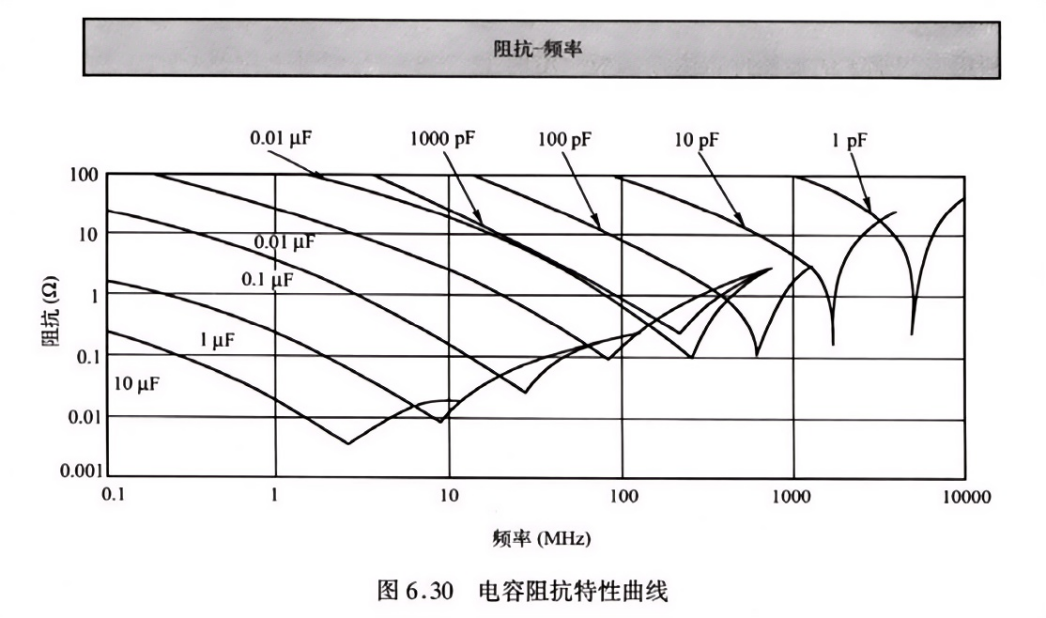

優化框體背板的時鐘匹配電阻的濾波電容,改為0.1μF和0.022μF。

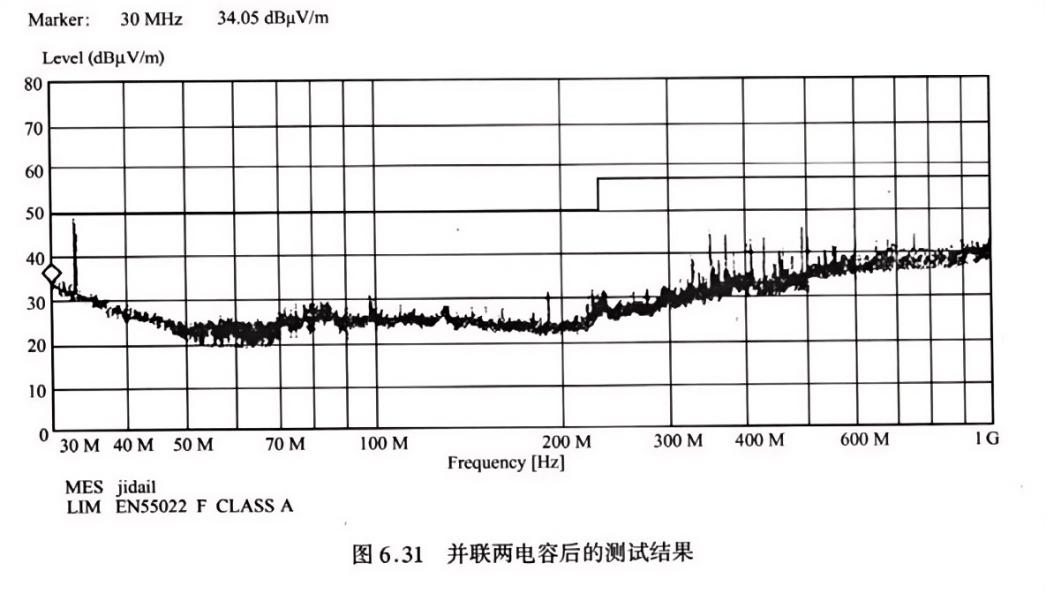

由圖6.30所示的電容阻抗特性曲線可知,兩電容并聯后的濾波范圍在幾十MHz之間。修改完后,再進行測試,并聯兩電容后的測試結果如圖6.31所示。

圖6.31中的測試結果與以前的測試結果相比有改善,說明于擾與VIT電源層有關,但是耦合發生在背板還是主控制板,需要進一步定位。

步驟二

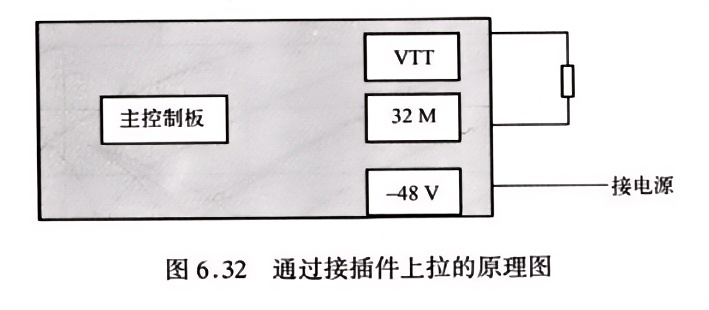

利用專門加工的接插件將主控制板輸出的32.768MHz時鐘上拉到VTT,然后啟動主控制板,通過接插件上拉的原理圖如圖6.32所示。

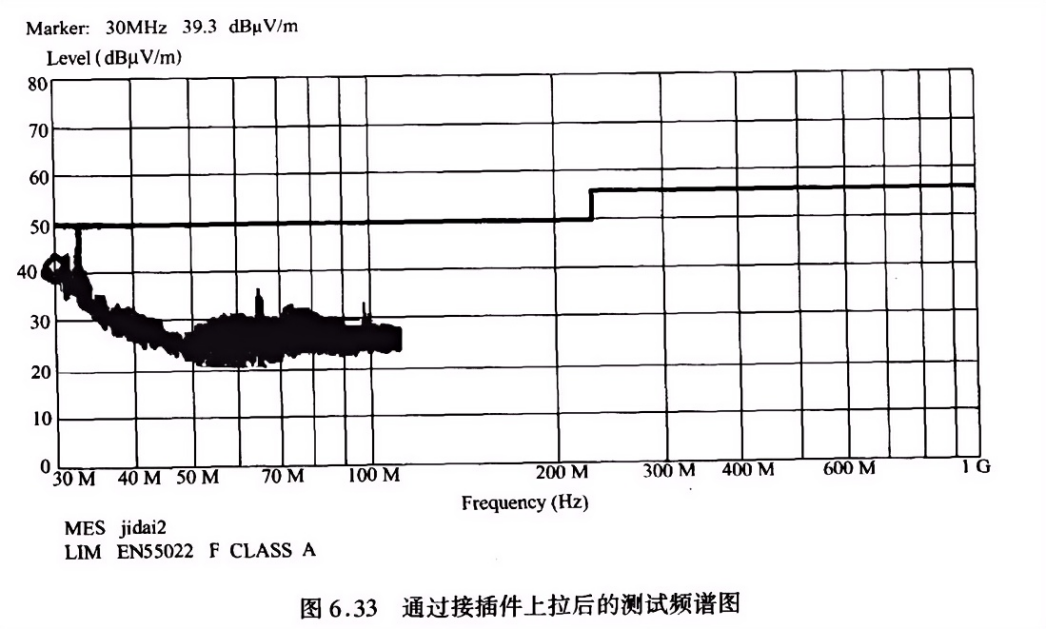

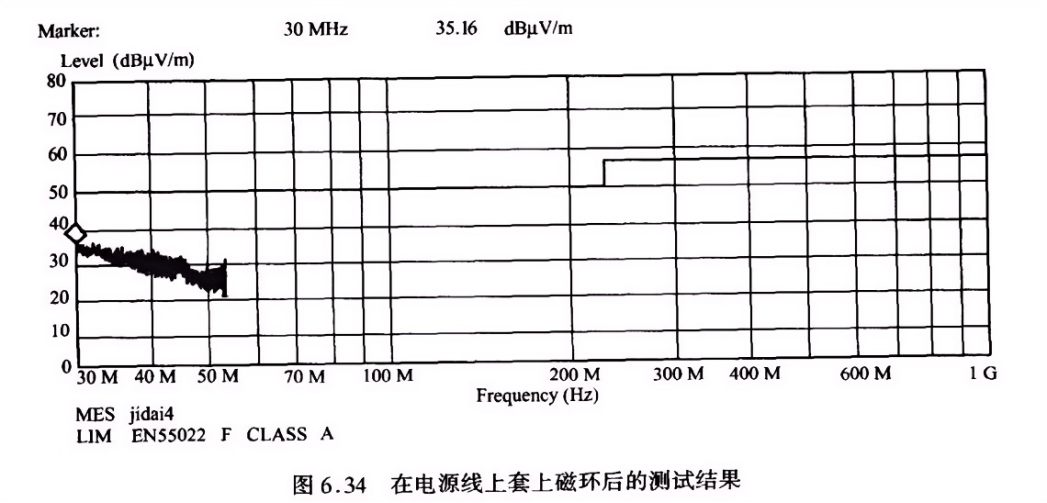

通過接插件上拉后再進行測試,結果如圖6.33所示。

再在電源線上套上磁環后進行測試,得到如圖6.34所示的結果。

到此為止,基本上可以說明問題出在主控制板上,而不是背板上,是主控板內部存在耦合。需要進一步定位的是,耦合是由時鐘線直接引起的還是由VTT電源層引起的。

步驟三

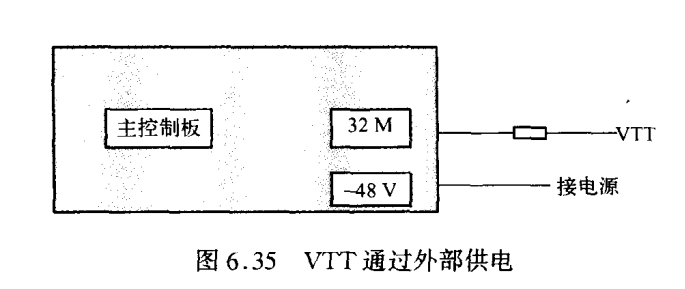

對主控制板進行處理,關斷主控板的VTT電源,VTT通過外部線性電源供電,然后連接,如圖 6.35 所示。

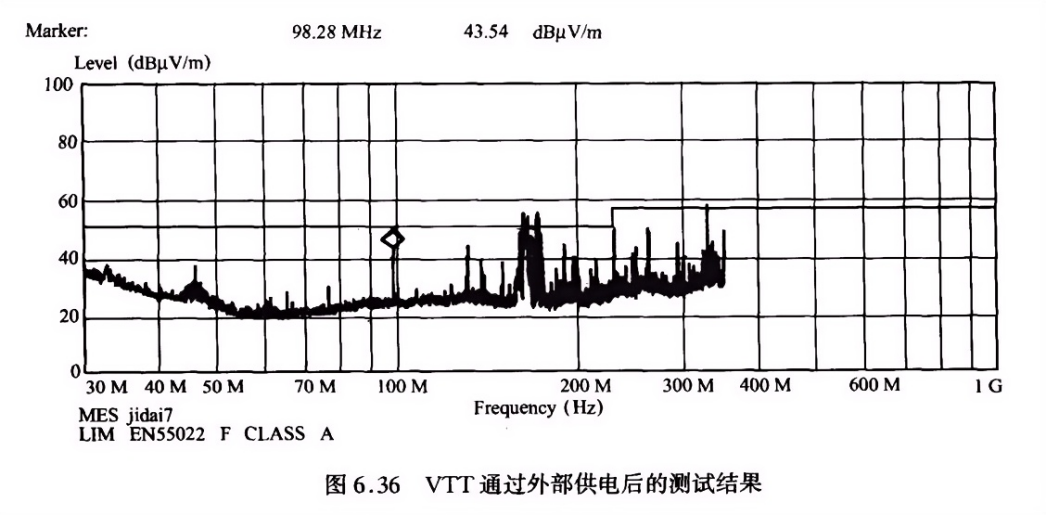

啟動主控制板后再進行輻射測試,得到如圖6.36所示的結果。

32.768 MHz時鐘輻射基本消失,說明并不是由時鐘線直接耦合到-48V電源層導致的輻射超標,而是由時鐘信號的VTT電源層受到時鐘信號的影響后對-48V電源層耦合造成的。

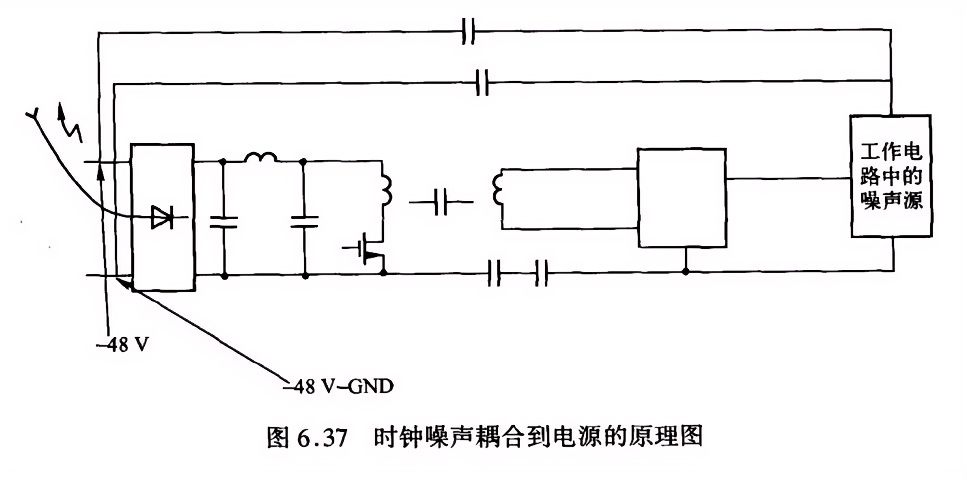

試驗證明,32.768 MHz時鐘的輻射是主控制板內通過VTT耦合到-48V電源層后,再對主控制板進行審查,發現VTT電源層與-48V、-48-GND的電源平面有大面積的重合,這樣 VTT中的時鐘噪聲通過容性耦合的方式耦合到-48V、-48-GND的線上,而與-48 V、-48-GND直接相連的框體供電電源線成為了很好的發射天線。時鐘噪聲耦合到電源的原理圖如圖 6.37 所示。

【處理措施】

(1) 改變主控制板的電源層VTT的電源平面分布,避開-48V電源平面,使得-48V電源平面所在的區域除-48V電源及其地平面外無其他任何平面。

(2) 優化VTT電源去耦電容為0.1μF和0.022μF。

【思考與啟示】

(1) PCB板的人口供電電源及其相關電路應與PCB板中其他的電路做好良好的隔離與去耦,使電源信號相對獨立,以免PCB中的信號合到電源信號中。

(2) 對于隔離電源,既要做好電平線的隔離,也要做好“0V”線的隔離。

-

pcb

+關注

關注

4370文章

23511瀏覽量

410234 -

PCB板

+關注

關注

27文章

1474瀏覽量

53538 -

耦合

+關注

關注

13文章

596瀏覽量

101698 -

鋪地

+關注

關注

0文章

3瀏覽量

2079

發布評論請先 登錄

PCB中鋪銅作用

解惑高級PCB-EMC問題

PCB中鋪銅作用分析

PCB中鋪銅的好處有哪些

為什么這十個PCB設計錯誤要避免資料下載

PCB中鋪銅的好處有哪些?資料下載

評論