1. 介紹

差分時鐘被廣泛用于實現(xiàn)高速、耐噪聲的時鐘傳輸。鐘表制造商包括愛普生在內的公司提供各種格式的差分時鐘產品,有必要做出適當?shù)母鶕?jù)系統(tǒng)要求進行選擇。愛普生提供三種差分時鐘產品標準格式:LV-PECL、LVDS和HCSL,現(xiàn)在我們新增了專有的寬振幅LVDS或WA-LVDS加入產品陣容。本技術說明解釋了這四個差分時鐘的特性。

2.差分時鐘概述

① LV-PECL

LV-PECL代表“低壓正發(fā)射極耦合邏輯”。正如你從“發(fā)射器”一詞中看到的,它是一個由雙極晶體管組成的輸出驅動器。由于ECL(LV-PECL的詞根)需要負電源,因此添加了“正”一詞來強調驅動器使用正電源運行。在一款電源電壓為3.3V的產品問世后,又增加了“低壓”一詞。如今,由于可在3.3V或更低電壓下工作的產品變得相當普遍,“LV-”經常被省略。

LV-PECL適用于高速操作,因為輸出晶體管在不關斷的情況下工作,如稍后所述。此外,由于振幅相對較大,因此具有低相位噪聲特征,以及出色的抗噪性。

② LVDS

LVDS代表“低壓差分信號”。顧名思義,LVDS的特點是低振幅操作。LVDS最初主要由美國國家半導體公司(后來被德州儀器公司收購)開發(fā)。它于1994年由ANSI/TIA/EIA標準化,目前用于許多電子設備。

最常見的振幅水平為0.35 V(典型值)。通過保持低振幅,實現(xiàn)了低驅動器電流的高速操作。低電流消耗是LVDS的主要優(yōu)勢。然而,由于振幅低,其相位噪聲趨于惡化。此外,必須注意的是,接收器需要相當大的功率才能將振幅擴展到所需的水平,在此過程中相位噪聲可能會降低。

③ HCSL

HCSL代表“高速電流轉向邏輯”。該名稱來源于電流輸出路徑在正負輸出端子之間交替控制的電路結構。這種方法是在PCI Express標準中提出的,至今仍然是一種主要的應用。調整愛普生提供的HCSL驅動器的輸出波形,使邊緣速率適當或不太陡峭。這是因為用于PCI Express的時鐘頻率通常為100 MHz,并且需要為該頻率擬合邊緣速率。因此,盡管幅度水平幾乎與LV-PECL相同,但相位噪聲與之相比有些不利。

④ WA-LVDS

近年來,ASIC和SOC上的時鐘接收器越來越定制化,因此上述標準差分時鐘并不總是合適的。因此,愛普生最近發(fā)布了寬振幅LVDS(WA-LVDS),以提供具有卓越性能和靈活性的差分時鐘。

WA-LVDS保持了LVDS負載連接的簡單性,并為偏移電壓和信號幅度提供了靈活性。偏移電壓電平和幅度可以分別從四個電平和十個電平中選擇(細節(jié)將在后面描述)。因此,在許多情況下,您可以將時鐘直接連接到LSI,而不需要額外的組件。當然,與電容器的交流耦合也是可能的。如果選擇大振幅,電流消耗會增加,但預期相位噪聲會降低。WA-LVDS適用于低功耗和低噪聲的兩種系統(tǒng)。WA-LVDS的另一個優(yōu)點是它比LVDS具有更高的PSNR(電源噪聲抑制)性能。

3.差分時鐘的分類

雖然它沒有得到廣泛認可,但差分時鐘大致分為兩種類型:電流輸出型和電壓輸出型。電流輸出類型通過使指定電流通過負載電阻器來獲得所需的輸出幅度。因此,振幅也取決于負載電阻的精度。另一方面,電壓輸出型直接向負載輸出指定的電壓。振幅與負載電阻的精度關系不大。

此外,當從流過負載電阻的電流的角度進行分類時,電流可分為兩種類型:純交流和交流+直流。不可避免地,包含直流組件的時鐘驅動器需要過大的電流消耗。

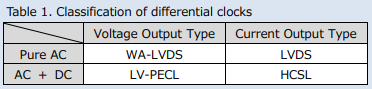

基于這些組合,差分時鐘可分為四種類型,如表1所示。新開發(fā)的WA-LVDS是一種電壓輸出型,流經負載電阻的電流是純交流電。這正是差分時鐘的理想組合。

注1:一些產品具有LV-PECL作為電流輸出類型的偽實現(xiàn)。

注2:Renesas(前身為IDT)專有的LP-HCSL(低功耗HCSL)是一種HCSL,但它屬于與LV-PECL相同的分類。

4.輸出電壓和電流

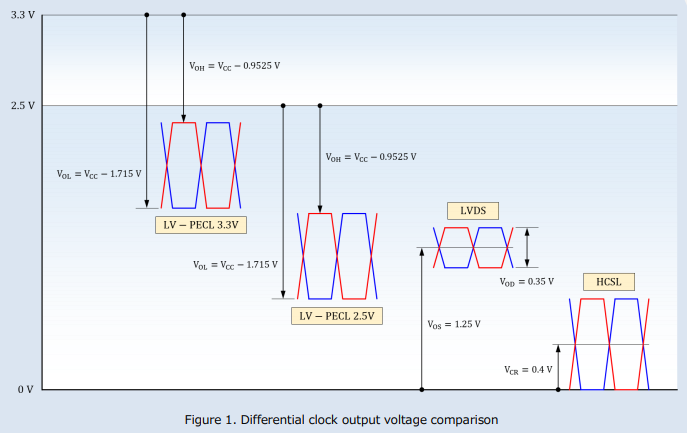

讓我們看看現(xiàn)有三種時鐘(即LV-PECL、LVDS、HCSL)的輸出電壓差異。請參考圖1。

最獨特的可能是LV-PECL。LV-PECL的輸出電壓相對于電源電壓VCC來定義。因此,輸出電壓值根據(jù)電源電壓而變化。H電平輸出電壓VOH和L電平輸出電壓VOL的規(guī)格如圖所示。無論VCC如何,差分幅度均為0.7625 V(典型值)。

對于LVDS,偏移電壓VOS被指定為1.25V,并且與電源電壓無關。差分幅度VOD為0.35V,這是三種方法中明顯最小的值。

最后一個是HCSL,其特征是L電平為0V。規(guī)范通常確定差分交叉點電壓VCR為0.4V。關于H電平通常沒有明確的規(guī)定。但不可避免的是,它的設計在0.8 V左右。因此,振幅水平與LV-PECL大致相同。

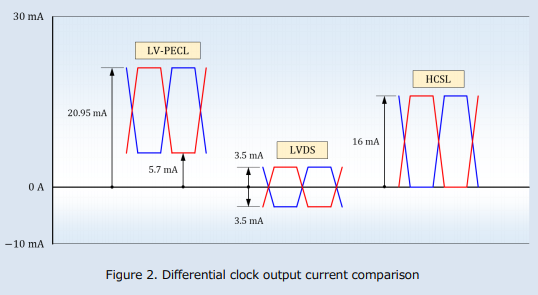

接下來,讓我們看看輸出電流。這里的輸出電流是指從驅動器的輸出端子流向負載(或從負載流入)的電流,形成圖1所示的輸出電壓。請參考圖2。

如上所述,LV-PECL的輸出電壓取決于電源電壓,但輸出電流為與電源電壓無關。這是因為終端參考電壓也根據(jù)電源電壓而變化。即使輸出L電平,LV-PECL驅動器也需要提供5.7mA。這是LV-PECL在電流消耗方面的一個主要缺點。

LVDS的獨特之處在于輸出電流是純交流電,因此不需要多余的電流。此外,由于峰值輸出電流限制在3.5mA的小值,LVDS適用于低功耗應用。LVDS的純交流電流輸出還可以將時鐘信號與電容器進行交流耦合。

HCSL在輸出L電平時不輸出電流。因此,即使輸出電壓幅度為與LV-PECL相比輸出電流要低得多。

5.電路操作和端接方法

接下來,讓我們詳細解釋每種類型的電路操作以及如何連接負載。

① LV-PECL

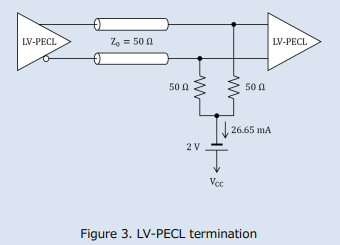

LV-PECL的典型端接方法如圖3所示。規(guī)定50Ω端子必須連接到VCC?2 V,而不是接地。由于電勢VCC?2 V必須由用戶創(chuàng)建,因此時鐘接收電路會有點復雜。

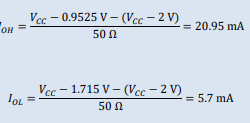

流過H和L電平輸出負載的電流(如圖2所示)分別計算如下

從上述公式可以理解,從輸出端子輸出的電流總計為26.65mA。

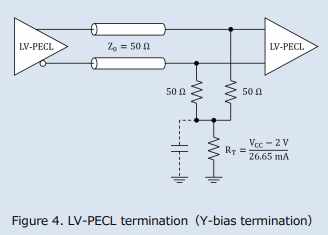

僅為此終端提供VCC?2 V的恒壓源是不切實際的。因此,通常采用另一種方法。圖4顯示了所謂的Y偏置終止,這是一種方法,其中26.65 mA的電流流過電阻器,產生相當于VCC?2 V的電壓。電阻值RT必須根據(jù)圖中所示的VCC設置。如果VCC=3.3 V,RT=49Ω;或者如果VCC=2.5V,RT=19Ω。電容器可以與RT并聯(lián)連接,使終端節(jié)點更理想地作為交流地。

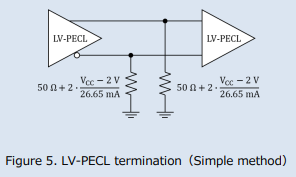

圖5顯示了另一種方法。電阻器RT被分為兩個等效電阻器(2RT),每個電阻器都與一個負載電阻器(50Ω)集成在一起,從而減少了對兩個電阻器的需求。如果VCC=3.3V,電阻值為148Ω,如果VCC=2.5V,電阻值為88Ω。總輸出電流將與圖4相同,但從每個輸出端子流出的電流值不同,這將導致電壓值略有偏差。此外,由于電路沒有端接至50Ω的交流地線,因此該端接不能應用于傳輸線的末端。只有當時鐘驅動器和接收器電路放置在附近時,它才適用。此外,請注意,愛普生不保證使用這種終止方法的時鐘特性。

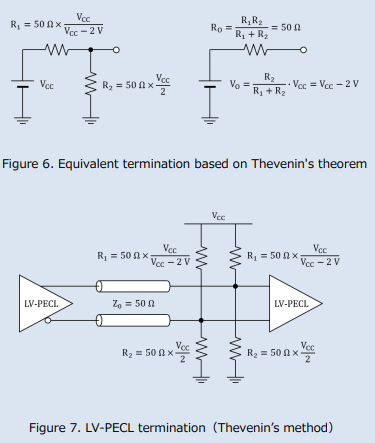

最后,我們將介紹一種名為Thevenin終止的技術。這需要四個電阻器,但最簡單。如圖6的左圖所示,假設電壓VCC被兩個電阻器R1和R2分壓,中點節(jié)點被取出。如果我們用戴維南定理變換這個電路,我們將得到右邊的等效電路。可以看出,在節(jié)點處等效地產生了VCC-2 V和50Ω。將此電路應用于圖3中的負載電路,結果如圖7所示。這就是所謂的戴維南終止。使用此技術時,VCC電源的輸出阻抗必須相對于R1的值保持足夠低。此外,您需要小心VCC中的噪聲,因為它可能會降低時鐘質量。

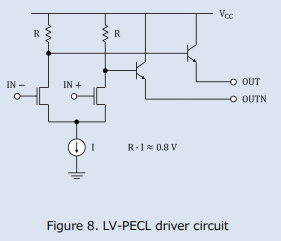

接下來,讓我們檢查圖8所示的LV-PECL驅動器的內部電路配置。輸出級是具有公共集電極的開放發(fā)射極配置。這是一種通常被稱為“發(fā)射極跟隨器”的電路,因為發(fā)射極電勢會隨著基極電勢而變化。通過用MOS晶體管切換恒流“I”,VCC或VCC-0.8V交替施加到雙極晶體管的基極端子。

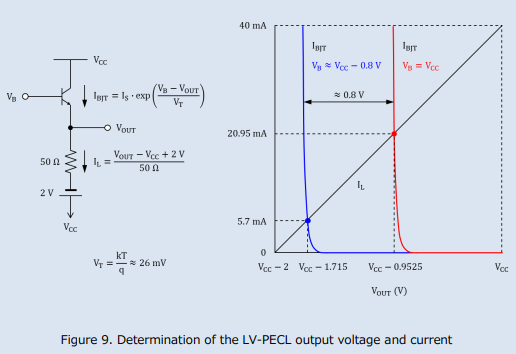

圖9展示了如何確定LV-PECL的輸出電壓和電流。通過雙極晶體管的電流IBJT和通過負載電阻器的電流IL使用輸出電壓VOUT作為參數(shù)表示。輸出電壓和電流在兩者相互平衡的點上確定。

如果基極電壓VB等于VCC,則IBJT將是圖上的紅線。當VOUT為VCC?0.9525 V時,IBJT和IL必須平衡,并且根據(jù)LV-PECL規(guī)范,該點的電流值必須為20.95 mA。為了滿足這些特性,調整雙極晶體管的尺寸。當該晶體管的基極電壓降至VCC-0.8V時,IBJT會跟隨一條藍線。在這種情況下,當VOUT為VCC-1.715V時,IBJT和IL是平衡的,此時的電流值為5.7mA。這樣,就滿足了LV-PECL的L電平規(guī)格。

如果負載電阻偏離50Ω,IL圖(黑線)的斜率將增加或減小。但是,您可以理解,即使在這種情況下,輸出電壓的變化量也很小。從這個特征可以說LV-PECL是一種電壓輸出型驅動器。請注意,最近愛普生的LV-PECL驅動器使用MOS晶體管而不是雙極晶體管。在這種情況下,實現(xiàn)了與圖8中略有不同的獨特電路配置,但這里將省略其說明。

順便說一句,你可能會覺得奇怪,VOH和VOL被指定為小數(shù)點后3到4位的非常詳細的數(shù)字。這可能是因為規(guī)格被設置為模仿首次發(fā)布的產品的特性。實際上,這些數(shù)字因制造商和產品而異,因此請在選擇產品時查看數(shù)據(jù)表。

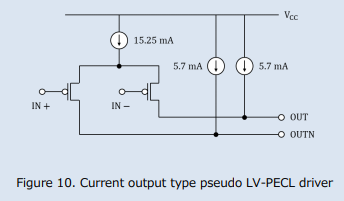

一些LV-PECL驅動器使用電流輸出型電路,如圖10所示。如果負載為50Ω,則可以獲得與電壓型相同的結果,但圖5所示的簡單端接方法不能應用于這種類型的驅動器。這種電路的缺點是,與射極跟隨器電路相比,它往往更容易受到寄生電感的影響。因此,振鈴可能會疊加在時鐘波形上。愛普生過去在一些SAW振蕩器中使用這種電路,但現(xiàn)在所有的LV-PECL都統(tǒng)一為電壓輸出型。

② LVDS

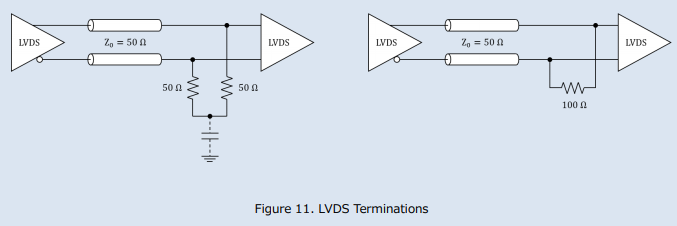

LVDS端接方法如圖11所示。由于LVDS的輸出電流是純交流電,因此50Ω負載連接到浮動節(jié)點,如左圖所示。該節(jié)點恒定在1.25V,因此被認為是交流接地。1.25V電壓由驅動器設置,因此不需要在接收器側提供偏置電壓。您還可以在端接節(jié)點連接一個電容器,使交流接地更加理想。這也可能有效地消除共模噪聲。但在通常情況下,這是不必要的。在許多情況下,兩個50Ω電阻器可以用一個100Ω電阻器代替,以創(chuàng)建差分100Ω終端,如右圖所示。

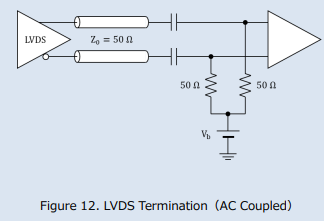

由于LVDS的輸出電流是純交流,因此可以與交流耦合電容器一起使用,如圖12所示。電容器可以插入傳輸線的發(fā)射側或接收側。在這種情況下,您需要在接收側準備偏置電壓Vb。Vb的值可以根據(jù)接收電路的規(guī)格任意設置。Vb需要是一個足夠低的阻抗電壓源,以保證50Ω的端接,或者相反,需要足夠高的阻抗,以保證100Ω的差分端接。您還可以使用圖7所示的Thevenin終端。

請注意,如果時鐘占空比偏離50%,輸出電流中會出現(xiàn)直流分量。在這種情況下,電荷可能會積聚在交流耦合電容器中,導致波形變化。變化程度取決于產品的電路設計,因此請在使用前仔細檢查。

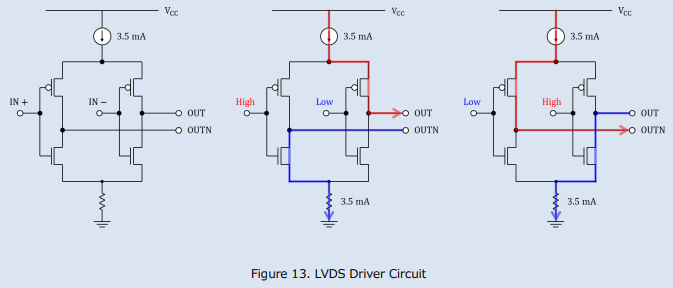

圖13顯示了LVDS驅動器的內部電路配置。它由一個3.5mA的恒流源、四個MOS開關和一個使用有源元件的可變電阻器組成。圖13中的中心和右側數(shù)字顯示了電流路徑的切換操作。通過在這兩種狀態(tài)之間交替,交流電流流過負載。

3.5mA的恒定電流始終流過電阻器,因此可以通過改變其電阻來調節(jié)偏移電壓VOS。LVDS驅動器具有CMFB(共模反饋)電路,其功能是將VOS保持在1.25 V。有三種類型的CMFB電路:一種監(jiān)測實際輸出波形,一種從IC內驅動器電路的副本估計VOS,以及兩者的混合類型。

③ HCSL

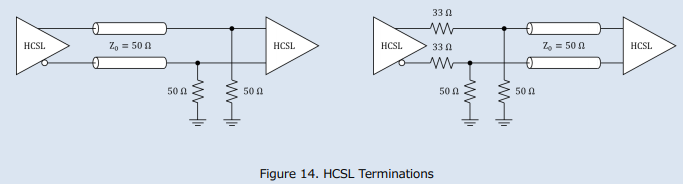

HCSL終止方法如圖14所示。圖的左側顯示了接收側端接的示例。這是一種簡單、易于理解、問題較少的終止方法。高電平輸出側的負載由HCSL驅動器提供16mA的電流,產生0.8V的幅度。低電平輸出側負載的電流供應被切斷,電壓變?yōu)榈仉娖健?/p>

PCI Express標準中規(guī)定了另一種端接方法,如圖14右側所示。驅動器側提供端接電阻器,驅動器的電流輸出分為兩個方向:50Ω負載和接收電路。在接收器端,波形被全反射,因此振幅加倍,形成振幅為0.8V的波形。反射波形被50Ω吸收,但由于連接了HCSL驅動器,阻抗略低于50Ω。為了使驅動器在節(jié)點上不那么顯眼,在驅動器的輸出端插入了33Ω電阻器。然而,即使采用這種方法,也很難確保完美的阻抗匹配。因此,一些波形將在驅動器側重新反射。因此,接收器端子處的波形根據(jù)傳輸線的電長度而變化。你必須在設計電路時考慮到這種行為。波形可以通過以下方式進行模擬時鐘制造商提供的IBIS型號。

圖14中的端子基于差分100Ω傳輸,但也可以使用差分85Ω。這樣做的目的是通過縮小傳輸線之間的間距來減小電路板的尺寸,或者減小板的厚度。在這種情況下,電阻必須為42.5Ω而不是50Ω,27Ω而不是33Ω。由于必須保持電壓振幅,因此需要輸出電流的(100/85)倍。

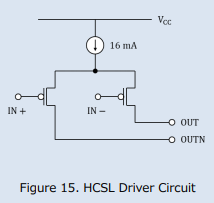

圖15顯示了HCSL驅動器的內部電路配置。它具有簡單的配置,其中16mA的恒定電流通過MOS開關交替施加到兩個輸出端子。該電路與圖10中的電路非常相似,去掉了無用的5.7mA恒流源。

恒流源的交流阻抗理想情況下為∞,MOS開關的交流阻抗理論上為0(處于導通狀態(tài))或∞(處于關斷狀態(tài)),因此即使在圖14右側所示的連接情況下,HCSL驅動器基本上也不會導致阻抗失配。然而,寄生電容等因素會破壞理想狀態(tài),因此阻抗失配在實際中是不可避免的。

④ WA-LVDS

WA-LVDS的端接方法與LVDS相同,請參考圖11或圖12。在LVDS具有AC耦合負載的情況下,如果占空比偏離50%,則會產生DC電流,并且擔心電荷會積聚在電容器中。由于WA-LVDS是一種電壓輸出型,其優(yōu)點是此類問題較少。

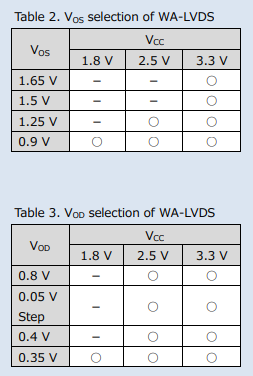

使用LVDS時,偏移電壓(VOS)固定為1.25 V,差分輸出電壓(VOD)固定為0.35 V,但使用WA-LVDS時,您可以分別從4個電平和5個電平中進行選擇,如下表所示。可選值取決于電源電壓VCC。交流耦合時,選擇一個接近VCC/2的VOS值。

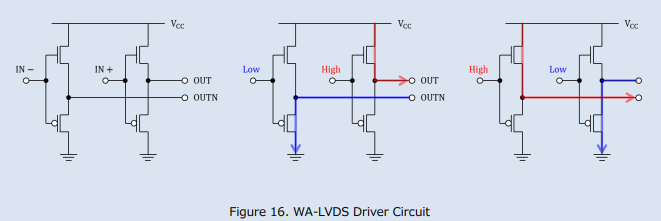

圖16顯示了WA-LVDS驅動器的內部電路配置。N型MOS晶體管連接到VCC側,P型MOS晶體管接地側,源極端子連接到輸出端。這是一種稱為源極跟隨器電路的配置,類似于LV-PECL的發(fā)射極跟隨器。輸出電壓電平取決于輸入到柵極端子的IN+和IN-的電勢。實現(xiàn)了一種獨特的電路來控制輸入幅度電勢,以滿足所需的VOS和VOD。電流路徑切換操作如圖16的中心和右側圖所示。它的行為類似于LVDS。

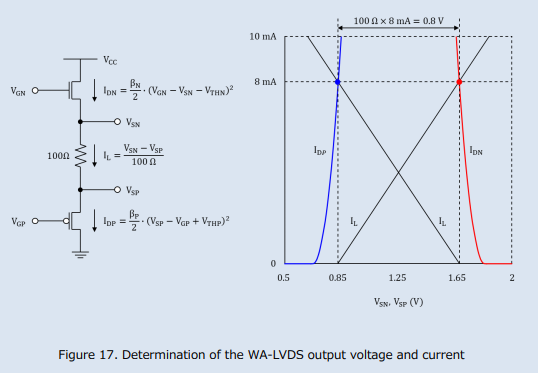

參考圖17,讓我們看看WA-LVDS輸出電壓和電流是如何確定的。他們是由流過N型MOS晶體管的電流IDN、流過100Ω負載電阻的電流IL和流過P型MOS晶體管中的電流IDP之間的平衡決定。

圖17中的圖表顯示了輸出VOS=1.25V和VOD=0.8V波形的狀態(tài)。IDN和IDP由每個MOS晶體管的柵源電壓決定。當電源電壓改變時,所有電流值都會改變。假設VSN和VSP將流過IDN和IDP的相同電流(圖中為8mA)。如果VSN和VSP之間的差值是電流值的100倍(圖中為0.8V),則IL也將具有相同的電流值,電路將處于平衡狀態(tài)。

通過適當?shù)卣{整MOS晶體管VGN和VGP的柵極電壓,可以任意設置上述平衡點,從而可以滿足所需的偏移電壓VOS和差分輸出電壓VOD。WA-LVDS驅動器IC中實現(xiàn)了用于此目的的內部調整機制。

6.輸出幅度、輸出電流和抖動之間的相關性

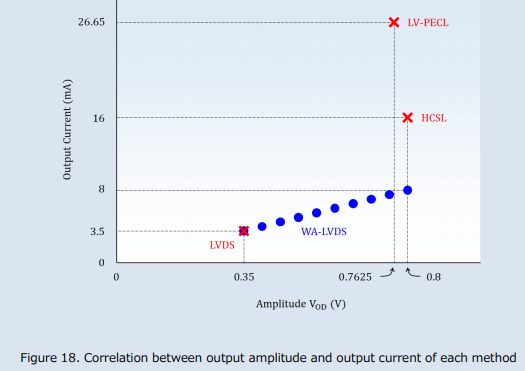

讓我們比較一下上述四種方法的輸出幅度和輸出電流之間的相關性。請參見圖18。

WA-LVDS(藍色●)有10個圖,因為差分輸出電壓VOD可以在10個步驟中切換。波形形成方法與LVDS相同,因此當VOD為0.35V時,它與LVDS匹配。每次振幅增加時,電流都會增加,但即使VOD為0.8V,輸出電流也會保持在8mA。這是因為輸出電流是純交流電。

相比之下,即使振幅在0.8 V時相同,HCSL也需要兩倍的電流,即16 mA。LV-PECL需要26.65 mA的電流,即使其振幅稍小。通過這樣的比較,你可以看到WA-LVDS的效率有多高。

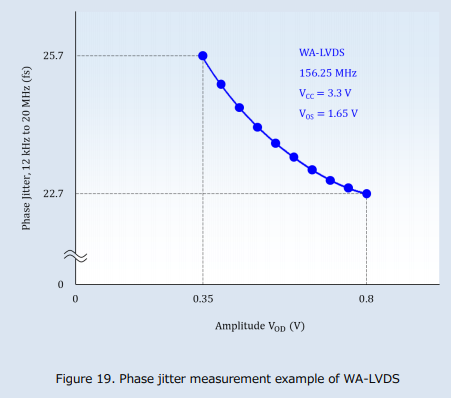

WA-LVDS測量的相位抖動示例如圖19所示。可以清楚地看到,相位抖動隨著差分幅度VOD的增加而減小。因此,如果電路的電流消耗不受限制,更高的差分幅度VOD是獲得更高電路性能的更好選擇

7.結論

我們解釋了LV-PECL、LVDS和HCSL三種驅動器的特點和使用方法,以及新開發(fā)的WA-LVDS。愛普生計劃在未來擴大WA-LVDS產品線。如果您對本技術說明的內容有任何疑問,請根據(jù)以下信息與我們聯(lián)系。

-

驅動器

+關注

關注

52文章

8226瀏覽量

146253 -

終端

+關注

關注

1文章

1128瀏覽量

29865 -

差分時鐘

+關注

關注

0文章

10瀏覽量

4541

發(fā)布評論請先 登錄

相關推薦

快速評估NB7L32M GigaComm時鐘驅動器的評估板NB7L32MMNGEVB

如何理解時鐘驅動器的抖動參數(shù)?

安森美推出NB7L585等多款時鐘驅動器,支持不同的接口選擇

可編程低電壓1:10 LVDS時鐘驅動器ADN4670

CDCVF2505-Q1時鐘鎖相環(huán)時鐘驅動器數(shù)據(jù)表

CDCVF2505時鐘鎖相環(huán)時鐘驅動器數(shù)據(jù)表

CDCVF111 1:9差分LVPECL時鐘驅動器數(shù)據(jù)表

CDCV855,CDCV855I時鐘驅動器數(shù)據(jù)表

CDCLVP110帶可選輸入時鐘驅動器數(shù)據(jù)表

CDC111差分LVPECL時鐘驅動器數(shù)據(jù)表

CDC203反相器/時鐘驅動器數(shù)據(jù)表

SSQEA32882差分時鐘PLL驅動器數(shù)據(jù)表

差分時鐘驅動器和終端

差分時鐘驅動器和終端

評論