今天我們來聊聊在計算機領域中非常關鍵的技術——DRAM(動態隨機存取存儲器)的內部結構和工作原理。

DRAM Arrays的基本結構

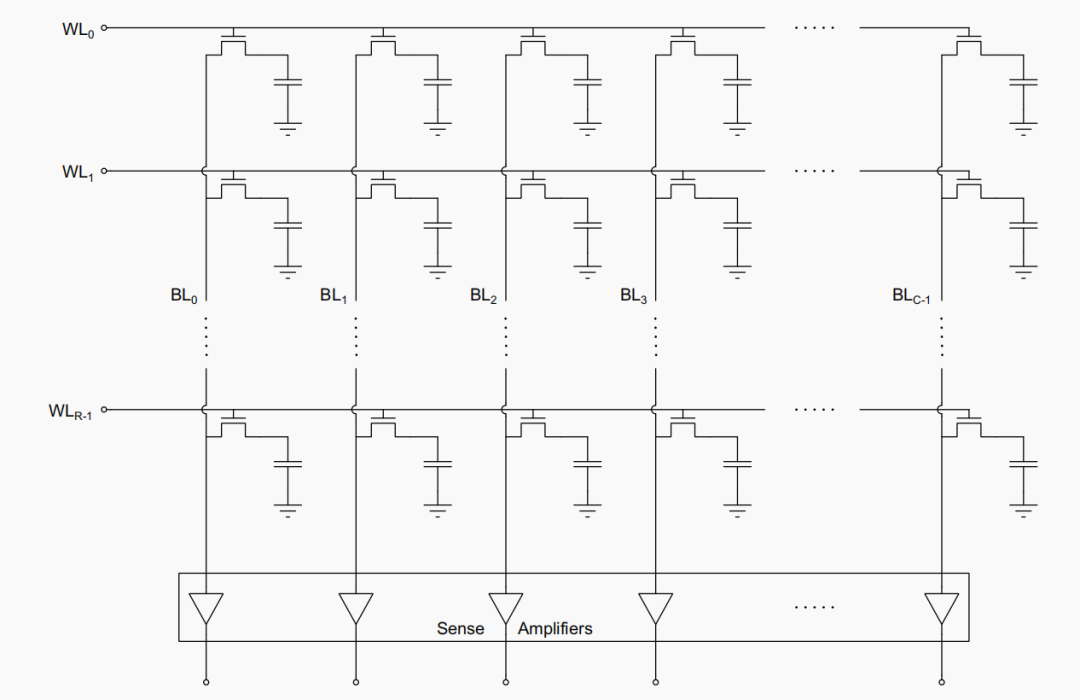

首先,DRAM通常被組織成一個矩形的存儲單元陣列,這些存儲單元按照行和列的方式排列。想象一下,就像一個巨大的表格,每個單元格都是一個存儲cell。下圖展示了一個簡化的基本DRAM cell arrays結構,其中包含R行和C列的cell。一個典型的DRAM array可能會包含數百甚至數千個這樣的cell。

訪問DRAM cell

這些cell是如何被訪問的呢?答案是通過行地址和列地址。行地址線(也就是我們常說的字線)連接到nMOS晶體管的柵極,而列線則連接到靈敏放大器。這種設計使得我們可以通過特定的行和列地址來定位并訪問任何一個DRAM cell。

arrays大小的權衡

然而,arrays的大小并不是越大越好。更大的arrays雖然可以存儲更多的信息,但它們也需要更長的字線和位線。更長的字線和位線意味著更高的電容,這會帶來一些問題。首先,電容的增加會使得位線上的電壓擺動在讀取時變得非常微小,這使得檢測變得困難。其次,更高的電容也意味著更大的arrays在操作時會更慢。

典型DRAM arrays的大小

在現代DRAM中,一個典型的arrays大小是8K字(行)乘以1024位(列)。這意味著每個DRAM芯片可以存儲8192個數據單元,每個單元可以存儲1024位數據。

DRAM banks的概念

你可能還聽說過DRAM Banks。一個DRAM Banks通常包含4到16個DRAM arrays,這些arrays可以同時被訪問。因此,每當內存控制器訪問DRAM時,DRAM芯片會傳輸或接收與arrays數量相等的位數。每個array提供一個位到輸出引腳。DRAM芯片被描述為xN,其中N指的是內存array和輸出引腳的數量。例如,一個x8 DRAM表示DRAM至少有八個內存array,這意味著每次內存控制器訪問DRAM時,DRAM會傳輸或接收8位。

-

DRAM

+關注

關注

40文章

2311瀏覽量

183447 -

存儲器

+關注

關注

38文章

7484瀏覽量

163765 -

計算機

+關注

關注

19文章

7488瀏覽量

87852

原文標題:深入理解DRAM Arrays與Banks

文章出處:【微信號:數字芯片實驗室,微信公眾號:數字芯片實驗室】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

ldo內部結構和工作原理

CS5463內部結構和引腳功能分別是什么? CS5463的工作原理分為哪幾部分?

TEA1504的內部結構及工作原理

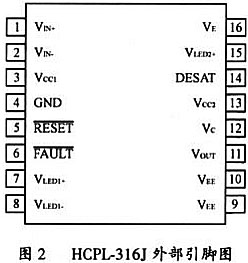

HCPL-316J內部結構及工作原理

mcs-51單片機CPU的內部結構及工作原理

ldo內部結構和工作原理

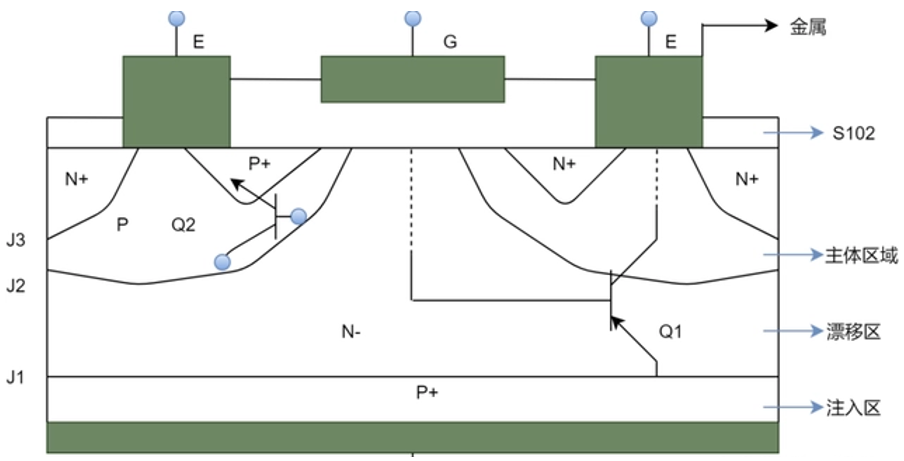

igbt內部結構及工作原理分析

DRAM的內部結構和工作原理

DRAM的內部結構和工作原理

評論